日前,由中國科學院EDA中心承接的高性能IP模塊研制課題,在陳嵐研究員和吳玉平研究員的帶領下,研究小組成員克服時間緊、任務重等困難,在基于SiGe工藝下的射頻IP關鍵核心模塊的研制工作取得了重要進展,并獲得了上海華虹NEC電子有限公司的高度認可。

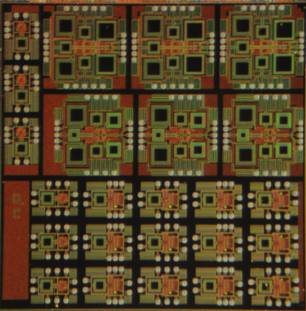

圖1 射頻IP模塊的芯片照片

高性能IP研究小組使用華虹NEC已有SiGe工藝,對部分射頻IP模塊進行了設計工作。通過電路仿真、版圖設計、流片和測試,驗證了所設計的射頻模塊符合預期的設計要求,并為0.18/0.13um SiGe HBT工藝平臺的研發提供了可借鑒的經驗。

圖2 部分射頻模塊的測試結果

自從華虹NEC的0.13um SiGe HBT平臺開放后,高性能IP研究小組又立即針對該平臺進行了部分射頻IP的設計工作,目前已進入制版階段,并將很快進行流片驗證。在整個項目的合作中,高性能IP研究小組主動與華虹NEC進行全面的探討和交流,推進了該項目的順利進行,并獲得了華虹NEC的高度認可。

粵公網安備 44030902003195號

粵公網安備 44030902003195號