PCIe 6之后,敢問路在何方

作者:泰克科技 David Bouse

PCIe Express® 物理層先從 Gen 4.0 飛速發(fā)展到了 Gen 5.0,最后升級至 Gen 6.0,且 6.0 規(guī)范包含了開發(fā)硅芯片所需的一切。數(shù)據(jù)傳輸速率從 16 Gt/s 提升到 32 GT/s,Gen 6.0 更是增加到了 64 GT/s(每秒千兆傳輸速率)。而且,首次采用了PAM4多級信號調(diào)制技術(shù),允許我們在單個(gè)單位時(shí)間內(nèi)編碼兩位信息。借此,我們將 Gen 5.0 的數(shù)據(jù)傳輸速率增加了一倍。

在今年的泰克創(chuàng)新論壇上,我有幸參加了一場小組討論,與我一同參與的還有兩位業(yè)內(nèi)專家:新思科技 (Synopsys) 的 Madhumita Sanyal 和安立公司 (Anritsu) 的 Hiroshi Goto。我們討論了最新 PCIe 版本面臨的挑戰(zhàn)以及 PCIe 7.0 可能面臨的挑戰(zhàn)。PCIe Express 6.0的開發(fā)和設(shè)計(jì)仍在不斷演化和成熟中,包括外形標(biāo)準(zhǔn)、測試規(guī)范等等。然而,PCI-SIG®已經(jīng)宣布并已經(jīng)開始了Gen 7.0的開發(fā),我們預(yù)計(jì)到2025年將會(huì)有一個(gè)基本規(guī)范。我們有望實(shí)現(xiàn)每秒128千兆傳輸速率和與Gen 6.0一樣的PAM4信號調(diào)制技術(shù)。

正如Madhumita所言:

“現(xiàn)在正處于一個(gè)非常有趣的時(shí)代,傳輸速率從 64 Gt/s 提升到了 128 GT/s。這相當(dāng)于要求具有以下特性的以太網(wǎng)連接:1.6 TB 帶寬,16 個(gè)傳輸速率為 128 Gt/s 的通道,總傳輸速率為 2 TB/s 且是單向,這是以太網(wǎng)世界的要求。并且保留了 PAM4,奈奎斯特現(xiàn)在為 32 GB,但需要向后兼容所有之前版本。

“我認(rèn)為它仍會(huì)使用 Flits,誰知道哪種 FEC(前向糾錯(cuò)碼)更強(qiáng)大呢?需要 FEC 就像以太網(wǎng) LAN 需要 Reed Solomon 糾刪碼一樣,也可能仍然使用輕型 FEC 就可以,也會(huì)提升數(shù)據(jù)傳輸速率。當(dāng)然,協(xié)議本身可能會(huì)進(jìn)行極大的改進(jìn)。我認(rèn)為電氣設(shè)備將越來越可靠,具體取決于 PCI-SIG 如何定義通道。我們可能需要新的主板、連接器和電纜。SERDES 發(fā)送器和接收器架構(gòu)肯定會(huì)面臨一些新的挑戰(zhàn)。”

Hiroshi Goto補(bǔ)充道:

“內(nèi)容增加了,通道損耗有多少?從 Gen 5.0 到 Gen 6.0,從 32 GT/s 到 64 GT/s——P 和 N 之間的時(shí)鐘偏差無論是正還是負(fù),現(xiàn)在都極其關(guān)鍵。一毫米的電纜差異會(huì)帶來五皮秒的失配。所以,P 和 N 的時(shí)鐘偏差失配也會(huì)產(chǎn)生重要影響。

“人們已經(jīng)做了大量工作來研究如何保持與卡機(jī)電 (CEM) 連接器的向后兼容性。我認(rèn)為這是需要密切關(guān)注的問題。我們是否能夠繼續(xù)實(shí)現(xiàn)向后兼容性?我們是否必須考慮從主機(jī)到端點(diǎn)的替代連接類型?”

小組討論結(jié)束后,泰克參加了 2023 年 6 月 13 日至 2023 年 6 月 14 日在美國加州圣克拉拉舉行的 PCI-SIG 開發(fā)者大會(huì),會(huì)上 PCI-SIG 宣布了 PCI Express (PCIe) 7.0 規(guī)范已升級至 0.3 版。

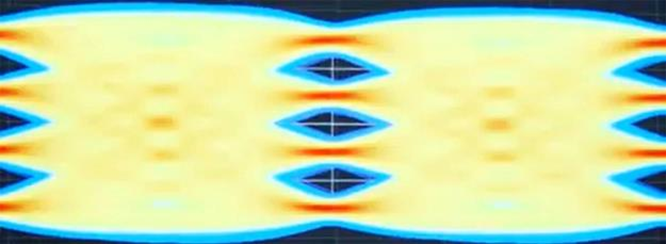

在該活動(dòng)上,新思科技進(jìn)行了一次所謂的“窺探式”演示,展示了PCIe 7.0即將達(dá)到的128 GT/s的數(shù)據(jù)傳輸速率。在演示中,新思科技評估板將 PRBS 模式發(fā)送到泰克 DPO70000SX 示波器上。所有三個(gè) 128 GT/s PAM4 眼圖均打開,三者之間具有良好的線性度、低抖動(dòng)和良好的比率電平失配 (RLM)。

成功的 128GT/S PAM4 眼圖

在第二場演示中,安利公司重點(diǎn)展示了安利 MP1900A 誤碼檢測器與泰克 DPO70000SX 實(shí)時(shí)示波器以及新思科技 PCIe 6.0 PHY & 控制器 IP 在端到端系統(tǒng)中的兼容表現(xiàn),清晰顯示了 FEC 應(yīng)用前后的誤碼率對比情況。 在此演示中,泰克示波器校準(zhǔn)的 33db 應(yīng)力眼圖由充當(dāng)主機(jī)的安利誤碼檢測器發(fā)送到具有 PHY 端控制器的新思科技端到端解決方案。接收器對受壓的模式進(jìn)行均衡,并將信號通過控制器回環(huán)至 PHY 發(fā)送器,再由發(fā)送器將信號返回至安利誤碼檢測器。包括 Gen 6 階段 1-3 在內(nèi)的所有代際的鏈路訓(xùn)練均已完成且通過了測試。

查看2023泰克創(chuàng)新論壇所有技術(shù)內(nèi)容,請移步回放大廳https://tif2023-china-event.vhall.com/。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號