近日,中國科學院微電子研究所集成電路先導工藝研發中心在22納米CMOS關鍵技術先導研發上取得突破性進展,在國內首次采用后高K工藝成功研制出包含先進的高K/金屬柵模塊的22納米柵長MOSFETs,器件性能良好,達到國內領先、世界一流水平。

22 納米 CMOS技術是全球正在研究開發的最新一代集成電路制造工藝,各國都投入了巨大資金,力爭搶占技術制高點。Intel開發的基于三柵器件結構的處理器已于近期實現量產;IBM聯盟也于近期發布了采用22納米工藝生產的SRAM芯片;Global Foundries,歐洲的IMEC,日韓的三星、Toshiba和我國臺灣的臺積電也發布了各自的22納米制程技術;我國于2009年在國家科技重大專項的支持下開始22納米關鍵技術先導研發。作為該項目的牽頭單位,中科院微電子研究所集成電路先導工藝研發中心與項目聯合承擔單位,北京大學、清華大學、復旦大學和中科院微系統所的項目組一道,開展了系統的聯合攻關。經過3年多的辛勤努力,該項目于近期取得突破性進展。

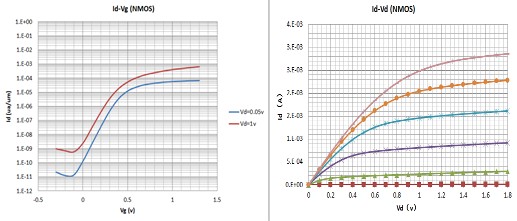

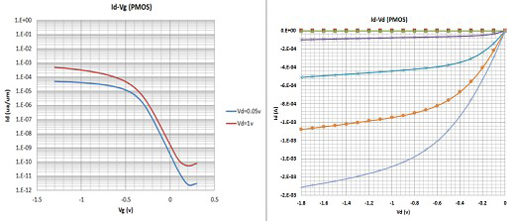

在22納米CMOS技術節點,為了降低成本、減少功耗和提高器件性能,高K/金屬柵技術被廣泛引入,同時也對器件制造工藝及集成技術帶來了很大的挑戰,主要包括了以下幾個方面:一是界面工程,需要研究高K材料與硅溝道的界面態特性、應力引入控制機制、影響載流子遷移率的原理機制等;二是柵工程,對高性能的NMOS和PMOS器件而言,篩選出具有合適功函數的金屬柵材料及堆疊結構避免費米釘扎效應,降低刻蝕工藝及集成技術的難度至關重要;三是需要實現超淺結的源漏工程,確保器件具有良好的短溝道效應抑制特性和歐姆接觸。針對上述核心問題,項目組開展了系統的研究工作,在N型和P型MOS電容上均獲得了EOT≤8.5 ?,漏電流降低3個數量級,金屬柵有效功函數距硅帶隙邊距離≤0.2eV的良好電學結果。成功研制出器件性能良好的22納米柵長MOSFET器件(圖1)。其中,NMOS和PMOS的閾值電壓分別達到工業要求的0.3V 和-0.28V左右,在|Vdd|= 1V時飽和導通電流Ion (在沒有使用應變硅增強技術的條件下)分別達到465µA/µm和368µA/µm,短溝道效應得到很好的改善,亞閾值擺幅(SS)和漏致勢壘降低(DIBL)控制在85mV/dec和65mV以內(圖2),均滿足工業應用標準。

在這一過程中,中科院微電子研究所與北京大學、清華大學、復旦大學以及中科院微系統所的聯合項目組完成了1369項專利申請,其中包括424項國際專利申請,為我國在集成電路領域掌握自主知識產權,取得國際話語權奠定了基礎,其中后高K/金屬柵工藝模塊及相關專利、金屬柵堆疊結構及其專利等均已開始在國內集成電路制造企業進行進一步的生產工藝開發。

多年來,我國的集成電路先進制造工藝大多是在引進的核心知識產權上進行產品工藝開發,在全球產業鏈最先進工藝的開發上缺少布局和話語權。此次22納米關鍵技術先導研發是國內第一次在全球最先進工藝技術代組織這么大規模的產學研聯合攻關,同期,國內制造企業在28納米工藝上也在進行開發,目標就是在22納米核心技術的知識產權中取得一席之地,在我國集成電路制造產業進入22納米技術代時,開始擁有自己的話語權。該成果的取得對我國集成電路產業在22納米獲得具有自主知識產權的核心技術有重要意義,也為我國繼續自主研發16納米及以下技術代的關鍵工藝提供了必要的技術支撐。結合國內制造企業在28納米技術研發上取得的突破,我國已開始在全球尖端集成電路技術創新鏈中擁有自己的地位。

圖1 22納米 柵長NMOS截面和高K/金屬柵堆疊結構的TEM照片(中科院微電子研究所,2012)

圖2 NMOS的Id-Vg轉移曲線以及Id-Vd輸出曲線(中科院微電子研究所,2012)

圖3 PMOS的Id-Vg轉移曲線以及Id-Vd輸出曲線(中科院微電子研究所,2012)

粵公網安備 44030902003195號

粵公網安備 44030902003195號