在美國國防先期研究計劃局(DARPA)的部分資金支持下,美國普度大學研究出采用絕緣體上硅(SOI)互補金屬氧化物半導體(CMOS)工藝、基于三層共源共柵(triple Cascode)組合晶體管版圖的高效率功率放大器,適用于下一代移動電話、車用低成本防撞雷達和通信用輕量微型衛星。

現有移動電話中傳輸信號用功率放大器主要采用砷化鎵(GaAs),由于不能與其他硅基CMOS信號處理器件集成,限制了移動電話集成度的進一步提升。新的放大器基于CMOS設計,可提高集成度、壽命和性能,減少制造和測試成本,并降低功耗。

普度大學在新設計的SOI CMOS放大器中,對部分硅晶體管進行了堆疊合并,減少了晶體管間通常所需的金屬互聯數量,從而減少了寄生電容和獲取更高工作頻率。

第五代移動電話(預計在2019年)需要能夠工作在更高頻率和效率的功率放大器,提供比現有手機更快的數據傳輸和視頻下載速度,并消耗更少的功耗,以更好地滿足新興物聯網需求。值得一提的是,新研制的CMOS放大器還將有力推動微型衛星的發展,將微型衛星的重量降為現有技術的百分之一。

研究人員目前正在研究新一版功率放大器,功率性能將再提升一倍。下一步的工作是將該放大器與手機其他器件實現單片集成。研究人員為該研究結果發表了兩篇論文,并正申請三項專利。

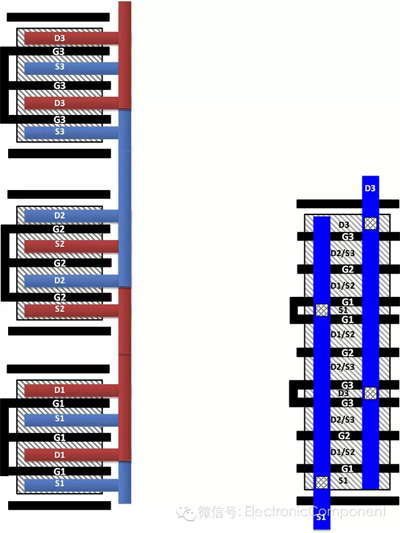

左圖是移動手機中功率放大器的標準版圖,右邊是普度大學的新設計

技術細節

堆疊的三級共源共柵結構作為功率放大器的基本單元,能夠容易地獲取高增益、高功率、高效率和縮小版圖面積。研究人員用格羅方德45nm CMOS SOI工藝制造出兩個毫米波功堆疊率放大器。

第一個功率放大器工作在K波段(24-28GHz),帶有三個三級共源共柵單元,每個單元都使用標準帶有獨立版圖的晶體管。在24GHz、偏置電壓10.8V時,最大線性功率增益是13dB,飽和輸出電壓是25.3dBm,-1dB輸出功率(P1dB)是23.8dBm,峰值功率附加效率(PAE)是20%。

第二個功率放大器工作在U波段(40-60GHz),帶有兩個三級共源共柵單元,每個單元采用了組合型版圖,有效減少內部寄生電容,帶來PAE性能的顯著提升。在46GHz、偏置電壓6V下,飽和輸出功率(PSAT)達到22.4dBm,線性增益17.4dB,峰值PAE42%,漏極效率(DE)49%。在46GHz、偏置電壓4.8V下,PSAT減小至20dBm,DE和峰值PAE分別增加至53%和45%。

來源:大國重器——聚焦世界軍用電子元器件

粵公網安備 44030902003195號

粵公網安備 44030902003195號