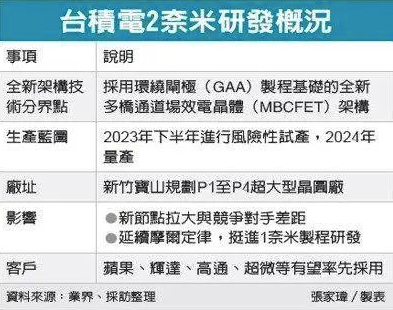

一、臺積電:第一家官宣2nm工藝,研發進度超前

據臺灣經濟日報報道,臺積電2nm工藝取得重大突破,研發進度超前,業界看好其2023年下半年風險試產良率就可以達到90%。

據臺媒透露,有別于3nm與5nm采用鰭式場效晶體管(FinFET)架構,臺積電2nm改采全新的多橋通道場效晶體管(MBCFET)架構,研發進度超前。

據悉,臺積電去年成立了2nm專案研發團隊,尋找可行路徑進行開發。

考量成本、設備相容、技術成熟及效能表現等多項條件,2nm采以環繞閘極(GAA)制程為基礎的MBCFET架構,解決FinFET因制程微縮產生電流控制漏電的物理極限問題。

極紫外光(EUV)微顯影技術的提升,使臺積電研發多年的納米片(Nano Sheet)堆疊關鍵技術更為成熟,良率提升進度較預期順利。

臺積電此前透露2nm研發生產將在新竹寶山,規劃P1到P4四個超大型晶圓廠,占地90多公頃。

臺積電5nm已經量產,3nm預計2022年量產,2nm研發現已經取得重大突破!

二、FinFET的替代者出現,GAA技術給摩爾定律續命

摩爾定律表明:每隔18~24 個月,集成電路上可容納的元器件數目便會增加一倍,芯片的性能也會隨之翻一番。

然而,在摩爾定律放緩甚至失效的今天,全球幾大半導體公司依舊在拼命「廝殺」,希望率先拿下制造工藝布局的制高點。

從2012年起,FinFet已經開始向20mm節點和14nm節點推進。

并且,依托FinEFT技術,芯片工藝節點制程已經發展到7nm,5nm甚至是3nm,也遇到了瓶頸。

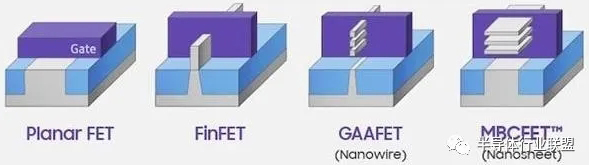

而全環繞柵(GAA)是FinFET技術的演進,溝道由納米線(nanowire)構成,其四面都被柵極圍繞,從而再度增強柵極對溝道的控制能力,有效減少漏電。

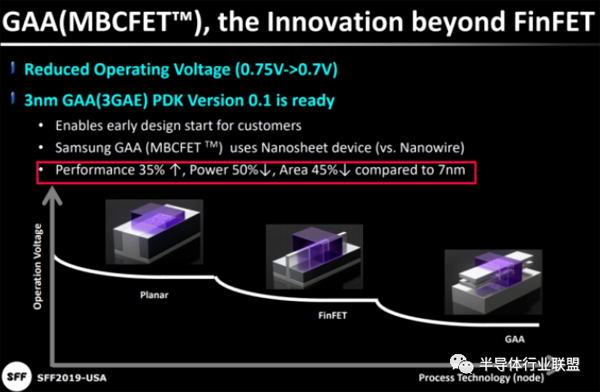

與現在的7nm工藝相比,3nm工藝的具體指標表現為:可將核心面積減少45%,功耗降低50%,性能提升35%。

臺積電2nm采用的GAA(Gate-all-around,環繞閘極)或稱為GAAFET,它和FinFETs有相同的理念,不同之處在于GAA的柵極對溝道的四面包裹,源極和漏極不再和基底接觸。

根據設計的不同,GAA也有不同的形態,目前比較主流的四個技術是納米線、板片狀結構多路橋接鰭片、六角形截面納米線、納米環。

三星對外介紹的GAA技術是Multi-Bridge Channel FET(MBCFET),即板片狀結構多路橋接鰭片。

臺積電同樣采用MBCFET架構。臺積電總裁魏哲家日前于玉山科技協會晚宴專講時透露,臺積電制程每前進一個世代,客戶的產品速度效能提升30%- 40%,功耗可以降低20%-30%。

GAA可以帶來性能和功耗的降低,但成本也非常高。市場研究機構International Business Strategies (IBS)給出的數據顯示,28nm之后芯片的成本迅速上升。28nm工藝的成本為0.629億美元,5nm將暴增至4.76 億美元。三星稱其3nm GAA 的成本可能會超過5億美元

三、臺積電:1nm芯片,沒問題!

在近日的“2020世界半導體大會”上,臺積電南京公司總經理羅鎮球表示,芯片制程工藝持續推進,摩爾定律仍將適用---3nm、2nm、1nm都沒有什么太大問題。

羅鎮球透露,2021年可以在市面上看到3nm的產品,臺積電計劃在2022年實現3nm產品的大規模量產。

據羅鎮球透露,目前,臺積電7nm工藝有超過140個產品在生產,同時,臺積電還持續投入7nm+和6nm工藝。

公開資料顯示,臺積電南京公司成立于2016年,是臺積電的全資子公司,下設有一座十二英寸晶圓廠和一個設計服務中心。該公司去年營收40億元,同比增長170%。

臺積電5nm、4nm、3nm、2nm芯片最新情況如下:

① 目前,臺積電5nm芯片已經進入量產階段良率推進遠遠好于3年前的7nm;② 預計4nm芯片在2021年開始正式批量生產;

③ 臺積電3nm芯片,性能可以再提升10-15%,功耗可以再降低25-30%。預計可以看到3nm芯片產品將在2022年進入大批量生產;

④ 此外,在日前召開的“臺積電技術論壇”上,臺積電透露了2nm芯片的最新布局---已經在新竹購買了土地用于建設2nm工廠和新的研發中心,投入8000多名工程師進一步推動2nm節點研發。

粵公網安備 44030902003195號

粵公網安備 44030902003195號