邏輯分析的概念

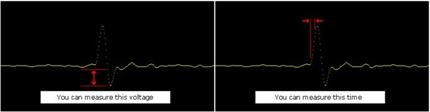

邏輯分析儀也是非常常用的儀表,與示波器一樣,是數字設計和測量的經典儀器之一。數字電路測量時,何時應使用示波器呢?一般而言,當需要精確參數信息(如時間間隔和電壓讀數)時可以使用示波器。具體來講:

當需要測量信號的較小電壓偏移(如低于或超出)時。

當需要較高的時間間隔精度時。示波器能夠采集精確的參數信息,如脈沖的上升沿上兩點之間的高精度時間。

圖1 示波器用于測量信號的模擬波形

一般而言,邏輯分析儀用于查看多個信號之間的定時關系,或者用于捕獲信號所運載的數據。當被測設備的信號超過電壓閥值時,邏輯分析儀會表現出與邏輯電路相同的反應。它將識別信號的高低。具體來講:

當需要立即查看多個信號時。邏輯分析儀可以很好地組織和顯示多個信號。一般任務是將多個信號組成一條總線并分配一個自定義名稱。地址、數據和控制總線都是有代表性的示例。

當需要使用與硬件相同的方式查看系統中的信號時。信號顯示在一個時間軸上,這樣就可以查看相對于其他總線信號或時鐘信號的轉變的發生時間。

當需要象接收芯片一樣基于時鐘邊沿,捕獲總線中的信息時。接收芯片基于時鐘邊沿判斷總線上的地址、命令和數據。邏輯分析儀象一個偵聽器,捕獲總線上傳輸的這些信息,并把需要的信息存入存儲器。可設置觸發條件,捕獲需要關注的或出問題的總線上的信息,據此可了解協議或軟件執行的情況。

上面已經簡短討論了邏輯分析儀的一些用法,現在,讓我們更詳細地了解一下有關邏輯分析儀的概念。到目前為止,我們已經很廣泛地使用了“邏輯分析儀”這一術語。實際上,大多數邏輯分析儀中都包含兩個分析儀。

1.定時分析儀:

定時分析儀是邏輯分析儀的一部分,它與示波器相似。事實上,它們之間的關系非常密切。定時分析儀顯示信息的一般形式,這一點與示波器相同,即橫軸表示時間,縱軸表示電壓振幅。因為兩個儀器上的波形都取決于時間,所以這種顯示可以說是“時間域”中的顯示。

2.狀態分析儀:

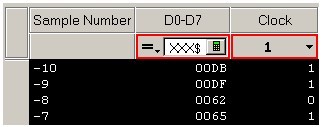

狀態分析儀非常適用于跟蹤軟件中的缺陷或硬件中的缺陷組件。它有助于確定問題是出現在軟件代碼中還是出現在某些硬件設備中。大多數情況下,狀態分析儀用于在出現特定時鐘信號時查找總線上存在哪些邏輯電平。換句話說,可以了解在時鐘出現且假設數據有效時將顯示哪些“活動狀態”。內存中采集的數據將以列表格式顯示,且帶有連接到各個狀態的時間標簽。

定時分析

定時分析儀使用自己的內部時鐘控制數據采樣。這種類型的時鐘計時會使邏輯分析儀中的數據采樣與被測設備中的時鐘異步。具體來講:

定時分析儀適用于顯示信號活動“相當于其他信號”“何時”發生。

定時分析儀側重于查看各個信號之間的時序關系,而不是與被測設備中控制執行的信號之間的時序關系。

這就是為什么定時分析儀可以對與被測設備時鐘信號“不同步”或異步的數據進行采樣。

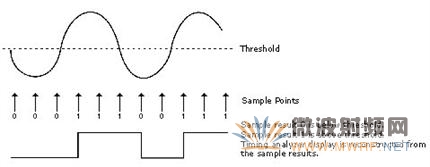

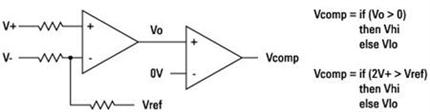

在定時采集模式下,邏輯分析儀的工作是對輸入波形進行采樣,從而確定它們是高電平還是低電平。為了確定高低,邏輯分析儀會將輸入信號的電壓電平與用戶定義的電壓閾值進行比較。如果采樣時信號高于閾值,則分析儀將信號顯示為 1 或高。同樣,低于閾值的信號將顯示為 0 或低。下圖闡釋了當正弦波跨過閾值電平時邏輯分析儀對其進行采樣的情況。

圖2

采集之后采樣點被存儲在內存中,并用于重建方形數字波形。這種要使一切變成方形的處理方式似乎會限制定時分析儀的用處。不過定時分析儀本來也不是打算用作參數儀器的。若要查看信號的上升時間,可以使用示波器。若需校驗幾個或幾百個信號之間的時序關系,對其同時進行查看,則定時分析儀才是正確的選擇。

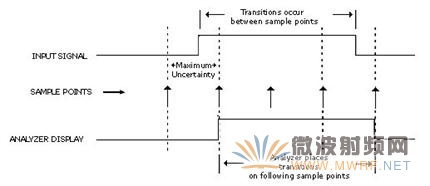

定時分析儀對輸入通道進行采樣時,該通道信號或者是高電平或者是低電平。如果在進行某一采樣時該通道處于某種狀態(高或低),而在進行下一采樣時變成了相反的狀態,則分析儀可以“知道”輸入信號已在這兩個采樣之間的某個時候發生了跳變。但它不知道具體在何時,因此它將跳變點放在了后一個采樣上,如下圖所示。

圖3 定時分析采樣精度(不確定度)

對于跳變實際上是在何時發生以及分析儀何時顯示跳變,存在著某種含糊性。假如跳變是在前一個采樣點之后立即發生的,這種不確定性最多也就是一個采樣周期。不過對于這種方法,在精度和總采樣時間之間也存在著一種折衷。請記住,每個采樣點都只使用一個存儲位置。因此,精度越高(采樣頻率越高),采樣周期越短。

觸發定時分析儀:

在測量中的某些點,邏輯分析儀必須了解何時采集(存儲)流經其內存的數據。這些點叫做觸發點。

使分析儀觸發的一種方法是:相應地配置分析儀,使之從一組信號(總線)中查找上限或下限碼型,或者查找單個信號的上升或下降時鐘沿。當分析儀在數據中發現指定的碼型或時鐘沿時,它便觸發。

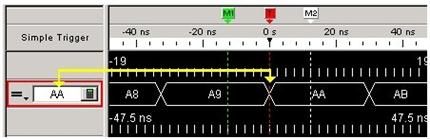

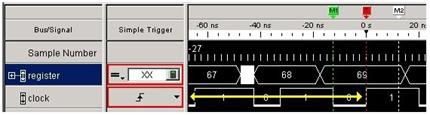

碼型觸發:

碼型觸發用于在總線上查找特定的上限和下限碼型。您可以指定不同的標準,如等于、不等于、在或不在某個范圍內或者大于/小于。

示例:擁有一條包含 8 條信號線的總線。配置了簡單觸發 以指定分析儀在輸入數據等于“AA”碼型時觸發。

圖4 碼型觸發

為了更便于某些用戶的使用,大多數分析儀上的觸發點不僅可以用十六進制進行設置,還可以用二進制(1 和 0)、八進制、ASCII 或十進制進行設置。例如,十六進制觸發值 AA 還可以設置為等價的二進制觸發值 1010 1010。但是,在 16、24、32 或 64 位寬的總線上查找時,使用十六進制設置觸發點尤其有幫助。

時鐘沿觸發:

時鐘沿觸發對于習慣使用示波器的用戶來說是一個很熟悉的概念。調整示波器上的“trigger level”(觸發電平)旋鈕時,可以將其視為設置電壓比較儀的電平:當輸入電壓超過該電平時,電壓比較儀會告知示波器觸發。定時分析儀的時鐘沿觸發大體上與此相同,只不過將觸發電平預先設置成了一個邏輯閾值。

許多邏輯設備依賴于電平,而這些設備的時鐘和控制信號卻往往受時鐘沿的影響。通過時鐘沿觸發,可以在對設備進行定時的同時開始采集數據。

示例:試想一個未正確移位數據的時鐘沿觸發移位寄存器。是數據有問題還是時鐘沿有問題?為檢測設備,我們需要在對其進行定時的同時檢驗數據(基于時鐘沿)。可以告知分析儀在出現時鐘沿時(無論上升或下降)采集數據并獲取移位寄存器的所有輸出。

圖5 邊沿觸發

跳變定時:

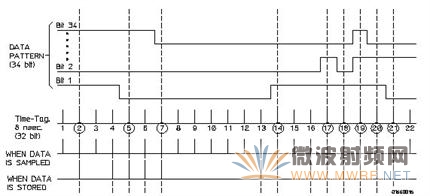

在 Transitional / Store qualified(跳變/存儲限定)定時模式中,定時分析儀將定期對數據進行采樣,但只有當閾電壓電平中存在信號轉變時才存儲數據。每當定義的總線/信號(未排除的)中的任何位發生轉變時,都要存儲所有通道上的數據。為每個存儲數據樣本存儲一個時間標簽,這樣稍后就可以重新構建和顯示測量。

通常,各個采樣點不會發生轉變。下面將用時間標簽 2、5、7 和 14 來舉例說明。當確實發生轉變時,為每個轉變存儲兩個樣本。因此,存儲 1K 的轉變,就會帶有 2K 內存的樣本。必須去除一個起始點必需的轉變才能使存儲的最小轉變量達到 1023。

如果轉變發生的速率很快,例如每個采樣點都有一個轉變,那么如下圖中的時間標簽 17 至 21 所示,只為每個轉變存儲一個樣本。如果整個跟蹤過程始終保持這種狀況,那么存儲的轉變數量為 2K 樣本。此外,必須去除起始點樣本,這樣才能使存儲的最大跳變量不超過 2047。

圖6 跳變定時的數據存儲

大多數情況下,當最小轉變量和最大轉變量都存在時會存儲跳變時序跟蹤。因此,在此例中存儲的實際轉變量將在 1023 和 2047 之間。

跳變定時注意事項:

檢測到時鐘沿時,在分配給定時分析儀的所有通道中存儲兩個樣本。如果在時鐘沿檢測器重置之前出現第二個時鐘沿(在第一個時鐘沿后),為避免數據丟失需要兩個樣本。

在跳變定時中,每個序列步驟只有 2 個分支。在跳變時序中,只有一個全局計數器可用。

跳變時序需要有時間標簽才能重建數據。通過將時間標簽與內存中的測量數據交叉可存儲時間標簽。

默認情況下,分析儀將查找為邏輯分析儀模塊定義的所有總線/信號上的轉變。但是,為增加可用內存深度和采集時間,可以在高級觸發中選擇不存儲某些總線/信號轉變(如將無用信息添加到測量中的時鐘或選通脈沖信號)。

運行測量時,無論總線/信號是否定義或是否分配給邏輯分析儀通道,都將在所有這些通道上采集數據。在跳變時序模式中,如果定義的 總線/信號(未排除的)上存在轉變,將保存采集的樣本。

運行跳變時序測量后,如果為以前未分配的邏輯分析儀通道定義新的總線/信號,那么將顯示在這些通道上采集的數據,但是不可能存儲這些總線/信號上的所有轉變;顯示的數據好似新的總線/信號在運行測量前就已經被排除了。

在跳變時序中,不需要預先存儲數據(觸發前獲得的樣本)。因此,與狀態模式非常相似的是,觸發位置(起始/中心/結束)表明觸發后樣本占用內存的百分比。觸發前獲得/顯示的樣本數量在不同的測量中會有所變化。

狀態分析

狀態分析儀需要來自被測設備的采樣時鐘信號。這種類型的時鐘計時可使邏輯分析儀中的數據采樣與被測設備中的計時事件同步。具體來講:

狀態分析儀適用于顯示“有效時鐘或控制信號”期間的信號活動是“什么”。

狀態分析儀側重于查看指定執行時間內的信號活動,而不是與時序無關的信號活動。

這就是為什么狀態分析儀需要對與被測設備時鐘信號“同步化”或同步的數據進行采樣。

對于微處理器,數據和地址可以出現在相同的信號線上。要采集正確的數據,邏輯分析儀必須對數據采樣加以限制,使之只在所需的數據有效并出現在信號線上時進行。為此,它會從相同的信號線上采集數據樣本,但使用來自被測設備的不同采樣時鐘。

示例:以下時序圖表明,要采集地址,分析儀需要在 MREQ 線下降時進行采樣。

要采集數據,分析儀需要在 WR 線下降(寫周期)或 RD 線下降(讀周期)時進行采樣。

圖7 狀態采集

觸發狀態分析儀:

與定時分析儀相似,狀態分析儀也具有限定要存儲的數據的功能。如果我們正在查找地址總線的上限和下限的特定碼型,當分析儀找到該碼型時,我們可以通知分析儀開始存儲,并且只要分析儀的內存未滿就一直存儲。

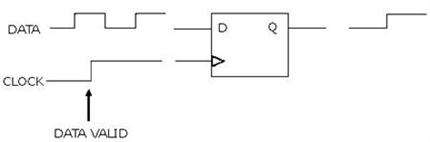

簡單觸發示例:

請看下面顯示的“D”觸發器,在正值的時鐘沿出現之前,“D”輸入上的數據是無效的。因此,時鐘輸入為上限時,觸發器的狀態才有效。

圖8 D觸發器

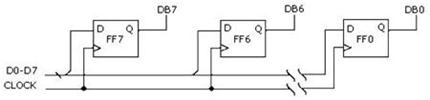

現在,假設我們有并行的八個此類觸發器。如下所示,這八個觸發器都連接到同一時鐘信號。

圖9 接收器

當時鐘線上出現高電平時,所有這八個觸發器都會在其“D”輸入處采集數據。此外,每次時鐘線上出現正電平時都會發生有效狀態。下面的簡單觸發指示分析儀在時鐘線上出現高電平時在 D0 - D7 這幾條上收集數據。

圖10

高級觸發示例:

假設想查看地址值為 406F6 時內存中存儲了哪些數據。對高級觸發進行配置,以在地址總線上查找碼型 406F6(十六進制)以及在 RD(內存讀取)時鐘線上查找高電平。

圖11 高級觸發設置

在配置 Edge And Pattern trigger(時鐘沿和碼型觸發)對話框時,嘗試將該操作看作是構造從左向右讀取的句子。

Find the first occurrence of a Bus named ADDR, and on All bits a pattern that Equals 406F6 Hex, And a Signal named RD with a High level.Then Trigger and fill memory with Anything.

Pod、通道和時間標簽存儲

Pod和通道的命名約定:

Pod是一組邏輯分析儀通道的組合,共有17個通道,其中數據16個通道,時鐘1個通道。邏輯分析儀的通道數是Pod數的倍數關系。34通道的邏輯分析儀對應兩個Pod,68通道邏輯分析儀對應4個Pod,136通道邏輯分析儀對應8個Pod。

對于模塊化的邏輯分析儀(或稱為邏輯分析系統),以 16900 系列邏輯分析系統為例,對應關系如下:

1.插槽從上到下以 A 至 F 字母命名。

2.有一條標有 Pod 2 的電纜連接著每一個邏輯分析儀模塊。知道某個Pod連接到哪個插槽很重要,因為如果在插槽 A 和 B 中都有邏輯分析儀模塊,則將有兩條盒電纜標有 Pod 2,但操作界面應用程序會把一條記作 Slot A Pod 2,把另一條記作 Slot B Pod 2。分清這兩條電纜很重要。

3.Slot A Pod 2 等于 Pod A2。A2 與 Slot A Pod 2 可互相替代;同樣,D1 與 Slot D Pod 1 也可互相替代。

4.時鐘Pod (Clock Pod) 由模塊中所有Pod的所有時鐘通道組成。

5.每個Pod各有一個時鐘通道。所有時鐘通道按 Clk1、Clk2、Clk3 等進行編號。如果某邏輯分析儀模塊有兩個邏輯分析儀卡,每卡有四個Pod,則該邏輯分析儀的時鐘通道標記為 Clk1 至 Clk8。

6.除了 Clk1 外,時鐘通道還可標記為 C1。C1 和 Clk1 是一樣的。

在 16900 系列邏輯分析系統中,請勿混淆時鐘通道 C2 與 Slot C 中的 Pod 2,后者記作 Pod C2。對于時鐘通道,C 是 Clock 的縮寫,不是 Slot C 的縮寫。

為什么有時Pod會丟失?

導致所有Pod對邏輯分析儀模塊均不可用的原因有多種:

在狀態采樣模式中,在選擇了一般狀態模式采樣選項的情況下,選擇最大采集內存深度需要將一個Pod對保留用于時間標簽存儲。在這種情況下,將內存深度設置為最大值的一半(或更小)將返回Pod。

在狀態采樣模式中,在選擇了高速狀態模式采樣選項的情況下,會將一個Pod對保留用于時間標簽存儲。

在定時采樣模式中,在選擇了跳變/存儲限定定時模式采樣選項的情況下:

選擇了最小采樣周期時,會將一個Pod對保留用于時間標簽存儲。

選擇了除最小采樣周期之外的采樣周期時,選擇最大采集內存深度需要將一個Pod對保留用于時間標簽存儲。在這種情況下,將內存深度設置為最大值的一半(或更小)將返回Pod。

該模塊是已分離的邏輯分析儀的一部分。在這種情況下,Pod位于分離分析儀的另一半模塊中。

狀態模式和跳變定時模式下通道數、內存深度和觸發之間的相互影響:

狀態采樣模式時,時間標簽存儲需要1個Pod或1/2的采集內存。

在操作界面應用程序中,所有模塊都與時間相關;不能關閉 time tag storage(時間標簽存儲)(雖然以前的 Agilent 邏輯分析系統可以)。

要使用 1/2 以上的模塊采集內存,必須將一個Pod保留用于時間標簽存儲。要使用所有Pod,內存使用量不能超過模塊采集內存的 1/2。

一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同。

默認設置:

時間標簽存儲始終處于開啟狀態(并且不能將其關閉)。

內存深度設置為總采集內存的 1/2。

所有盒對都可用于采集數據。

如果選擇整個內存,則要用于時間標簽存儲的默認Pod是最左邊的盒對,但未分配總線或信號的任何Pod都是可以使用的。

跳變定時模式,時間標簽存儲需要1個Pod或1/2的采集內存:

跳變時序采樣模式也需要時間標簽存儲。

當選擇最小采樣周期時,必須將一個Pod對 保留用于時間標簽存儲。在這種情況下,不能使用 1/2(或更少)的模塊采集內存來替代該Pod。

對于其他采樣周期,內存深度和通道數的權衡與狀態采樣模式下的相同。也就是說,要使用 1/2 以上的模塊采集內存,必須將一個Pod 保留用于時間標簽存儲。要使用所有Pod,內存使用量不能超過模塊采集內存的 1/2。

一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同。

狀態模式采樣位置、眼定位和眼圖掃描

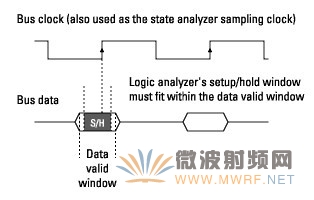

同步采樣(狀態模式)邏輯分析儀與觸發時鐘沿的觸發相似,因為它們都需要輸入邏輯信號才可以在時鐘事件前(建立時間)和時鐘事件后(保持時間)的一段時間內保持穩定,以便正確解釋邏輯電平。組合建立和保持時間被稱為建立/保持窗口。

被測設備(由于其本身的建立/保持要求)可指定數據在某段時間內在總線上有效。這被稱為數據有效窗口。一般情況下,大多總線上的數據有效窗口小于總線時間周期的一半。

要精確采集總線上的數據,需符合以下條件:

邏輯分析儀的建立/保持時間必須在數據有效窗口內。

圖12 有效采集窗口

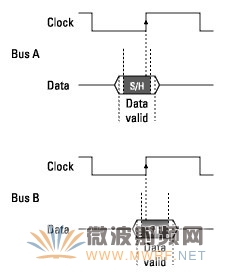

由于與總線時鐘有關的數據有效窗口的位置根據總線類型的不同而有所變化,因此邏輯分析儀的建立/保持窗口的位置在數據有效窗口中必須是可調整的(相對于采樣時鐘,且具有較高分辨率)。例如:

圖13 調整采樣位置

為了將建立/保持窗口(采樣位置)放置在數據有效窗口內,邏輯分析儀可在每次采樣輸入時調整延遲(以定位每個通道的建立/保持窗口)。

如果可以在單個通道上調整采樣位置,可以使邏輯分析儀的建立/保持窗口變小,因為可以校準由探頭電纜和邏輯分析儀的內部電路板跟蹤引起的偏移效應,而且還可以看到邏輯分析儀的內部采樣電路的建立/保持要求。

但是,手動定位每個通道的建立/保持窗口需要花費大量時間。對于被測設備中的每個信號和每個邏輯分析儀通道來說,必須測量與總線時鐘(帶有示波器)相關的數據有效窗口,重復定位建立/保持窗口并運行測量以查看邏輯分析儀是否正確采集數據,最后再將建立/保持窗口定位在錯誤采集數據的位置之間。

使用具有眼定位 (eye finder)功能的邏輯分析儀,在手動調整(沒有額外的被測設備)的一小段時間內,可以自動:

定位每個通道上的建立/保持窗口。

針對盡可能寬的數據有效窗口調整閾電壓設置。

眼定位 是獲得盡可能小的邏輯分析儀建立/保持窗口的一種簡單方法。

眼定位概要:

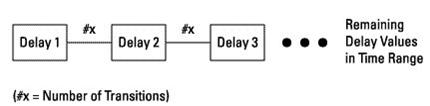

對于指定的狀態采樣時鐘,眼定位 可在時鐘沿前后的一個固定時間范圍內查找數據信號轉變(閾電壓交叉點),并為顯示相關內容以幫助設置最佳采樣位置。

為了了解眼定位 顯示,需為每個活動時鐘沿拍攝一張有關該時鐘沿的數據信號轉變的“照片”。將此照片看作快照、定格畫面或頻閃觀測儀(位于時鐘沿中心或與時鐘沿同步)。到達時鐘沿的時間為 T=0。

例如,如果選擇盒 1 上時鐘輸入的上升沿作為狀態采樣時鐘,每次拍攝“照片”時,都將達到盒 1 時鐘上的上升沿。盒 1 時鐘沿之間的時間是否相同無關緊要。如果同時在上升沿和下降沿上進行采樣,那么在每一個時鐘沿上都會拍攝一張“照片”。此外,在活動沿之間消耗了多少時間也不重要。每一個時鐘沿上都要拍攝“照片”。

要構建眼定位 顯示,需要將無數張這樣的“照片”堆疊在彼此的頂端。每張“照片”都在 T=0 時對齊,此時將達到活動時鐘沿。照片拍自上升沿還是下降沿并沒有關系;它們會在 T=0 時對齊。構建顯示后,就無法區分給定信號轉變區域是與時鐘上升沿相關聯,還是與下降沿(或兩者)相關聯。

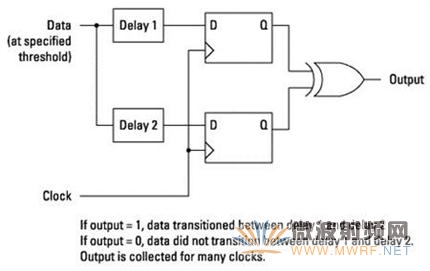

眼定位 工作原理:

通過邏輯分析儀使用少量的偏移延遲對每個通道進行雙重采樣的功能,以及通過使用獨有的 OR 操作比較延遲的樣本可進行眼定位 測量。

圖14

當獨有的 OR 輸出很高時,延遲的樣本會有所差別,并且會在延遲時間之間檢測到轉變。由于采樣信號的不穩定和其他變化,眼定位 測量將對每對延遲值的多個時鐘進行檢查,以便報告兩次延遲時間之間發生轉變的頻率。然后,檢查另一對延遲值,依次類推,直到掃描完轉變的整個時間范圍。

圖15 延遲值記錄

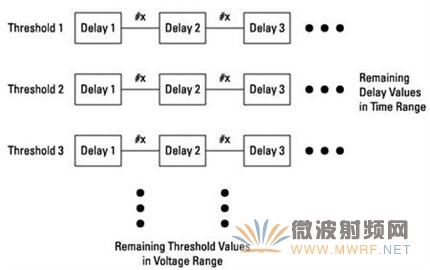

因為邏輯分析儀可以調整通道的閾電壓,所以眼定位 測量可在很多閾電壓電平隨著時間的推移對轉變進行重復掃描。

圖16 眼定位的多閾值掃描

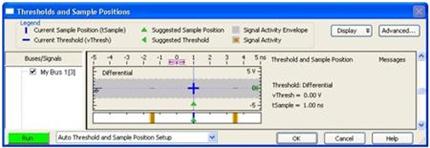

通過調整閾電壓和查看活動指示符,眼定位 可查找信號活動信封并確定最佳閾電壓;然后通過在該閾值執行全時掃描,眼定位 可找出樣本位置。

圖17 眼定位的閾值和采樣位置掃描

也可以在當前閾電壓設置下運行全時掃描,以便僅自動設置采樣位置。

圖18 僅掃描采樣位置

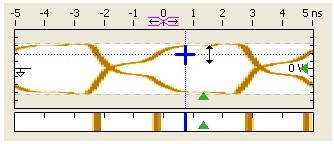

自動閾值和采樣位置設置掃描通常足以確保正確采集數據,但它還可以識別您想要進一步詳細查看的信號(例如,如果您想查看延遲、衰減等)。通過在整個信號活動信封內執行全時掃描,眼定位 可以顯示在時間和電壓的小窗口中檢測到的轉變。這些掃描稱為眼圖掃描(eye scan)。像示波器一樣,眼圖掃描用于顯示測量數據。每個窗口中的轉變數量都會突出顯示。這可以使概覽眼型圖案,并確定是否需要使用示波器來進一步詳細地查看信號。

圖19 眼圖掃描

可以運行導致自動設置閾電壓和采樣位置的 eye scan,或運行只導致自動設置采樣位置的 eye scan。

眼定位 測量收集數據所基于的通道數量會影響測量時間。當一個模塊中存在多個邏輯分析儀卡時將出現異常;在這種情況下,測量將同時并行運行。

支持差分信號的邏輯分析儀中的眼圖掃描Eye Scan:

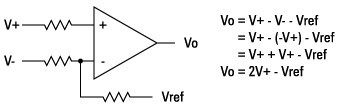

支持差分信號的邏輯分析儀(如16962A 邏輯分析儀模塊)針對輸入使用真值差分接收器:

可編程參考電壓將計入負輸入。這是分析儀采用單端探頭時的閾電壓。對于差分探測的相關操作,通常將參考電壓編寫為 0V:

隨后將接收器的輸出與 0V 進行比較,從差分輸入信號產生內部邏輯信號。請注意,最終比較結果將對“差分信號高于 Vref 還是低于 Vref?”的問題作出解答:

對眼隙的 eye scan 測量是通過使用不同 Vref 設置進行一系列 eye finder 測量完成的。差分信號的默認 eye finder 測量使用 Vref=0V。通過將 Vref 增至零以上,我們會找到信號與上升的 Vref 值交叉的位置。如果 Vref 升至足夠高,信號的頂部軌跡將通過 Vref,我們便會看到眼的頂端。再將 Vref 升高一點會導致 Vcomp 保持在 Vlo,表示信號不會升至該電平。反之,將 Vref 移至零以下會看到眼的下半部。

eye scan/eye finder 顯示窗口會在每個信號的 eye scan 圖下方顯示 eye finder 交疊部分,以此顯示 eye finder 與 eye scan 之間的這一關系。通過在 eye scan 圖中將 Vth 水平線向上和向下移動,可以獲得距離眼中心該偏移量位置處的 eye finder 視圖。

無論用戶界面中的閾值如何設置,邏輯分析儀的差分輸入將始終 應用于接收器。這意味著可通過將電壓閾值手動設置為非零值允許在差分對中使用公共模式電壓。如果信號擺幅中心與地線差距大于 100 mV,eye scan 將自動執行此操作。

邏輯分析儀的觸發

設置邏輯分析儀觸發非常困難,而且還需花費大量時間。假設如果知道如何編程,則應該可以毫不費力地設置邏輯分析儀觸發。然而,這是不可能的,因為許多概念對邏輯分析來說都是唯一的。本節的目的就是介紹這些主要概念及如何有效地使用它們。

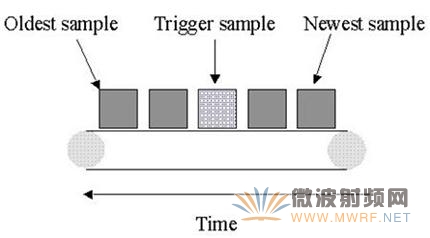

傳送帶類比:我們可以將邏輯分析儀的內存比作一條很長的傳送帶,而從被測設備 (DUT) 獲取的樣本就像是傳送帶上的箱子。新的箱子被放置在傳送帶一端,而在另一端落下。換句話說,由于邏輯分析儀內存的深度(樣本數量)有限,因此每當采集新樣本時,如果內存已滿,將會刪除內存中現有的最舊的樣本。如下圖所示。

圖20

邏輯分析儀觸發就像是放置在傳送帶(上面放置有多個箱子)起始位置上的箱子一樣。它們的任務是“查找特殊的箱子,并在該箱子到達傳送帶的某一特定位置時停止運行傳送帶”。在此類比中,特殊的箱子就是觸發。邏輯分析儀檢測到與觸發條件相匹配的樣本后,就表示當觸發位于內存中的適當位置時應停止繼續采集樣本。

觸發在內存中的位置被稱為觸發位置。通常,觸發位置被設置在中間,以便使觸發前后出現的樣本的最大數量不超出內存范圍。不過,也可以將觸發位置設置在內存中的任意位置。

由于邏輯分析儀觸發提供了大量功能,因此下表將對本文中介紹的功能進行簡要概述。該表將對這些功能進行逐一描述。

表1 邏輯分析儀觸發功能摘要

觸發序列:

雖然邏輯分析儀觸發通常很簡單,但它們卻需要復雜的程序。例如,可能想在某一信號的上升沿后跟另一信號的上升沿時觸發。這意味著邏輯分析器必須在開始尋找下一個上升沿之前找到第一個上升沿。由于擁有一個可查找觸發的步驟序列,因此它被稱為觸發序列。序列的每個步驟被稱為一個序列步驟。

每個序列步驟由兩部分組成:條件和操作。條件是指布爾邏輯表達式,例如“If ADDR = 1000”或“If there is a rising edge on SIG1”。操作是指符合條件時邏輯分析儀應當執行的內容。操作的示例包括觸發邏輯分析儀、轉至另一序列步驟以及啟動定時器。這類似于編程中的 If/Then 語句。

觸發序列中的每個步驟都被指定一個數字。執行的第一個序列步驟總是序列步驟 1,但由于“轉到”操作,剩余的序列步驟可以以任意順序執行。

執行一個序列步驟且布爾邏輯表達式均為假時,邏輯分析儀將采集下一樣本并再次執行同一序列步驟。例如一個簡單的示例,考慮以下觸發序列:

1. If DATA = 7000 then Trigger

如果采集以下樣本,邏輯分析儀將在采集樣本 #6 時觸發。

樣本號 ADDR DATA 1 1000 2000 2 1010 3000 3 1020 4000 4 1030 5000 5 1040 6000 6 1050 7000 <- 此處為邏輯分析儀的觸發位置 7 1060 2000

實際上,序列步驟 1 相當于“Keep acquiring more samples until DATA=7000, then trigger”。

如果符合一個序列步驟中的布爾邏輯表達式,那么在執行下一序列步驟之前總是采集另一樣本。換句話說,如果一個樣本符合序列步驟 1 的條件,在執行序列步驟 2 前將采集另一樣本。這意味著一個單獨的樣本不可能符合多個序列步驟的條件。每個序列步驟都可以看作是代表了在不同點及時發生的事件。兩個序列步驟可以從不用于指定同時發生的兩個事件。

例如,考慮以下觸發序列:

1. If ADDR = 1000 then Go to 2 2. If DATA = 2000 then Trigger

如果采集以下樣本,邏輯分析儀將在采集樣本 #7 時觸發。

樣本號 ADDR DATA 1 1000 2000 <- 此樣本符合序列步驟 #1 中的條件 2 1010 3000 3 1020 4000 4 1030 5000 5 1040 6000 6 1050 7000 7 1060 2000 <- 此處為邏輯分析儀的觸發位置

請注意,由于在符合序列步驟 1 中的條件和測試序列步驟 2 中的條件二者之間采集了新的樣本,因此邏輯分析儀不會在采集樣本 #1 時觸發。可將此觸發序列看作是“Find ADDR = 1000 followed by DATA = 2000 and then trigger”。觸發序列中的多序列步驟暗示了“后接”。

邏輯分析儀觸發后,將不會再次觸發。換句話說,即使度個樣本符合觸發條件,邏輯分析儀也只觸發一次。例如,使用“ADDR=1000”作為觸發,如果邏輯分析器采集以下樣本,它將會在采集樣本 #2 時觸發,并且只在采集樣本 #2 時觸發。

樣本號 ADDR 1 0000 2 1000 <- 此處為邏輯分析儀的觸發位置 3 2000 4 1000 <- 邏輯分析儀不會在此處再次觸發 5 1040

一個經常遇到的問題是“如果不符合序列步驟中的條件會怎樣?”例如,有一個條件是“If ADDR = 1000 Then Trigger”,那么如果當前樣本是 ADDR = 2000,結果會怎樣?邏輯分析儀只采集下一樣本并試圖再次執行此序列步驟。實際上,如果觸發條件是“ADDR = 1000”,這相當于“持續采集樣本直到找到條件為 ADDR=1000 的樣本”。因此,如果設置一個從不符合的觸發條件,邏輯分析器將不會觸發。

當符合序列步驟中的條件時,使用“轉到”操作時下一步將執行哪個序列步驟將會非常清楚,但是如果沒有使用“轉到”操作,則不可能知道執行哪個序列步驟。在一些邏輯分析儀上,如果沒有“轉到”,這意味著應當執行下一序列步驟。在其他邏輯分析儀上,意味著將再次執行同一序列步驟。由于比較混亂,最好使用“轉到”操作而不依靠默認。狀態和定時模塊通過在每個序列步驟中自動包含一個“轉到”或“觸發”操作來解決這一問題。例如: If ADDR = 1000 and DATA = 2000 then Go to 1 <- 這是自動添加的

布爾邏輯表達式:當多個序列步驟表示“后跟”時,可以在序列步驟內使用布爾邏輯表達式。示例:

If ADDR = 1000 and DATA = 2000 此表達式意指在同一樣本中 ADDR 必須等于 1000 且 DATA 等于 2000,才能符合此表達式。換句話說,在 ADDR 等于 1000 的同時 DATA 等于 2000。因此,如果要在同時發生兩個事件時觸發,則應使用布爾邏輯表達式。常見錯誤是應使用布爾邏輯表達式時嘗試使用兩個序列步驟,或者應使用兩個序列步驟時嘗試使用布爾邏輯表達式。當多個事件同時發生時使用布爾邏輯表達式,而在一個事件接著一個事件發生時使用多個序列步驟。

分支:分支類似于 C 編程語言中的 Switch 語句和 Basic 中的 Select Case 語句。分支可提供測試多個條件的方法。每個分支都有其獨有的操作。下面是多分支的一個示例:

1. If ADDR < 1000 then Go To 2 <- This is a branch of Level 1 Else If ADDR > 2000 then Go To 3 <- This is a 2nd branch of Level 1 Else If DATA = 2000 then Trigger <- This is a 3rd branch of Level 1 2. If DATA <= 7000 then Trigger 3. If there is a Rising Edge on SIG1, then Trigger 在序列步驟 1 中,存在三個分支,因此存在三個可以采用的操作。

如果符合某一分支的條件,則不對其下面的任何分支進行測試。換句話說,無法根據單個樣本執行多個分支,即使該樣本可導致符合多個分支條件。也就是說,每個分支都是一個“Else If”。

沿:沿表示單個信號從下到上或從上到下的轉變。通常,沿被指定為“上升沿”、“下降沿”或“任一時鐘沿”,其中“上升沿”表示從下到上的轉變。在大多數邏輯分析儀上,觸發序列中最多可包含兩個沿,而有些則只允許包含一個沿。

范圍:指定值的范圍是劃分范圍的一種便捷方式,如“1000 到 2000 范圍內的 ADDR”。大多數邏輯分析儀還支持“not in range”功能。范圍是一種方便的快捷方式,因此您無需指定“ADDR >= 1000 and ADDR <= 2000”。

標志:標志是用于從一個模塊向另一個模塊發送信號的布爾變量。當某種情況在某一模塊中發生而稍后被另一模塊測試時可以設置標志。在下面的示例中,標志 1 用于跟蹤在模塊 1 的觸發序列中發生的情況,以便在模塊 2 中使用此信息。

模塊 1 的觸發序列:

1. If ADDR < 5000 then Set Flag 1 Trigger and fill memory

模塊 2 的觸發序列:

1. If DATA = 5000 and Flag 1 is set then Trigger Else if DATA = 1000 and not Flag 1 then Trigger

計數器:發生計數器用于想要查找事件的“第 N 次”出現的情況。例如,如果想在 ADDR = 1000 第 5 次出現時觸發,可以將觸發設置為:

If ADDR = 1000 occurs 5 times then Trigger

全局計數器類似于整數變量。全局計數器比發生計數器更靈活,因為它們可用于為復雜事件(例如一個時鐘沿后跟另一時鐘沿的事件)計數。可以增加、測試和重新設置全局計數器。默認情況下,全局計數器以零開頭并且不需要重新設置,除非已在觸發序列中使用了它們。一般情況下,如果可能的話,應使用發生計數器代替全局計數器,原因是發生計數器的用法比較簡單,而且全局計數器的數量有限。

定時器:定時器用于檢查事件之間消耗的時間。例如,如果想在出現一個時鐘沿后的 500 ns 內出現另一個時鐘沿的情況下引發觸發,請使用定時器。使用定時器時要記住的最關鍵一點是:先啟動定時器,然后再對其進行測試。換句話說,定時器無法自動啟動。設置定時器的關鍵是確定在何種情況下進行啟動和測試。

存儲限定:存儲限定用于確定應該存儲(即,存入內存)還是丟棄已獲得的樣本。這可以避免不需要的樣本占用邏輯分析儀內存。

設置存儲限定最簡單的方法是設置“默認存儲”。默認存儲表示“如果未經序列步驟指定,則進行存儲”。例如,可能只想在 ADDR 的范圍為 1000 到 2000 時存儲樣本,那么就應將“默認存儲”設置為:

ADDR In Range 1000 to 2000

默認情況下,“默認存儲”設置為存儲所有已獲得的樣本。也可以將“默認存儲”設置為不存儲任何樣本,這意味著除非某序列步驟覆蓋該默認存儲,否則將不存儲任何樣本。

序列步驟存儲限定意味著在某個特定的序列步驟內只存儲特定的樣本。這意味著在使用 Go To(轉到)或 Trigger(觸發)操作離開此序列步驟之前,應用該存儲限定。如果要為每個序列步驟應用不同的存儲限定,該存儲限定很有用。例如,可能不希望在 ADDR = 1000 之前存儲任何樣本,而對于其余的測量,只存儲 ADDR 在 1000 到 2000 范圍之內的樣本。

設置序列步驟存儲還需要再使用一條分支指令。例如,在查找 DATA=005E 時,如果只希望存儲 ADDR 在 5000 到 6FFF 范圍之內的樣本,某些情況下可使用以下序列步驟:

1. If DATA = 005E then Trigger Else If ADDR in range 5000 to 6FFF then Store Sample Go to 1 注意存儲樣本操作的使用。這表示“立即存儲內存中最新獲得的樣本”。而不 表示“從現在起,開始存儲”。應當注意,因為當 ADDR 不在 5000 到 6FFF 范圍之內時從不執行存儲樣本操作,所以該分支指令實質上是指“在此序列步驟中,只存儲 ADDR 在 5000 到 6FFF 范圍之內的樣本”。

上述示例似乎說明將只存儲 ADDR 在 5000 到 6FFF 范圍之內的樣本。但是,這取決于默認存儲的設置方式。還是使用上述示例,如果默認存儲設置為“Store Everything”(存儲所有樣本)并且有一個樣本不在 5000 到 6FFF 的范圍之內,則不會執行 Else If 分支指令,而應用該“默認存儲”。實際上,該序列步驟說明了樣本值在特定范圍內時要執行的操作,但沒有說明樣本值在此范圍之外時應執行的操作。因此,如果要明確指定序列步驟存儲,請使用以下指令:

1. If DATA = 005E then Trigger Else If ADDR in range 5000 to 6FFF then Store Sample Go to 1 Else If ADDR not in range 5000 to 6FFF then Don't Store Sample Go to 1 此外,如果默認存儲設置為“Store Everything”(存儲所有樣本),可以使用以下指令:

1. If DATA = 005E then Trigger Else If ADDR not in range 5000 to 6FFF then Don't Store Sample Go to 1

總之,序列步驟存儲總會覆蓋默認存儲,但只針對序列步驟存儲中特別指定的條件。處理默認存儲和序列步驟存儲之間的沖突時一定要謹慎。

雖然設置邏輯分析儀很困難,但觸發函數 可以大大降低此過程的難度。觸發函數是可以組合起來設置觸發的常用構建塊。由于這些函數涵蓋了大多數普通觸發,因此通過選擇適當的函數并將其填充到數據中即可設置觸發。下圖顯示了邏輯分析儀觸發用戶界面。請注意,觸發函數位于屏幕左側的一個醒目位置。

圖21 使用觸發函數

通常,設置復雜觸發的最大難題是對問題進行分解。換句話說,就是如何將復雜觸發映射到序列步驟、分支和布爾邏輯表達式。

1.將問題分解為不同時發生的事件。這些事件對應于序列步驟。

2.掃描觸發函數列表,嘗試找出一些與步驟 1 中確定的事件相匹配的函數。

3.將所有剩余事件分解為布爾邏輯表達式及其相應操作。各個布爾邏輯表達式/操作對分別對應于序列步驟中的一個單獨分支。請記住,可能存在只用于為序列步驟處理存儲限定的“存儲”分支。

設置邏輯分析儀觸發與編寫軟件大相徑庭。如果使用預定義的觸發函數和較早編寫的文檔完善的觸發來完成其他工作,就可大大降低設置邏輯分析儀觸發的難度。僅在沒有其他可用的資源時,才需要編寫自己的觸發設置。最后,當設置較難的觸發時,可將問題分解為若干較小的部分,然后逐個解決。

邏輯分析儀探頭

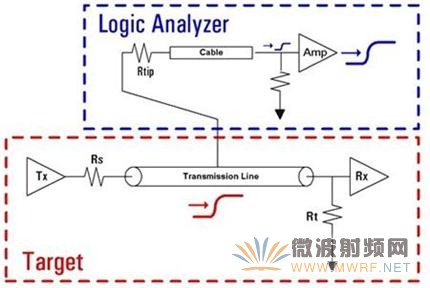

邏輯分析儀的探頭是邏輯分析儀非常重要的一部分。因為邏輯分析儀主要用于在線測量,探頭提供了與被測件的電氣和機械連接,當我們選擇探頭時,這兩個方面都是主要考慮因素。

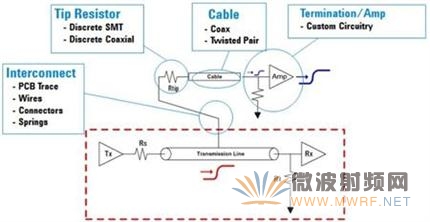

如下圖所示,探頭被動的觀察目標信號,目標信號的一小部分進入探頭,通過互連線纜傳遞到邏輯分析儀模塊,邏輯分析儀模塊里面的放大器把這一小部分信號放大,還原原始波形。

探頭的電氣性能主要考慮2個方面,這與示波器探頭的考慮因素是一致的。

1)不要干擾目標信號(探頭的信號完整性)

2)模塊內能夠較精確的復現被測信號(探頭的信號保真度)

圖22

探頭的結構細分下來也是比較復雜的。探頭與被測傳輸線接觸的小互連部分,可以使用PCB走線的方式,也可以使用導線,連接器或彈簧片,要根據實際情況選擇。探頭的前端包含電阻,有的是分立的SMT電阻,有的是分立電阻,一般阻值都在20k歐姆左右。探頭前端到模塊有長的電纜,已達到便于連接遠近目標的方便性,這些電纜可使用同軸方式或使用雙絞線方式,但都要保證足夠的帶寬。邏輯分析儀模塊需要對電纜的阻抗進行匹配,防止傳遞過來的信號反射回去,還要對信號進行放大,因為傳遞過來的信號幅度比較小。

圖23

探頭的負載效應主要分為兩種類型:直流負載和交流負載。

直流負載:探頭看起來象一個對地的直流負載,一般是20K歐姆。如果被測總線具有弱上拉或弱下拉特性(即上下拉電阻較大),這個負載可能會導致邏輯錯誤。直流負載主要由探頭尖的電阻決定,這個電阻阻值越大,直流負載越小,阻值越小,直流負載越大。

交流負載:探頭包含寄生電容和電感。這些寄生參數會減小探頭帶寬和導致信號反射。我們需要在被測電路接收端和探頭尖處考慮信號完整性。

探頭帶寬被降低主要來自2個方面:探頭電容和探頭與目標連接的連線的電容。

探頭導致信號反射的原因是4個方面:探頭電容和電感;探頭在被測總線上的探測位置;總線的拓撲結構;探頭和目標間連線的長度。

對于交流負載,我們需要考慮:探測點在傳輸線的位置,總線的拓撲結構和探頭和目標間連線的長度。

探頭的負載除了可以用復雜的Spice模型仿真分析外,也可以用簡單的RC模型簡單預估負載效應。下圖是典型探頭的RC模型。

圖24

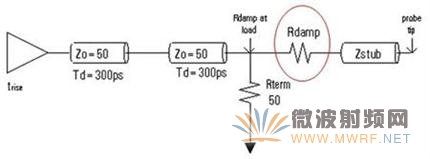

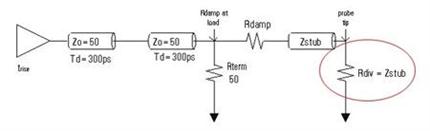

我們需要仔細考慮探頭和目標之間的連線。為了可靠的電氣連接,有三種方式可選擇:短線探測(Stub Probing),阻尼電阻探測(Damped Resistor Probing),電阻匹配探測(Resistive Divider Probing)。

短線探測會增加電容負載。舉例:探頭電容負載是0.7pF,連接短線是50歐姆微帶線(C=3pF/in),長度1英寸。則整個探頭的電容負載是3.7pF,這個短線是電容負載的主要部分。

被測系統可容忍的負載電容是多少呢?需要參考被測電路的系統上升時間,一般規則:短線的電氣長度<系統上升時間的20%。一個允許短線長度的計算例子:

PCB傳輸延遲:150ps/in

系統上升時間:500ps

則最大電氣長度:0.2x500ps=100ps

則最大短線長度:(100ps)/(150ps/in)=0.67in。

如果沒法減小短線長度,可以試著用阻尼電阻探測的方式。阻尼電阻有2個作用:隔離來自短線的電容,消減來自短線的反射。

圖25

阻尼電阻阻值大小的一般規則:目標阻抗的2.5倍。

如果探測環境需要更長的連線,這時候可考慮電阻匹配探測,即在探頭尖處附加一個匹配電阻,消除連線的反射。匹配電阻的阻值與連線傳輸線的阻抗一樣即可,但需要考慮信號的衰減。

圖26 電阻匹配探測方式

邏輯分析儀的探頭主要有3種類型:提前設計型;事后考慮型;定制型。

圖27 邏輯分析儀的探頭類型

小結:邏輯分析儀探頭是邏輯分析儀非常重要的部分,典型探頭的形狀,連接,參數如下圖所示。

圖28 邏輯分析儀探頭具體形狀和參數

作者:安捷倫科技專家 孫燈亮

參考文獻

[1] Agilent Technologies,Inc. Logic Analyzer Help System[G/DK].Santa Clara:Agilent Technologies,Inc.2012.

[2] Agilent Technologies,Inc.Logic Analyzer Probing Challenges,Considerations,and Options[R/DK].Santa Clara:Agilent Technologies,Inc.2010.

[3] Agilent Techlologies,Inc.Logic Anayzer Basic[G/DK].Santa Clara:Agilent Technologies,Inc.2008.

粵公網安備 44030902003195號

粵公網安備 44030902003195號