每個人都希望在各方面能獲得更多實惠:體積更小、功能更多、用電更少、封裝更好、成本更低,等等。特性越豐富,自然就越好,為了滿足這一要求,今天的離散解決方案就是明天的集成解決方案。這就意味著更小、更省電、成本更低、可靠性更高這些因素將推動市場的發(fā)展。集成與創(chuàng)新是制造商獲得市場成功所必須實現(xiàn)的關(guān)鍵目標。

目前,移動計算與通信設(shè)備很普通。數(shù)字電子技術(shù)的發(fā)展正是支持上述發(fā)展的驅(qū)動力,不過模擬電子技術(shù)發(fā)展也同樣重要,二者缺一不可。

數(shù)字 "以 2 為基數(shù)",也就是說信號不是一種狀態(tài)就是另一種狀態(tài),不是"開"就是"關(guān)",不是"真"就是"假",不是"1"就是"0",以此類推。

模擬信號在各種狀態(tài)中連續(xù)工作。模擬信號是世間萬物工作的方式,也是人類感官感知世界的方式。因此,要處理"現(xiàn)實"世界的光與聲等信號,就需要模擬信號處理。

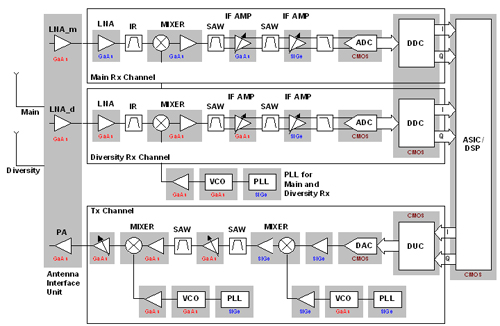

在蜂窩基站中,數(shù)字電子技術(shù)執(zhí)行許多復(fù)雜的功能,通常在軟件與固件控制下工作。而收發(fā)信號則需要模擬電子技術(shù)。數(shù)據(jù)轉(zhuǎn)換器用于將信號從一個領(lǐng)域轉(zhuǎn)換到另一個領(lǐng)域,即從數(shù)字轉(zhuǎn)換為模擬并從模擬轉(zhuǎn)換回數(shù)字。圖 1 顯示了發(fā)送 (Tx) 與接收 (Rx) 架構(gòu)以及目前常用的相關(guān)半導(dǎo)體工藝。

|

| 圖 1--基站收發(fā)架構(gòu)樣例 |

發(fā)送側(cè)架構(gòu)的基本功能是通過在 DSP(數(shù)字信號處理器)或 ASIC(專用集成電路)中運行"程序"生成數(shù)字域信號,隨后信號由被稱作 DUC(數(shù)字上變頻器)的專用數(shù)字電子設(shè)備進一步處理,再通過 DAC(數(shù)模轉(zhuǎn)換器)轉(zhuǎn)換為模擬信號,進行混合、過濾與放大,并通過天線發(fā)送。

接收側(cè)的過程剛好相反。天線接收的模擬信號通過模擬電子設(shè)備放大、混合并過濾,再通過 ADC(模數(shù)轉(zhuǎn)換器)轉(zhuǎn)換為數(shù)字。一旦成為數(shù)字格式,則信號首先由被稱為 DDC(數(shù)字下變頻器)的專用電子設(shè)備處理,然后再由 ASIC 或 DSP 處理。許多蜂窩基站制造商都力圖增強系統(tǒng)性能并降低尺寸與成本。有兩種方法實現(xiàn)上述目標,一是功率放大器(PA)的線性化,二是電子設(shè)備的集成,近期就將朝這兩個方向發(fā)展。

手機(手持終端)已成功地集成了收發(fā)功能。這也是基站設(shè)計的目標,不過基站所需的性能水平要高得多,因此現(xiàn)在要實現(xiàn)目標還很困難。

PA 線性化

為了滿足頻帶外傳輸規(guī)范要求,PA(功率放大器)在較高的 A 類上工作,效率低于 10%。這需要大型器件以及大量電能。為了優(yōu)化 PA 的尺寸與效率,我們正在開發(fā)線性化技術(shù)。最簡單的 PA 線性化方法之一就是降低波峰因數(shù)。降低波峰因數(shù)壓縮了信號"峰值"并降低線性操作所需的平均功率。它也向信號添加"噪聲",這樣所有可用的波峰因數(shù)降低約為 3dB,并仍可滿足 BER(位誤差率)的 EVM(誤差向量值)規(guī)范。不過,3dB 還是 3dB。

此外,PA 線性化技術(shù)更大的突破是可使信號預(yù)失真。預(yù)失真是 PA 線性化的"法寶",有望使 PA 效率優(yōu)于 25%。不過這也非常復(fù)雜,并要求了解 PA 失真特性--而該特性的變化方式非常復(fù)雜。該方法的基本思路是使 PA 預(yù)失真,這樣當傳輸信號經(jīng)過PA 時就不會失真,并滿足傳輸屏蔽 (mask) 的要求。挑戰(zhàn)在于 PA 的失真(即非線性)特性會隨時間、溫度以及偏壓 (biasing) 的變化而變化,因器件的不同而不同。因此,盡管能為一個器件確定特性并設(shè)計正確的預(yù)失真算法,但要對每個器件都進行上述工作在經(jīng)濟上則是不可行的。為了解決上述偏差,我們須使用反饋機制,對輸出信號進行采樣,并用以校正預(yù)失真算法。

集成:常見功能與常見技術(shù)

蜂窩基站的另一發(fā)展趨勢符合人們對電子技術(shù)的期待,也就是集成更多功能。集成的目的在于讓功能模塊變得更小,降低功耗,減少成本并提高可靠性。

集成通常采取的第一步就是將多個部件放在一個封裝中。因此,我們的分集接收機采用一個雙功能部件,而不是采用兩個 ADC。另一種方法就是集成使用相同工藝技術(shù)的功能。因此,放大器與混頻器可以集成在一起。

架構(gòu)發(fā)展是減少組件數(shù)量并提高性能的另一種方法。其實例之一就是使用正交調(diào)制器與解調(diào)器。

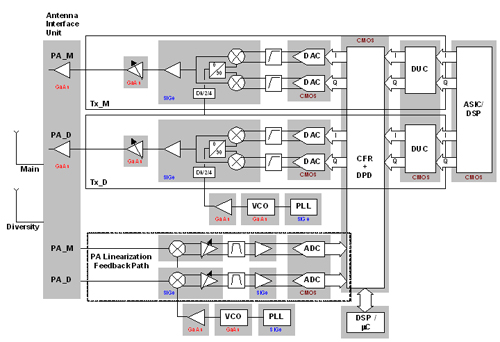

顯示了包括 PA 線性化集成度更高的發(fā)送器。在該例中,波峰因數(shù)降低技術(shù)(CFR) 與數(shù)字預(yù)失真 (DPD) 都借助 DSP 或微處理器 (μC) 控制集成到單芯片中。為了實現(xiàn)分集,我們使用兩條發(fā)送路徑,并在一個部件中集成了多個 DUC。可以看出,正交調(diào)制需要兩個雙 DAC,而放大器也組合到調(diào)制器中。發(fā)送信號的采樣在 PA 進行,并像上面介紹的那樣反饋用于線性化目的。這基本上是一個接收路徑,帶有集成放大器與混頻級,一個封裝中有兩個 ADC。

|

| 圖 2--帶有 PA 線性化的集成發(fā)送器 |

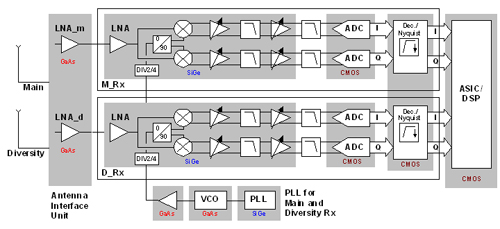

圖 3 給出了帶有分集接收機集成度更高的接收機。每個信道都集成了 LNA(低噪聲放大器),帶有正交解調(diào)器、濾波功能、可變增益以及雙 ADC。通過使用正交解調(diào),可用更簡單的 Nyquist 濾波器及抽選濾波器替代了 DDC 功能。

|

| 圖 3--集成的接收機 |

集成:數(shù)字與模擬

真正的挑戰(zhàn)來自在單芯片上混合數(shù)字與模擬功能。高頻數(shù)字邏輯會產(chǎn)生"噪聲","噪聲"通過電源、其他共用連接以及輻射狀的 (radiated) 路徑傳導(dǎo)。噪聲在模擬電路中至關(guān)重要,因為它決定著信噪比(SNR),而信噪比則是模擬系統(tǒng)中動態(tài)范圍的關(guān)鍵品質(zhì)因素。高性能數(shù)字意味著邏輯速度快,高性能模擬意味著動態(tài)范圍高,將兩者放置在同一 PCB(印制電路板)上需要很高的工程設(shè)計技巧,在芯片級上進行集成會更困難。

盡管先進的模擬電壓最近成功地從 12V 下降到 5V 與 3.3V,不過他們很難再降低,達到數(shù)字內(nèi)核電壓目前的水平。這是由于噪聲在工作電壓下降時不下降,因此模擬工作電壓必須保持在足夠的高度才能提供良好的 SNR。較低的電壓不足以提供高動態(tài)范圍模擬信號所需的性能空間。

最先進的數(shù)字工藝不包括高性能模擬組件。此外,最先進的數(shù)字工藝與最先進的模擬工藝之間在工藝特性尺寸上有很大差距。例如,德州儀器 (TI) 剛投產(chǎn)的最新型 DSP 采用了 C027 90nm 制造工藝,而 TI 最新高性能模擬工藝 HPA07 與 BiCom-III 則基于 350nm 的 CMOS 工藝。

模擬工藝的起點是穩(wěn)定的數(shù)字工藝。不管數(shù)字工藝晶體管提供什么線性功能,都作為片上模擬功能。即使如此,在工藝早期階段,我們的重點仍是數(shù)字;而模擬功能只限于那些不需要額外工藝步驟或修改的項目。一旦工藝成熟并成功制造最新系列的高速邏輯產(chǎn)品,則數(shù)字工藝開發(fā)人員接下來就會開始下一工藝節(jié)點的工作,模擬組件設(shè)計人員就會努力采用該工藝推出更高的模擬功能。開發(fā)與改進模擬組件需要時間。高性能模擬工藝推出的時間通常比基本數(shù)字工藝的投產(chǎn)要晚幾年。

TI 的 HPA07 與 BiCom-III 先進模擬工藝建立在 350nm CMOS 工藝基礎(chǔ)上,該工藝最初開發(fā)用于數(shù)字組件。因此,二者都有著廣泛的數(shù)字庫。基本 CMOS 工藝的電源要求與速度使其目前不適用于領(lǐng)先的 DSP 與 ASIC。同時,工藝的成熟也使模擬組件設(shè)計人員能夠推出高度專業(yè)化的工藝,可滿足各種不同終端設(shè)備應(yīng)用的不同產(chǎn)品需要。

HPA07

HPA07 精確模擬 CMOS 工藝為通信以及其他系統(tǒng)的低噪聲而設(shè)計,在上述應(yīng)用中,模擬與高速數(shù)據(jù)功能必須共存,并須盡可能減小信號干擾。該工藝有助于模擬集成,實現(xiàn)了良好的邏輯門密度、較好的模擬組件性能,并提供埋層隔離使模擬信號免受高頻數(shù)字電路的干擾。

HPA07 集成了 5V 與 3.3V 數(shù)字邏輯器件以及存儲器,并添加了專門用于模擬功能的晶體管與無源組件。該工藝經(jīng)過精心設(shè)計,符合噪聲、晶體管線性以及組件匹配與穩(wěn)定性方面的高性能標準。它極其適用于運算放大器、ADC、DAC、電壓參考與穩(wěn)壓器以及儀表放大器。HPA07 還可實現(xiàn)多達 40 個組件的靈活設(shè)計,同時還以相當少的屏蔽使成本保持在可控范圍之內(nèi)。

HPA07 CMOS 晶體管噪聲與失真都很低,它們采用掩埋信道 PMOS 技術(shù)制造,為此類器件實現(xiàn)了極高的增益帶寬/噪聲比。帶有很低溫度系數(shù)的激光微調(diào)硅鉻 (SiCr)薄膜電阻器可在整個工作溫度范圍內(nèi)實現(xiàn)穩(wěn)定性。晶圓的單獨處理可實現(xiàn) 16 位初始 (initial) 電阻器匹配,比業(yè)界典型情況多出四位。它還具有漏極擴展 (drain-extended) CMOS 晶體管,可為高振幅信號應(yīng)用處理高達 30V 的電壓。

此外,HPA07 提供了電壓系數(shù)提高 4 倍的金屬-絕緣體-金屬 (MIM) 電容器,并提供了高精度 TiN 聚合物 (TiN-Poly) 電容器、較厚的銅金屬路由層與存儲器。這些特性使模擬工藝能夠推出高精度集成產(chǎn)品。

OPA300 與 OPA301 只是該工藝生產(chǎn)的眾多產(chǎn)品中的最初產(chǎn)品而已。它們具有 150MHz 的單位增益帶寬、3nV/√Hz 的低電壓噪聲以及 30ns 內(nèi) 0.1% 的建立時間。OPA300 采用工作電壓為 2.7V (±1.35V) 至 5.5V (±2.75V) 的單電源供電,并具有關(guān)機功能,可將電源電流降低至 5μA,這對便攜式低功耗應(yīng)用非常有用。它們?yōu)轵?qū)動高速 SAR ADC 提供了低功耗單電源解決方案,同時還不影響性能。

BiCom-III

BiCom-III 是一種硅鍺 (SiGe) 工藝,為超高精度模擬集成電路而開發(fā)。它是一種電介質(zhì)絕緣的硅 (Si) 基工藝,并在基區(qū)加鍺 (Ge)。基區(qū)加鍺大大提高了載流子遷移率,實現(xiàn)了極快的瞬態(tài)時間。該工藝實現(xiàn)了真正互補的雙極 NPN 與 PNP 晶體管,傳輸頻率 (fT) 為 18GHz,最大頻率 (fmax) 為 40-60GHz。互補晶體管可實現(xiàn) AB 類放大器級,這對設(shè)計高速、高性能模擬電路至關(guān)重要。該工藝實現(xiàn)的速度是較早工藝的三倍。

高速模擬設(shè)計技術(shù)的其他優(yōu)勢在于:金屬-絕緣體-金屬 (MIM) 電容器電壓系數(shù)很低、電阻

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號