消費者使用移動裝置存取數據時,仍會因為下載速度過慢及圖形顯示效果不佳而感到不便。視頻博客及在線游戲等應用需要較快的連接速度及較短的延遲。更快速穩定的聯機有助于云端運算相關應用的開發,而且移動辦公室應用將不會因為硬件處理能力而受到限制。

在43億的無線網絡用戶中,大約有80%是單純使用語音的GSM用戶。因此行動系統供貨商十分看好未來5〜10年吸引30億的使用者申辦移動寬帶的成長商機。IPTV及數字相機等具有移動寬帶連接功能且可實現新型服務的裝置也可能帶來如此的成長,進而提高移動通信商的收益。

為應對愈來愈多的需求并且提供更快更穩的聯機及更短的延遲時間,全球網絡業者希望能夠建立4G網絡,而LTE是全球這方面的首例。

● LTE規格可提供超過100Mbps的最高下行鏈路(下傳)速率與超過50Mbps的上行鏈路(反傳),以及往返延遲低于10ms的無線電存取網絡(RAN)。

● LTE也運用波束形成(beam forming)等進階天線技術概念來擴大涵蓋范圍。透過多層天線解決方案可達到高尖峰數據速率,例如,2×2或4×4多重輸入與多重輸出(MIMO)。

雖然出現了具備所有絕佳功能的新標準,無線及行動網絡業者也必須持續面對投資成本及網絡建置的挑戰,以符合未來對于帶寬的激增需求。網絡業者必須針對4G選擇最符合成本效益的網絡演進。若要部署LTE等4G標準的網絡,所需的網絡升級不僅必須平衡新范圍有限的可使用性,也必須運用于現有范圍。為有效管理日益復雜的標準,分布式開放基站架構(Distributed open base station architecture)概念便隨著這些標準應運而生,以提供低成本、彈性的模塊化環境來管理無線電存取演進。

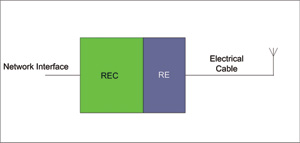

圖1a顯示的傳統基站部署需要將無線電設備控制器(REC)及無線電設備(RE)連同天線塔放入單一機殼中。如此的做法會使網絡業者在實際設置上面臨體積尺寸增大、功耗提高及成本增加等不利因素。這類架構也會使連接天線與RE的電纜出現信號耗損的狀況。

圖1a 傳統基站

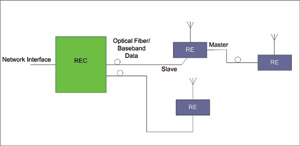

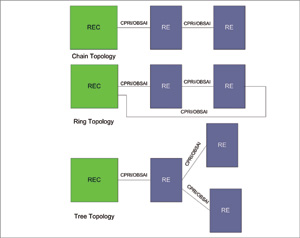

圖1b至1c顯示的分布式基站架構(DBSA)使得基站的其他部分完全不需要RF收發器。此架構能夠使RE的位置更接近個別的天線,以便將圖1b中介于RE與天線之間的電力損失減至最低,進而降低放大RF功率的成本。DBSA也允許各種不同的RE網絡拓撲,例如,圖1c所示的鏈狀、環狀或樹狀。如此的做法可確實縮小網絡設置的規模,因為無線電設備可彼此連接,并不需各RE對單一REC進行通信。

圖1b 分布式基站

圖1c 分布式基站拓撲

開放式基站架構創始聯盟(OBSAI)及通用公共射頻接口(CPRI)標準適用于無線電設備控制器及無線電設備之間的基頻數據通信,以及DBSA中的無線電設備網絡。將REC與RE之間的接口標準化之后,不同廠商的REC及RE設備即可交互使用。同時,2G/3G/4G的REC 能夠與不同的RE進行通信,因此可實現多種標準的結合與同時運作,并減少設備升級的需求。

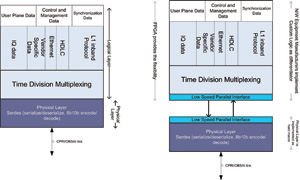

CPRI及OBSAI均載明其無線電設備控制器及無線電設備之間的高速串行接口,以達到基頻數據傳輸(I/Q數據),并且在相同接口進行指令/控制與同步(用于RE網絡)信息的溝通。

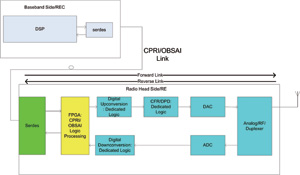

圖2顯示DBSA中的信號流向。對于上傳(foward link)的RE,OBSAI/CPRI資料是由序列器/解除序列器(SerDes)所還原,其中會將高速序列數據轉換為平行數據,然后將此數據傳輸至FPGA。FPGA會處理OBSAI/CPRI邏輯,然后將I/Q基頻取樣傳輸至數字升壓轉換器(專用邏輯),進而將I/Q基頻取樣調節至數位IF載波。經過向上轉換的數據會接著經過數據處理引擎的處理,以減少波峰系數(專用邏輯),并且以數字方式將信號預失真(專用邏輯),以補償功率放大器中產生的旁瓣(side lobe),并確保功率放大器能夠在線性區域中運作。

圖2 分布式基站架構信號流向

在上行鏈路中,無線射頻模塊包含所有的模擬功能,能夠將RF頻帶向下轉換為中頻,然后以數字方式將個別載波向下轉換為取樣的基頻同相及正交(I/Q)組。經過多任務處理的基頻取樣(I/Q)以及下傳與反傳中的控制及管理數據會被串行化,然后透過SerDes裝置(例如,德州儀器的TLK3134)以光纖纜線進行傳送。

若想借由分析4G演進方面的DBS以及所需突波來達到更快更穩定的數據聯機,則會引起另一個重要問題。由于下行鏈路及上行鏈路的數據速率提升,而且愈來愈多的網絡申辦用戶轉而使用隨選電視等高帶寬應用,因此,REC與R之間的序列數據速率也隨之增加。使用公式(1)可算出REC及RE之間的序列數據速率(SDR):

SDR=MAcSN2(I/Q)C (1)

其中,SDR是REC與RE之間的序列數據速率;M為天線數目;Ac為載波/天線數目;S為采樣率(各載波每秒取樣次數);N為取樣寬度,位/取樣;C為REC與RE之間串行傳輸期間的8b10b數據(10/8=1.25);2(I/Q)=2倍的同相及正交相位資料的倍增系數。

透過等式1及表1,對于4個W-CDMA載波、雙天線系統,采樣率為各載波每秒7.68百萬次取樣,I-Q取樣寬度為 4b/sample的20MHz無線射頻而言,其原始序列速率如式2所示:

SDR=2×4×7.68×4×2×1.25= 614.4Mbps (2)

同樣地,透過式1及表1,對于四天線系統、單一載波/天線,LTE 載波采樣率為各載波每秒30.72百萬次取樣,I-Q 數據取樣寬度為16b/sample的20MHz無線射頻而言,其原始序列速率如式3所示:

SDR=4×1×30.72×16×2×1.25=4.915Gbps (3)

對于八天線波束形成LTE系統而言,式3中的SDR會倍增為9.8Gbps。因此,I-Q取樣寬度、信道寬度或天線載波數目的增加會直接造成REC與RE之間序列數據速率的提高。搭建基礎架構的網絡設備制造商應該要了解,在LTE演進中,序列數據速率必須從614.4Mbps的中等速率調整為9.8Gbps或12.2Gbps。DBSA的高SDR需要光纖纜線兩端的SerDes發揮更高的效能,才能達到穩定的頻率數據復原,并符合CPRI或OBSAI標準的抖動規格。為了進一步了解4G的SerDes及數據處理效用,以下將分析CPRI/OBSAI的通信協議堆棧。

圖3a顯示CPRI通信協議層堆棧。一般而言,物理層包含不同通信協議都具備的固定功能。CPRI/OBSAI通信協議層的固定功能物理層是以硬件宏(hard marco)的方式進行實作,以達到嚴格的時序閉合需求。然而,邏輯層則允許客制化。由于新興的標準演進,以及網絡設備制造商期望透過專屬功能建立附加價值,使得邏輯層會隨之更新。在實作CPRI/OBSAI接口的邏輯層部份時,FPGA通常會提供所需的彈性。FPGA的邏輯項目能夠利用程序加以設計,以支持自定義的邏輯層。

圖3a CPRI通信協議層堆棧

圖3b CPRI通信協議層堆棧(外部SerDes劃分)

由于網絡設備制造商改采4G部署,因此不僅需要相同彈性來實行邏輯層,也需要強化SerDes效能來滿足增加的 SDR。網絡設備制造商可選擇采購已整合SerDes的FPGA,或選擇采購FPGA與離散式SerDes,然后將兩者結合(見圖3b)。

以下是選擇離散式SerDes-FPGA及整合型SerDes-FPGA時必須考慮的幾項關鍵因素:

● 離散式SerDes加上FPGA的成本VS已整合SerDes的FPGA成本

● 離散式SerDes的效能VS整合于FPGA的SerDes效能

● 對于特定FPGA平臺的熟悉程度

● 改用整合型SerDes-FPGA所節省的空間

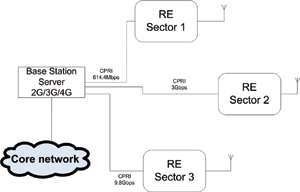

圖4顯示2G/3G/4G基站或REC連接到分別服務3個區塊的3個RE。其中,3個CPRI設定分別為614.4Mbps、3Gbps及9.8Gbps線路速率,并假設9.8Gbps為更新過后的SDR,可支持4G。

圖4 連接到3個RE的2G/3G/4G REC

狀況A:假設網絡設備制造商使用FPGA與離散式SerDes,而且已經在該特定FPGA平臺的學習周期中投入時間與資源。若要在此狀況下支持9.8Gbps:

● 制造商將SerDes升級,并持續使用同一個熟悉的FPGA平臺。優點:達到規模效益,因為圖4顯示的3個RE區塊都能具備類似的FPGA,同時以不同的SDR進行運作。如此一來,制造商便不需要變更FPGA平臺而經歷學習周期。

狀況B:網絡設備制造商使用已整合SerDes功能的經濟型低階FPGA。若要在此狀況下支持9.8Gbps,制造商有3種選擇:

● 改用不同制造商的9.8Gbps高階FPGA(已整合SerDes)。缺點:成本增加,而且制造商必須經歷新FPGA平臺的學習周期。

● 改用相同制造商的低價9.8Gbps FPGA(已整合SerDes)。缺點:效能疑慮。

● 向同一個廠商購買不含SerDes的FPGA,并將系統切割為FPGA以及離散式SerDes。優點:制造商改用不含SerDes的FPGA可以節省成本,同時保留熟悉的FPGA平臺。此外,使用相同的FPGA可切割出采用離散式SerDes的3個RE區塊,進而達到規模效益,就如圖4所示。缺點:離散式SerDes加FPGA的解決方案可能需要更多的PCB空間。

狀況C:網絡設備制造商使用已整合SerDes的高階FPGA。若要在此狀況下支持9.8Gbps,制造商有3種選擇:

● 改用相同制造商的9.8Gbps FPGA(已整合SerDes)。缺點:制造商可能必須為具備9.8Gbps SerDes功能的FPGA付出相當高的成本。

● 改用不同制造商的9.8Gbps低階FPGA(已整合SerDes)。缺點:學習周期、效能疑慮、缺乏降低成本的規模效益。

● 向同一個廠商購買不含SerDes的FPGA,并將系統切割為FPGA及離散式SerDes。優點:與狀況B類似。

在9.8Gbps或12Gbps等高SDR的情況下,要滿足離散式SerDes設計中對于穩定頻率數據復原、抖動容差、信號調節及信號完整性的需求已經相當不容易,更不用說在整合型SerDes-FPGA設計中,數字邏輯項目區塊(芯片的大部份)內敏感模擬電路的噪聲隔離會造成設計上更大的挑戰。有時候,為達到所需的效能,已整合SerDes的FPGA需要高成本的電源供應濾波,并選擇使用電壓控制的晶體振蕩器或成本較低的晶體振蕩器。這些需求會增加實施的成本。概括來說,將SerDes整合于FPGA會造成相關的成本,而且當整合難度因為SDR升高而增加時,這些成本也會增加。這正是為何當數據速率在3Gbps或更低的狀況下,FPGA加離散式SerDes的解決方案比整合型解決方案更符合成本效益的一個主要原因。

結論

當網絡設備制造商建置4G的基礎架構時,對于分布式基站架構部署中無線電設備控制及無線電設備之間的高序列數據速率需求將大幅升高。要滿足如此需求,光纖纜線兩端的SerDeson必須發揮更高的效能。網絡設備制造商可將系統切割開來,便能使用同一個熟悉的FPGA平臺進行邏輯層處理。為達到高序列數據速率,網絡設備制造商可改用離散式 SerDes 解決方案,單獨就SerDes部份進行升級。如此的切分可達到所需的效能而不必采用新FPGA平臺所需的學習周期,并且有助于提升規模效益,最終能降低制造商的成本。

粵公網安備 44030902003195號

粵公網安備 44030902003195號