作者:LauroRizzatti

VSORA是一家法國巴黎的DSP設計工具公司,推出了一種高效5G寬帶新型設計架構,迅速從5G和AI的芯片開發中脫穎而出。近日,創始人兼首席執行官KhaledMaalej和我談到了VSORA的多核數字信號處理(DSP)知識產權(IP)以及5G和AI應用程序的開發流程。

Maalej和vsora的創始人都來自巴黎的Dibcom(2013年被Parrot收購),該公司為全球領先的低功耗移動電視和無線電接收芯片設計公司。在DiBcom期間,他們注意到高帶寬基帶系統的技術并沒有得到充分發展和提升。他們認為,由于非常不合理的開發流程上的缺陷,往往造成算法工程師和DSP開發人員之間形成一個耗時的反復推翻的因境,大大地拖延了研發周期。

Maalej解釋說算法工程師在MATLAB環境中設計一種算法。一旦他們相信他們的建模將提供了令人滿意的結果,他們就會固化算法,并將其交給DSP開發人員來實現。DSP小組將花費幾個月的時間對算法進行徹底的RTL設計驗證。

“在這個階段,就可能碰到麻煩”Maalej說。首先根據目標規格對DSP設計的總體性能即速度、面積和功耗進行測試,然后DSP開發人員將其交給寬帶系統工程師和嵌入式軟件開發人員,以便在寬帶系統設計中進行部署。當總體性能不符合規范時,研發流程則退回到算法工程師,由算法工程師必須對算法進行再次修正,重新與DSP硬件開發人員之間進行設計迭代。

其結果往往是推遲了寬帶設計的發布,增加了無法實現最優化設計的風險。

Maalej指出:“DSP已經存在了幾十年,而這些缺陷還沒有在設計流程中得到有效解決。”目前的DSP技術沒有提供足夠的處理能力去滿足現今高帶寬系統的需求,例如5G無線應用程序。設計者不得不在可編程DSP周圍添加DSP協處理器,通過增加硬件方式系統去實現算法。如果設計人員沒有在產品規化時為應用程序提供足夠的電力,或者功耗超過預計的設計值 ,則必須對其進行修改以滿足要求,通過迭代以增加處理能力和降低功耗。

VSORA通過基于多核信號處理器(MSP)的方法,改變DSP硬件設計方案來提供高效的處理能力并降低功耗,增加其可編程的靈活性。

Maalej確信“為了應對大數據的復雜算法,比如應對5G寬帶的設計要求,功耗的增加是肯定的” 。VSORA的MSP集成了一個信號管理器來處理硬件中的三維信號矩陣,使用高帶寬存儲器,以確保嵌入式算術邏輯單元(ALU)得到充分利用。此外,在單個時鐘周期中可執行的大量指令加上對每個周期多條指令的支持,以此增加了MSP的處理能力和效率。

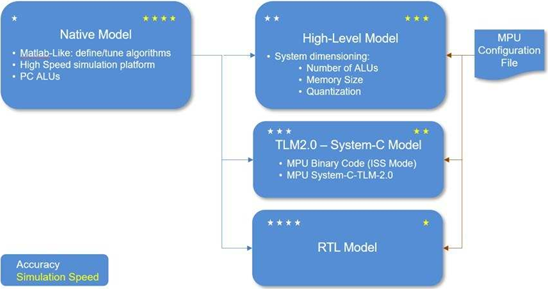

這個開發流程無需生成底層運算代碼,方法是將源代碼保持在由算法工程師創建的類似matlab語言的格式中。VSORA MSP開發流程自動將源代碼編譯為在MSP上運行的二進制格式。因此研發者可以輕松地評估算法的速度、面積和功耗。

因此,從算法工程師即可開始控制開發流程,充分展示最終產品的規格。系統成本優化取決于所選擇的算法,在項目開始時即可進行評估。算法工程師可以分析不同算法帶來的成本,并根據需要重新調整或修改算法,從而簡化復雜系統的研發流程。

新的MSP開發流程可以將信號處理代碼和系統嵌入式軟件代碼混合到相同的文件中,供寬帶系統工程師和算法工程師交互討論,系統工程從算法設計開始即可介入項目,以此減少失誤和開發節點之間反復。

Maalej說:它類似于軟件開發流程。通過從開發流程中排除DSP硬件實現,并讓算法工程師完全控制流程,該流程與軟件流程相當相似,使其更快、更高效、更便宜。

“復雜的系統不能被集成到單一的核”他補充說。MSP允許算法工程師選擇每個任務的內核數和每個處理器的大小,決定每個核心的ALU數以及計算精度。

VSORA的DSP開發流程類似于軟件工程師使用的開發流程。

在問及將5G和AI應用程序集成到MSP的復雜系統有多困難時,Maalej說:“一般來說,算法工程師不熟悉技術最終應用場景。這就是我們簡化了開發流程并將系統工程從開始即介入的原因,允許他們以一種簡單的方式執行實現。他們不需要改變他們的系統模擬去嘗試不同的硬件配置,或者改變內核的數量,例如,從三個到四個核。在VSORA設計流程中只需要用兩行簡單代碼中的一行即可進行硬件分配。“

新興的5G無線網絡具有大數據高速率、低延遲、低功耗、低成本、提高系統容量和大規模設備連接的特點。因此,一個更高效的流程來支持DSP開發,以確保5G的成功是非常重要的。

粵公網安備 44030902003195號

粵公網安備 44030902003195號