精密頻率合成技術(shù)助力多通道頻率合成器的應(yīng)用

直接數(shù)字頻率合成(DDS)在過去十年受到了頻率合成器設(shè)計工程師極大的歡迎,它被認為是一種具有低相位噪聲和優(yōu)良雜散性能的靈活的頻率源,基于DDS的頻率合成器在許多應(yīng)用中能比基于鎖相環(huán)(PLL)頻率合成器有顯著的優(yōu)勢。這些優(yōu)勢包括亞赫茲頻率控制分辨率,相位失調(diào)和輸出幅度控制,以及無需基于PLL頻率合成器設(shè)計所需要的外部元件。另外,作為一個基于數(shù)字的波形發(fā)生器,其頻率、相位和幅度的改變可以通過一個簡單的可編程端口來實現(xiàn)。這種能力允許DDS技術(shù)用于多種民用和軍事應(yīng)用中,包括那些要求復(fù)雜的多通道同步的應(yīng)用,例如,雷達、聲光濾波和基帶上變頻。

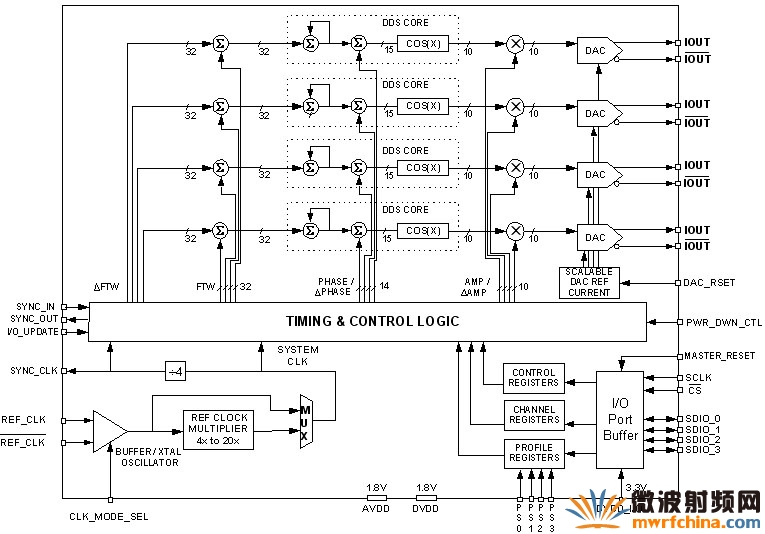

隨著ADI公司的AD9959四通道10 bit 500MHz DDS和AD9958雙通道10 bit 500MHz DDS產(chǎn)品的推出,多通道同步設(shè)計從來沒有這樣容易。AD9959在一顆芯片上集成了四個完整的DDS通道*,它為頻率合成器設(shè)計工程師需要四個通道的應(yīng)用提供一個單片解決方案。除了單片AD9959具有四個獨立的DDS通道之外,通過使用特別適合于自動同步多片AD9959的專用引腳有助于同步多片AD9959,這可以很容易地實現(xiàn)多個通道的同步。AD9958是與AD9959 具有相同特性和性能指標的雙通道器件。圖1示出AD9959產(chǎn)品的框圖。

* 一個完整的DDS通道由數(shù)字波形發(fā)生器、數(shù)模轉(zhuǎn)換器(DAC)和專用控制邏輯電路組成。如果不能展示框圖,應(yīng)當(dāng)給出定義。

圖1. AD9959 四通道DDS框圖

利用正交信號的單邊帶上變頻

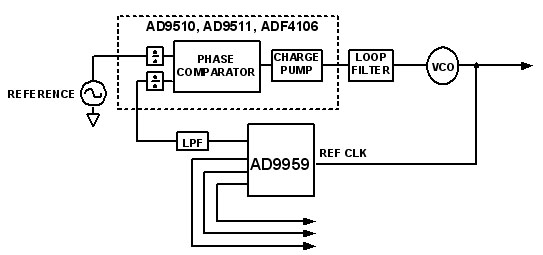

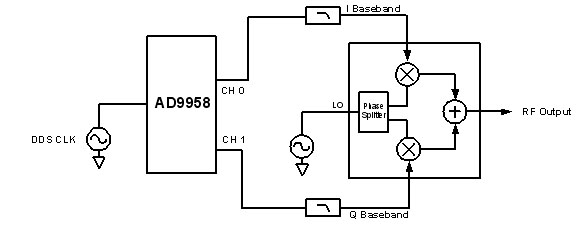

盡管DDS技術(shù)能提供優(yōu)良的頻率和相位控制特性,但為了在甚高頻(UHF)或微波頻段利用這些特性,還需要上變頻。通常采用多種上變頻方法。其中一種方法是利用PLL反饋環(huán)路中的DDS進行上變頻(見圖2),這種方法有受一些限制,但通過一種采用兩個正交的DDS通道來抑制邊帶能量的設(shè)計配置(見圖3)能夠突破這些限制。

圖2.利用PLL反饋環(huán)路的DDS進行上變頻

圖3.利用正交信號進行單邊帶上變頻的框圖

在圖2的電路設(shè)計中,DDS的許多優(yōu)勢受到PLL的限制。例如,DDS的快速跳頻能力受到PLL的鎖定時間的限制。另外,在PLL的環(huán)路帶寬內(nèi),來自DDS的任何雜散或相位噪聲都被放大并且傳遞到PLL輸出。由于這些原因,這種體系結(jié)構(gòu)通常被限制在產(chǎn)生單音或以較低帶寬傳輸工作的系統(tǒng)。

使用一個混頻器級對兩個DDS正交通道實現(xiàn)的單邊帶上變頻的設(shè)計體系結(jié)構(gòu)(圖3)是一個優(yōu)秀的案例,其中的兩個DDS通道具有獨立的相位和幅度控制,所以非常適合以較高數(shù)據(jù)速率工作的系統(tǒng)。利用這種方法,保持了快速跳頻,從而允許更快的數(shù)據(jù)速率傳輸。使用混頻器實現(xiàn)上變頻信號的主要擔(dān)心冗余邊帶的產(chǎn)生,因為它給濾波器設(shè)計帶來困難或不能濾波。通過使用DDS發(fā)送正交信號到一個模擬正交混頻器的同相(I)和正交(Q)輸入端,可顯著衰減冗余的邊帶,這樣將濾波器的設(shè)計要求降至最小。

AD9959/58每個通道的頻率、相位和幅度都可以被獨立的控制。這種靈活性可用于校正正交信號之間由于模擬信號處理〔例如,濾波、放大或印制電路板(PCB)布線相關(guān)的不匹配〕造成的不平衡。由于所有通道共享一個公共的系統(tǒng)時鐘,它們具有固有的同步性,從而無需以前的同步多個器件的設(shè)計要求。另外,利用單芯片解決方案,從根本上消除了存在于兩個分立器件之間的溫度效應(yīng)。

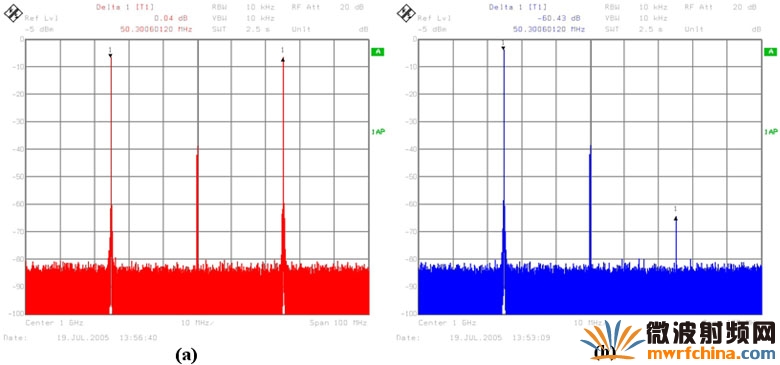

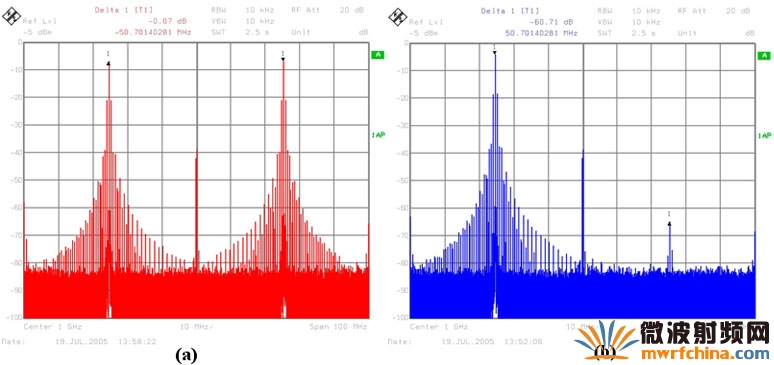

實驗室結(jié)果表明,AD9959/58器件能夠?qū)崿F(xiàn)優(yōu)于-60 dBc的冗余邊帶抑制能力。圖4中的兩條曲線圖示出一個25 MHz 單音信號上變頻到975 MHz的結(jié)果。當(dāng)采用來自AD9959的兩個正交信號時,對上邊帶的抑制效果如曲線(b)所示。圖5示出頻移鍵控(FSK)編碼數(shù)據(jù)的結(jié)果,其中曲線(a)沒有采用來自AD9959的正交信號,而曲線(b)采用了。應(yīng)當(dāng)注意的是,當(dāng)使用模擬正交混頻器結(jié)構(gòu)時,可能會產(chǎn)生本振頻率的饋通。在圖4和圖5中沒有表示出將饋通減至最小的實驗結(jié)果。

圖4 (a)上變頻單音頻譜,未采用正交信號;(b)上變頻單音頻譜,采用正交信號

圖5 (a)上變頻FSK編碼數(shù)據(jù)頻譜,未采用正交信號; (b)上變頻FSK編碼數(shù)據(jù)頻譜,采用正交信號

多通道DDS雷達應(yīng)

早期的雷達系統(tǒng)傳統(tǒng)上完全由模擬電路組成。近來,雷達設(shè)計工程師已經(jīng)采用既減少成本而又增加系統(tǒng)功能的數(shù)字技術(shù)。DDS技術(shù)現(xiàn)在常見于雷達系統(tǒng)設(shè)計中。DDS最吸引雷達系統(tǒng)設(shè)計工程師的特性是精密頻率控制、相位失調(diào)控制和線性調(diào)頻能力。通常包含DDS器件的兩種基本類型的雷達是脈沖雷達和調(diào)頻連續(xù)波(FMCW)雷達。最近的研究結(jié)果表明,許多雷達系統(tǒng)使用多個DDS通道,這些通道要求彼此同步。這種同步的要求也包括對每個DDS器件提供適當(dāng)?shù)臅r鐘分配。

在一些脈沖雷達中,發(fā)射元件(天線)的數(shù)量可從幾個到上百個或更多。天線制作成一個陣列形式,習(xí)慣用電子的方式控制發(fā)射的雷達射束。這種天線被稱為“相陣雷達”。對于陣列中每個單個的天線,都分配一個DDS 通道,并且其相位的調(diào)整是射束控制的機制。在所有何情況下的射束控制都使所有DDS通道以相同的輸出頻率工作,因此利用相位偏移特性完成射束控制任務(wù)。

FMCW雷達使用相陣天線比脈沖雷達更為困難。在這種配置中,射束很難控制 ,因為當(dāng)發(fā)出信號線性調(diào)頻信號時要求不斷地改變相位差。要克服這種困難,必須在線性調(diào)頻率期間對每個FMCW 信號進行相位調(diào)整。為作到這一點,需要提供一個匹配的等待時間開關(guān)以便允許頻率、相位和變化幅度同時發(fā)生變化。在前面的DDS設(shè)計中,當(dāng)這些參數(shù)同時變化時不能在DAC的輸出端同時顯現(xiàn),由于其內(nèi)部波形發(fā)生器的管道級延遲效應(yīng)。

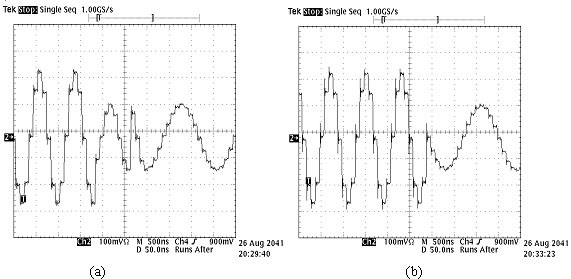

圖6示出一個管道匹配的DAC輸出和一個非管道匹配的DAC輸出之間的差別,其中頻率和幅度相差一半并且相位變化180°。曲線(a)清楚地示出幅度在相位之前變化,頻率在相位之后變化。在曲線(b)中,管道匹配開關(guān)允許,DAC輸出同時改變頻率、相位和幅度。應(yīng)當(dāng)注意:為了更好地示出等待時間匹配的影響,曲線顯示的是未經(jīng)濾波的DAC輸出,這就是為什么其輸出呈現(xiàn)“階梯”狀的原因。

圖6 (a)管道延遲匹配開關(guān)禁止; (b)管道延遲匹配開關(guān)允許

同步多個AD9959/58器件

最近研究結(jié)果表明,50%以上的所有基于DDS的設(shè)計采用了多通道,并且?guī)缀?5%的多通道系統(tǒng)都要求通道之間同步。另外,幾乎15%的多通道系統(tǒng)都需要四個以上的通道。為了支持這些需要四個以上通道的系統(tǒng),AD9959/58產(chǎn)品包含了能夠使多個AD9959/58器件相互之間自動同步的電路。

當(dāng)所有器件內(nèi)部時鐘發(fā)生狀態(tài)機的狀態(tài)都相同時,就認為多個器件是同步的,從而使每個器件的SYNC_CLK輸出引腳都產(chǎn)生相互相同的相位。多個器件同步可通過將主器件的SYNC_OUT輸出引腳簡單地連接到從器件的SYNC_IN輸入引腳實現(xiàn)。通過串行端口設(shè)置bit位,可將器件配置為主器件和從器件。

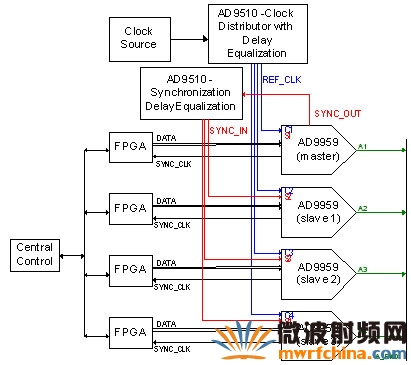

圖7示出一種用于同步多個AD9959/58器件的典型配置。

圖7. AD9959/58多芯片同步設(shè)置框圖

參看圖7,來自主器件的同步脈沖發(fā)送到AD9959/58芯片外的“同步延遲平衡”電路,目的是將這個脈沖同時分配到從器件的SYNC_IN引腳。從器件從主器件采樣同步脈沖并且將時鐘發(fā)生狀態(tài)機的當(dāng)前狀態(tài)和一個 “期望”值作比較。如果從器件的時鐘發(fā)生狀態(tài)機與期望值比較的結(jié)果正確,那么從器件就是同步的。如果從器件的時鐘發(fā)生狀態(tài)機和期望值不同,那么從器件就將時鐘發(fā)生狀態(tài)機延遲一個系統(tǒng)時鐘周期。只要器件配置為同步,這個采樣、比較、執(zhí)行的過程就會連續(xù)進行。那就是說,如果從器件由于基準時鐘輸入暫時不穩(wěn)定而不同步,一旦基準時鐘達到穩(wěn)定,從器件會自動重新與主器件同步。

敏銳的讀者可能會考慮到,在高系統(tǒng)時鐘速率條件下,很難在一個系統(tǒng)時鐘周期內(nèi)將同步脈沖從主器件傳送到從器件。為了便于在高速率下同步,允許用戶設(shè)置從器件,以期望在主器件產(chǎn)生同步脈沖后延后1~16個系統(tǒng)時鐘周期。這可以通過串行接口以增量方式對從器件進行設(shè)置實現(xiàn)的,即設(shè)置期望產(chǎn)生的外部傳播延遲的周期數(shù)。這種特性的另一個好處是每個從器件可設(shè)置不同的 “期望狀態(tài)”,它允許在同步脈沖分配電路中有較大的容許誤差。

除了自動同步方式以外,AD9959/58還提供手動同步方式,直接由用戶控制。硬件和軟件手動同步方式都可提供。硬件手動同步方式允許用戶將器件時鐘發(fā)生狀態(tài)機對于在SYNC_IN引腳上檢測到的每個上升沿(邏輯值 1)延遲一個系統(tǒng)時鐘周期。在軟件手動方式中,可通過串口寫入一個專門的控制位(bit),使該器件時鐘發(fā)生狀態(tài)機延遲一個系統(tǒng)時鐘周期。在單個系統(tǒng)時鐘周期步長中,時鐘發(fā)生狀態(tài)機延遲一個系統(tǒng)時鐘周期具有改變系統(tǒng)時鐘和SYNC_CLK輸出信號之間相位關(guān)系的作用。

通道之間的隔離性能

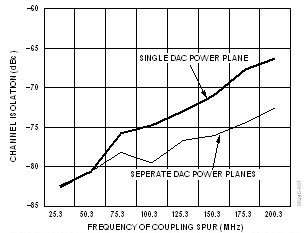

多通道系統(tǒng)的一個關(guān)鍵指標是通道之間的隔離。沒有正確的隔離,交流(AC)性能會顯著變差,負面地影響性能。圖8示出AD9959典型通道隔離性能的實驗室結(jié)果。在四個通道上進行測量,其中一個通道產(chǎn)生110.3 MHz 固定頻率,而其它三個通道在25 MHz~200 MHz頻率范圍內(nèi)掃描。在110.3 MHz頻率下的通道具有的功率電平與泄漏到其它通道的功率電平之差就是通道之間的隔離度。對于所有可能的情況,記錄下優(yōu)于-65dBc的測量結(jié)果。兩通道AD9958器件在相同測試條件下其通道隔離度提高-6dBc。

圖8 在500MSPS工作條件下的通道隔離,要測試的通道固定在110.3MHz,其他通道以25MHz增量進行頻率掃描

其它特性

盡管本文集中于AD9959/58的多通道能力,但是重要的是應(yīng)該注意到以前ADI公司DDS 產(chǎn)品的許多典型特性在AD9959/58中已經(jīng)包含或得到提高。例如,通過用于頻率、相位和幅度值的四個數(shù)據(jù)引腳和存儲單元,AD9959/58產(chǎn)品支持2,4,8或16級FSK,PSK或ASK調(diào)制。雷達應(yīng)用可利用該器件以可設(shè)置的速率和步長線性地掃描頻率、相位或幅度的能力。芯片內(nèi)還包括一個可編程的基準時鐘倍頻器,能接受10 MHz~125 MHz范圍內(nèi)的單端或差分輸入,以便提供500 MHz 速率的最大系統(tǒng)時鐘。SPI兼容的串行可編程口工作頻率達到200 MHz。為了進一步提高編程速度,這個端口還可進行配置,以便每串行時鐘周期接受2 bit或4 bit 數(shù)據(jù)。最后,四個DAC都可設(shè)置以獲得獨有的滿量程電流。

結(jié)論

AD9959/58器件現(xiàn)在可大批量提供,采用小型的7 mm×7 mm 56引腳LFCSP封裝。其評估系統(tǒng)可通過一個USB端口連接到一臺個人計算機(PC),為評估AD9959/58產(chǎn)品構(gòu)成一個用戶友好的平臺。該評估系統(tǒng)包括一塊硬件評估板和一個基于Windows的軟件包,使用戶能夠非常快速和準確地設(shè)置器件,而無須串口協(xié)議或寄存器等級定義方面的詳細知識。

作者:David Brandon,應(yīng)用工程師,ADI公司;John Kornblum,設(shè)計工程師,ADI公司

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號