輸入、輸出電容設計考慮:

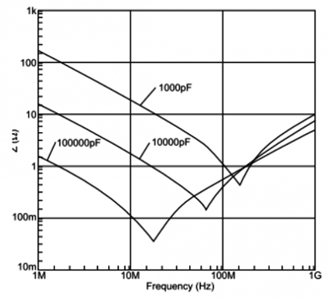

從圖14 中可以看到輸入電容為1nF 和10uF 組合,這樣做的原因是可以濾除不同頻率的噪音,輸入端噪音可以來自兩個部分:第一,來自于輸入端電源總線上的噪音,比如總線還給其他負載供電,而這些負載的電源也是來自于DC-DC 變換器,因此在電源總線就會疊加非常豐富的噪音;第二,來自于LM3242的自身開關噪音,它的開關噪音同樣會疊加在輸入端,因此可能會干擾總線上的其它負載芯片,所以實際設計時,入口還會需要更多不同容值的電容才可以滿足濾除不同噪音頻率的要求,比如10pF 或者100pF的電容也會用到,不同容值的電容所針對的最佳濾除頻率也是不一樣的,對于大容量的電容來說它可以濾除的頻率范圍相對來說窄一些,因為它的拐點頻率比較低,在拐點頻率之內,電容的阻抗是呈下降趨勢,也就是表現的是容性特質,但是拐點頻率之上,阻抗是呈上升特性,則表現的是電感特性,因此不再具有濾波作用,這也就是需要搭配不同容值電容的原因所在,因為噪音頻率非常豐富,一種容值的電容是不可能把寬頻帶的噪音全部濾除掉,另外還要注意同等容值、同等耐壓的小尺寸的電容表現出來的容性帶寬更寬一些,這主要是小尺寸的電容它的內部寄生電感量更小一些、同時它的有效容量更低一些,因此表現出來的特性就是濾除噪音的帶寬更寬一些,從圖中可以看出小容量但是尺寸更小的01005 封裝的電容,它可以濾除的噪音頻帶更寬。

圖15、電容阻抗和頻率關系圖

輸出電感設計考慮:

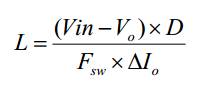

功率電感的計算,一般可以參照下面公式進行計算

Vo………………………..輸出電壓

D………………………….Vo/Vin

Fsw………………………開關頻率,比如LM3242,開關頻率是6MHz

ΔIo……………………….電感內部的紋波電流,可以取(0.2~0.5)Io

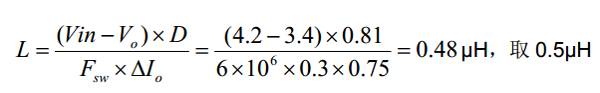

設計范例:

Vin=4.2V,Vo=3.4V,Io=0.75A,ΔIo=0.3*Io,Fsw=6MHz,D=3.4/4.2=0.81

則:

從公式中可以看出來,紋波電流越小則電感量就會越大,越小的紋波電流則在輸出電容上產生的紋波電壓就會越小(紋波電壓=輸出電容的ESR*紋波電流),但是電感的尺寸會變大,不利于小尺寸設計,因此在實際設計時,需要平衡電感量、紋波電流、電感尺寸之間的關系。在選擇電感時,除了要滿足電感量參數外,還要考慮電感的可以承受的最大電流,即IRMS 電流值,同時還要考慮電感的飽和電流值,即ISAT,如果流過電感的總電流ITOTAL=IDC+IRIPPLE 超過了ISAT,那就會使得電感飽和而失去了電感特性,即由電感變成了導線,從而造成變換器失效而損壞,通常來說,工程上快速評估可以采取1.5 倍的Io 做為一個合適的選取標準,比如輸出負載電流為1A,那么選擇電感的有效電流IRMS 為1.5A 為宜;還要注意的是,盡量選取帶有屏蔽功能的電感,這樣可以減少DC-DC 變換器工作時對外部環境造成的干擾。

10、SuPA 的PCB 設計和PCB 板疊層設計

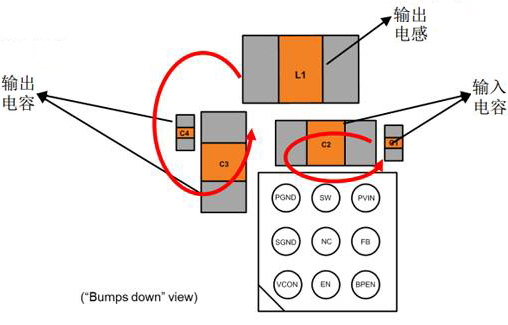

1. 功率器件的位置(輸入、輸出電容和電感)

如下圖所示,

圖16、LM3242布局示意圖

從圖中可以看出入口電容C1和C2是放置在芯片PVIN管腳最近的位置,輸出電容是放在距離電感輸出端最近的位置,這樣做的原因是保持輸入端功率回路包含面積(芯片,C1和C2、地線組成的環路)以及輸出端功率回路面積(輸出電感、C3、C4、地線)最小,這樣可以有效減小開關電源噪音對外部環境的干擾,這是在射頻電路設計中需要仔細考慮的要點。

2. 功率器件與芯片間的連線和PCB板疊層定義

PCB 板疊層設計舉例:

表層:用于連接流過大電流的連線,比如輸入、輸出電容、電感的電源線。

第二層:連接信號用的連線可以放置在此層,注意的是FB 管腳是被復用的(做為ACB 使用)會承載比較大的電流,因此需要使用10mil 以上的線寬連接。

第三層:連接SW 的連線可以放置此層,SW 是用來承載大于1A 以上的峰值電流,因此線寬需要大于15mil,在某些應用時甚至需要分配兩層同時放置SW 銅線(兩層疊加),用于減小寄生電感,盡可能降低在此銅線上的dv/dt,即SW 上的開關噪音振鈴幅值。

粵公網安備 44030902003195號

粵公網安備 44030902003195號