很多人都說,高速電路看著比普通的電路的電路結構簡單,但是為什么都說很難,說這話的工程師可能還沒有深入的了解高速電路的特點。沒錯,在做低速電路的時候,總想著要做電路匹配等等,高速電路相對來講確實簡單,不是兩顆芯片中間加兩顆AC耦合電容直接相連,就是一顆芯片與連接器中間加兩顆AC耦合電容直接相連。但是不要看著結構簡單,因為在高速電路中,電路已經不是簡單的電路,電容也不是簡單的一顆電容啦,這一顆電容優化不好,可能就會導致你整個高速電路設計失敗。

在高速串行鏈路中,為了讓工作在不同電壓下的發送器和接收器能夠連接(也許是為了不影響各自buffer模擬電路部分的靜態工作點),需要在通路中加入AC耦合電容,但是AC耦合電容自身和焊接電容的焊盤會給通路帶來阻抗的不連續性,這在設計中都需要仔細考慮。

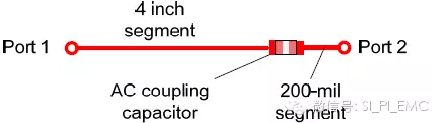

以一個典型的通路作為實例案例來研究這個問題

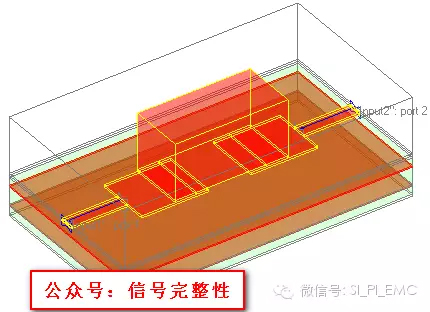

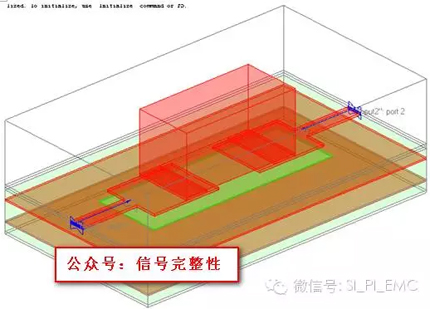

當信號傳到AC耦合電容處,由于焊盤的面積和電容兩端的引腳比較大,這個點的寄生電容必然很大,最終在阻抗曲線TDR圖上對應地顯示出阻抗偏小,進而導致return loss變的很大。為了讓阻抗連續,減小電路的容性,提高阻抗,通常采取在電容的下方隔層參考(挖空某些層),如下圖

接下來,我們將通過修改前后的電容結構分別做3D電磁場仿真,對比其處理前后的阻抗、回波損耗以及插入損耗。

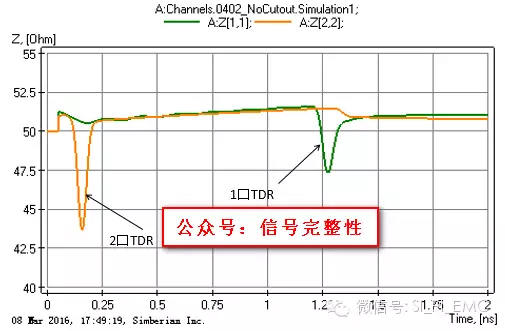

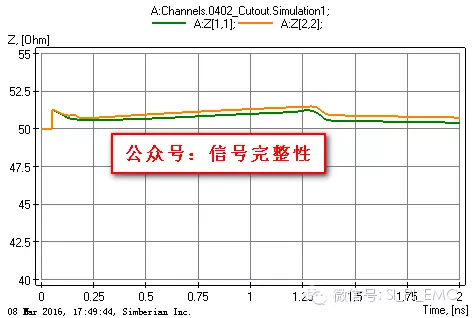

一、對比阻抗(TDR)

用前面3D電磁場仿真得到的S參數對這兩種電路做TDR分析:

1) 沒有處理時

2) 做隔層處理

可以看到未處理之前阻抗的不連續點很明顯,做隔層處理之后的阻抗改善很多,幾乎看不到任何的不連續了。

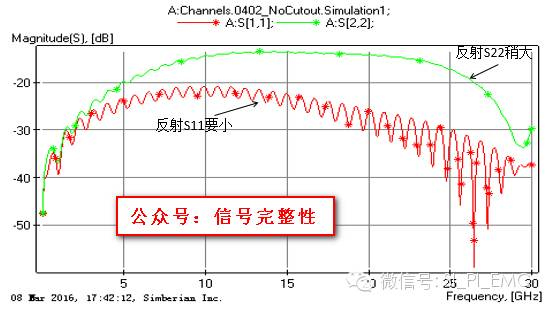

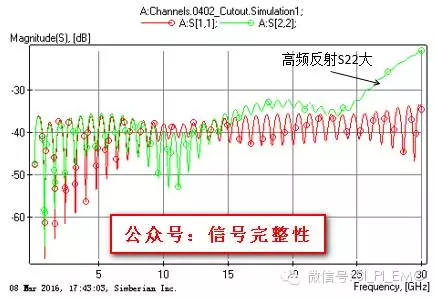

二、對比回損

1) 沒有處理時

2) 做隔層處理

隔層處理之后,無論是S11還是S22,都要比原來的改善很多,回波損耗在-30dB以下,這在實際的通路中的響應降到最低。從S22>S11可以看出靠近電容端的端口回損要大。

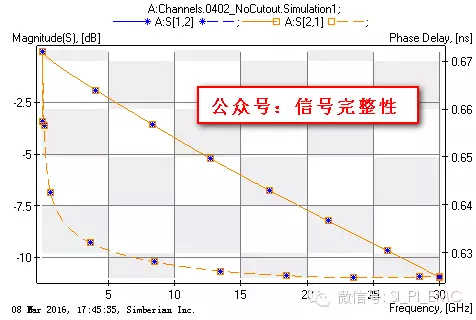

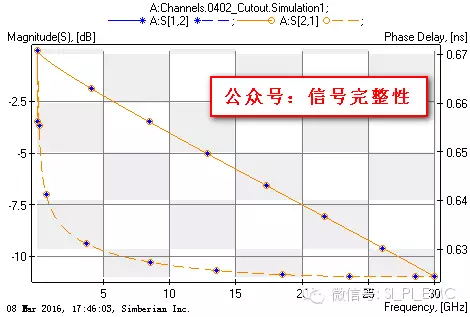

三、對比插損

1) 沒有處理時

2) 做隔層處理

從仿真結果上看,對AC耦合不連續點的處理與否,對插入損耗的影響不大。

從以上三個結果的分析可以發現,AC耦合電容的焊盤的處理對信號網絡的阻抗和回波損耗的影響非常大。我們在實驗中使用的還是0402的電容,現在很多工程師還在使用0603或者是更大size的電容,如果不進行處理,其影響肯定更大。但是大家在使用隔層參考的時候,還是需要謹慎一些,不要想當然的看到電容,就把下面所有的參考層都挖空。還是建議通過一些仿真之后再確定是否要做處理,或者是如何做處理。

來源:

粵公網安備 44030902003195號

粵公網安備 44030902003195號