在現代通信系統中,對頻率源的頻率穩定度和準確度的要求越來越高,只采用晶振是不能滿足需要的。而頻率合成技術則是利用一個或多個高穩定度的晶體振蕩器產生一系列等間隔的、離散的、高穩定度的頻率,可為通信設備提供大量精確且能迅速轉換的載波信號和本振信號,完全滿足現代通信的需要。其中鎖相頻率合成器具有工作頻帶寬、工作頻率高、頻譜質量好、方案簡單、造價低等優點,在目前現有的頻率合成方法中應用最為廣泛。

1 鎖相環頻率合成器的基本原理

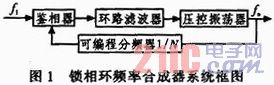

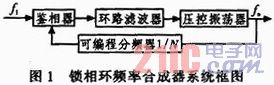

一個典型的頻率合成器主要由鑒相器(PD)、環路濾波器(LF)、壓控振蕩器(VCO)和可編程分頻器組成。其系統框圖如圖1所示。

基本工作原理是由晶體振蕩器提供參考輸入信號,經分頻后得到鑒相頻率fi與來自VCO的輸出信號fo經N分頻后得到的反饋信號進行鑒相,所產生的相位誤差信號,經電荷泵作用后轉換為與相位誤差成比例的正/負電流脈沖串,然后利用環路濾波器對來自電荷泵的電流脈沖求積分,向VCO調諧端口提供干凈的電壓,從而實現對VCO的頻率控制。當環路鎖定時,輸出頻率與鑒相頻率的關系如下:

N分頻器的分頻比不同時,輸出頻率fo也隨之變化。所以,只需要選擇合適的晶體振蕩器和選擇合適的N值就能產生所需要的頻率信號。

2 鎖相頻率合成器方案的設計

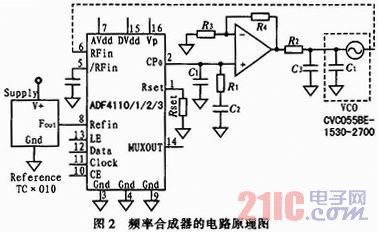

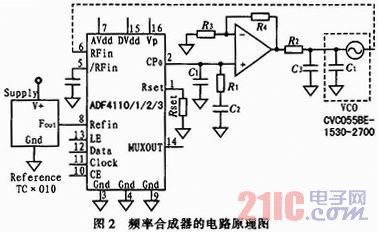

設計的頻率合成器的技術指標為輸出頻率1580~2500MHz,頻率間隔200kHz,輸出雜散優于-65dBc,輸出相噪優于-80dBe/Hz@1 kHz。根據技術指標來選擇合適的芯片,其中鎖相環器件選用ADI公司的ADF4112芯片,該芯片集成了鑒相器和可編程分頻器,最大工作頻率為3GHz,相位噪聲基底可達-215 dBc/Hz。VCO采用Crystek公司的CVC055BE-1530-2700,其頻率范圍為1530~2700MHz,靈敏度為140MHz/V,輸出功率65dBm,相位噪聲-87dBc/Hz@10kHz。

環路濾波器的設計是頻率合成器設計的最重要的一個部分,它的性能好壞直接關系到鎖相輸出的相位噪聲和雜散指標。由于本系統輸出頻帶范圍比較大,VCO所需的控制電壓最高達到7.5V,高于所選鎖相環芯片中電荷泵所能提供的最高供電電壓,所以使用無源環路濾波器不足以達到控制VCO所需的調諧電壓值,必須使用具有放大功能的有源濾波器。為了抑制有源器件產生的噪聲,一般使用三階以上的有源環路濾波器,電路如圖2中所示。這種結構采用同相放大器,不需要專用偏置,比較直觀、簡便。電阻R3和R4用來控制電路的增益,增益大小A表示為:

而且,電阻R4和R3的取值必須足夠大,以保證其消耗的電流不超出范圍。C3和R2有邊帶濾波作用,C1、C2和R1則用來調整環路帶寬、阻尼系數、相位噪聲等參數。

其中運算放大器采用ADI公司的AD820,該運算放大器具有可單電源供電、軌到軌、低噪聲等特點,滿足本設計的要求。系統整體電路圖如圖2所示。

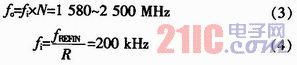

在系統調試過程中,對芯片中前置分頻器的值的設定要特別注意。芯片資料中給出,前置分頻器的值應該被選擇使它的輸出頻率總是小于或等于200 MHz,因此,在本設計中,16/17前置分頻器的值是有效的,8/9是無效的。由以下公式:

可以得出:N=7 900~12 500。

3 鎖相環頻率合成器的仿真

頻率合成器中環路濾波器的計算是非常復雜的,特別是對于高階鎖相環。所以采用ADS仿真軟件對頻率合成器進行仿真,不僅可以對鎖相環的各項性能指標進行分析,以確保設計方案的正確性,而且還可以對環路濾波器的參數進行設定和優化,減小了研制人員的研制難度和調試時間。

3. 1 頻域響應仿真

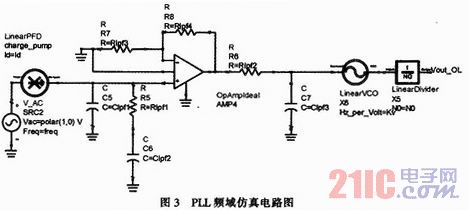

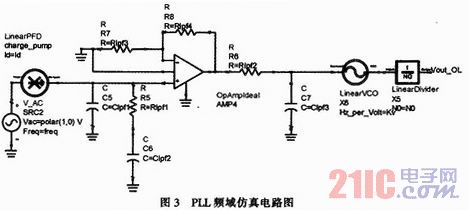

頻域仿真的目的是通過鎖相環參數設置,得到實際的相位裕量、環路帶寬、環路衰減和環路濾波器的參數。并同時得到鎖相環的頻域開、閉環幅度響應和相位響應曲線。調用ADS中的線性電荷泵鑒相器、線性壓控振蕩器、線性分頻器等模塊搭建鎖相環頻率響應電路。其中部分電路仿真電路圖如圖3所示。

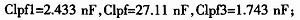

根據系統指標對頻域仿真中所需要的仿真控制器參數和一些變量模型的參數進行設置。其中掃描計劃(SWEEP PLAN)用于設定掃描的范圍,交流仿真器(AC)設定原理圖中采用小信號交流仿真。優化目標依次設置為開環增益、相位裕量、雜散抑制等。變量模型VAR1中主要對鎖相環一些特性進行設置,VAR2主要設置相位裕量、濾波器帶寬、雜散頻率等,VAR3主要設置環路濾波器的一些參數。完成各個模塊的參數設置后,仿真可以得到鎖相環路有源濾波器元件參數如下:

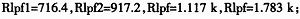

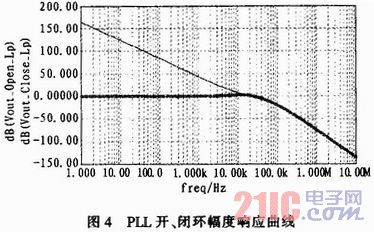

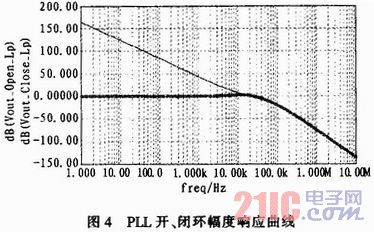

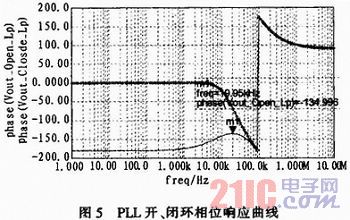

由仿真自動優化計算所得到的元器件值并不是實際使用的標稱值,可以選擇最接近仿真值的標稱值作為實際使用值。如果得到的器件值不太合理,可以重新在原理圖中設定器件值的范圍,再次仿真。另外,可以得到鎖相環電路的開、閉環幅度響應和相位響應曲線,如圖4、圖5所示,其中加線圈的為閉環響應曲線。從圖中可以看出鎖相環是比較穩定的,并且該電荷泵鎖相環的環路帶寬為19.95 kHz,相位裕度為45.004°。仿真結果與設計指標比較接近,證明整個系統設計方案可行。

3.2 瞬態響應仿真

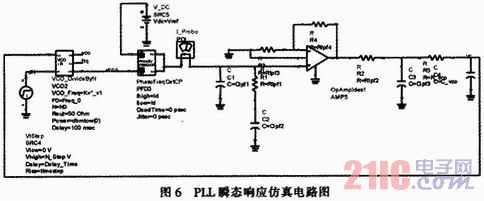

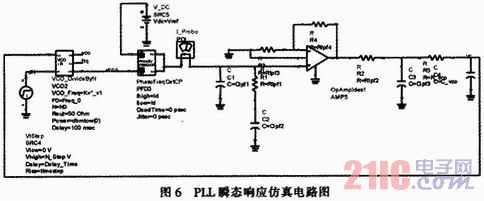

對鎖相環的瞬態響應仿真主要是針對鎖相環的VCO在從自由振蕩到被系統鎖定過程的瞬態響應,可以得到PLL的鎖定時間。主要是用ADS中的電荷泵鑒相器、帶分頻器的VCO、階躍電壓源等構建仿真電路如圖6所示。

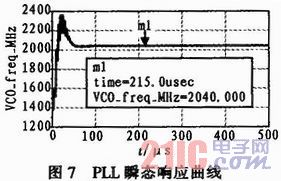

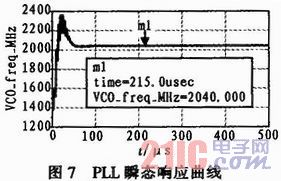

仿真電路圖中VCO內部帶有分頻器,分頻比受階躍電壓源SCR4控制。由于仿真中只觀察單一頻點的鎖定時間,所以仿真時可以把SCR4旁路掉,或者把其階躍電壓N_Step配置成0 V。選擇單一的頻率點2 040 MHz,仿真可得到鎖相環輸出頻率的瞬態響應曲線如圖7所示。

從圖中可以看出,在215μs時,鎖相環基本鎖定。可見通過對頻率合成器的瞬態響應仿真可以對電路是否能夠鎖定、鎖定時間、鎖定頻率范圍、環路濾波器的設計是否存在問題等方面進行分析。

4 結束語

首先對鎖相環頻率合成器電路進行簡單設計,然后利用ADS仿真軟件對電路進行頻率響應和瞬態仿真。這種方法既可以免去計算環路濾波器的麻煩和保證設計方案的正確性以縮短鎖相環電路設計的時間,又可以通過對鎖相環各種性能指標的仿真分析加深對鎖相環的理解。

1 鎖相環頻率合成器的基本原理

一個典型的頻率合成器主要由鑒相器(PD)、環路濾波器(LF)、壓控振蕩器(VCO)和可編程分頻器組成。其系統框圖如圖1所示。

基本工作原理是由晶體振蕩器提供參考輸入信號,經分頻后得到鑒相頻率fi與來自VCO的輸出信號fo經N分頻后得到的反饋信號進行鑒相,所產生的相位誤差信號,經電荷泵作用后轉換為與相位誤差成比例的正/負電流脈沖串,然后利用環路濾波器對來自電荷泵的電流脈沖求積分,向VCO調諧端口提供干凈的電壓,從而實現對VCO的頻率控制。當環路鎖定時,輸出頻率與鑒相頻率的關系如下:

N分頻器的分頻比不同時,輸出頻率fo也隨之變化。所以,只需要選擇合適的晶體振蕩器和選擇合適的N值就能產生所需要的頻率信號。

2 鎖相頻率合成器方案的設計

設計的頻率合成器的技術指標為輸出頻率1580~2500MHz,頻率間隔200kHz,輸出雜散優于-65dBc,輸出相噪優于-80dBe/Hz@1 kHz。根據技術指標來選擇合適的芯片,其中鎖相環器件選用ADI公司的ADF4112芯片,該芯片集成了鑒相器和可編程分頻器,最大工作頻率為3GHz,相位噪聲基底可達-215 dBc/Hz。VCO采用Crystek公司的CVC055BE-1530-2700,其頻率范圍為1530~2700MHz,靈敏度為140MHz/V,輸出功率65dBm,相位噪聲-87dBc/Hz@10kHz。

環路濾波器的設計是頻率合成器設計的最重要的一個部分,它的性能好壞直接關系到鎖相輸出的相位噪聲和雜散指標。由于本系統輸出頻帶范圍比較大,VCO所需的控制電壓最高達到7.5V,高于所選鎖相環芯片中電荷泵所能提供的最高供電電壓,所以使用無源環路濾波器不足以達到控制VCO所需的調諧電壓值,必須使用具有放大功能的有源濾波器。為了抑制有源器件產生的噪聲,一般使用三階以上的有源環路濾波器,電路如圖2中所示。這種結構采用同相放大器,不需要專用偏置,比較直觀、簡便。電阻R3和R4用來控制電路的增益,增益大小A表示為:

而且,電阻R4和R3的取值必須足夠大,以保證其消耗的電流不超出范圍。C3和R2有邊帶濾波作用,C1、C2和R1則用來調整環路帶寬、阻尼系數、相位噪聲等參數。

其中運算放大器采用ADI公司的AD820,該運算放大器具有可單電源供電、軌到軌、低噪聲等特點,滿足本設計的要求。系統整體電路圖如圖2所示。

在系統調試過程中,對芯片中前置分頻器的值的設定要特別注意。芯片資料中給出,前置分頻器的值應該被選擇使它的輸出頻率總是小于或等于200 MHz,因此,在本設計中,16/17前置分頻器的值是有效的,8/9是無效的。由以下公式:

可以得出:N=7 900~12 500。

3 鎖相環頻率合成器的仿真

頻率合成器中環路濾波器的計算是非常復雜的,特別是對于高階鎖相環。所以采用ADS仿真軟件對頻率合成器進行仿真,不僅可以對鎖相環的各項性能指標進行分析,以確保設計方案的正確性,而且還可以對環路濾波器的參數進行設定和優化,減小了研制人員的研制難度和調試時間。

3. 1 頻域響應仿真

頻域仿真的目的是通過鎖相環參數設置,得到實際的相位裕量、環路帶寬、環路衰減和環路濾波器的參數。并同時得到鎖相環的頻域開、閉環幅度響應和相位響應曲線。調用ADS中的線性電荷泵鑒相器、線性壓控振蕩器、線性分頻器等模塊搭建鎖相環頻率響應電路。其中部分電路仿真電路圖如圖3所示。

根據系統指標對頻域仿真中所需要的仿真控制器參數和一些變量模型的參數進行設置。其中掃描計劃(SWEEP PLAN)用于設定掃描的范圍,交流仿真器(AC)設定原理圖中采用小信號交流仿真。優化目標依次設置為開環增益、相位裕量、雜散抑制等。變量模型VAR1中主要對鎖相環一些特性進行設置,VAR2主要設置相位裕量、濾波器帶寬、雜散頻率等,VAR3主要設置環路濾波器的一些參數。完成各個模塊的參數設置后,仿真可以得到鎖相環路有源濾波器元件參數如下:

由仿真自動優化計算所得到的元器件值并不是實際使用的標稱值,可以選擇最接近仿真值的標稱值作為實際使用值。如果得到的器件值不太合理,可以重新在原理圖中設定器件值的范圍,再次仿真。另外,可以得到鎖相環電路的開、閉環幅度響應和相位響應曲線,如圖4、圖5所示,其中加線圈的為閉環響應曲線。從圖中可以看出鎖相環是比較穩定的,并且該電荷泵鎖相環的環路帶寬為19.95 kHz,相位裕度為45.004°。仿真結果與設計指標比較接近,證明整個系統設計方案可行。

3.2 瞬態響應仿真

對鎖相環的瞬態響應仿真主要是針對鎖相環的VCO在從自由振蕩到被系統鎖定過程的瞬態響應,可以得到PLL的鎖定時間。主要是用ADS中的電荷泵鑒相器、帶分頻器的VCO、階躍電壓源等構建仿真電路如圖6所示。

仿真電路圖中VCO內部帶有分頻器,分頻比受階躍電壓源SCR4控制。由于仿真中只觀察單一頻點的鎖定時間,所以仿真時可以把SCR4旁路掉,或者把其階躍電壓N_Step配置成0 V。選擇單一的頻率點2 040 MHz,仿真可得到鎖相環輸出頻率的瞬態響應曲線如圖7所示。

從圖中可以看出,在215μs時,鎖相環基本鎖定。可見通過對頻率合成器的瞬態響應仿真可以對電路是否能夠鎖定、鎖定時間、鎖定頻率范圍、環路濾波器的設計是否存在問題等方面進行分析。

4 結束語

首先對鎖相環頻率合成器電路進行簡單設計,然后利用ADS仿真軟件對電路進行頻率響應和瞬態仿真。這種方法既可以免去計算環路濾波器的麻煩和保證設計方案的正確性以縮短鎖相環電路設計的時間,又可以通過對鎖相環各種性能指標的仿真分析加深對鎖相環的理解。

粵公網安備 44030902003195號

粵公網安備 44030902003195號