基于ADS的接收機(jī)碼元同步算法實現(xiàn)

蘇鵬博1 董燚2 許建華3 張超3

1西安電子科技大學(xué),陜西,西安710071

2西安新天盟航空科技有限公司,陜西,西安710075

3電子測試技術(shù)國家科技重點(diǎn)實驗室,山東青島266555

摘要:數(shù)字通信系統(tǒng)中,碼元同步對于實現(xiàn)信號的準(zhǔn)確判決碼元和降低系統(tǒng)誤碼率起著關(guān)鍵作用。本文介紹了在ADS仿真環(huán)境下實現(xiàn)16QAM接收機(jī)碼元同步算法。采用的定時誤差提取算法消除了傳統(tǒng)算法在16QAM系統(tǒng)中引起的時鐘抖動問題,實現(xiàn)了接收信號和發(fā)送信號同步。并對該算法在ADS環(huán)境下進(jìn)行了仿真,仿真結(jié)果表明該算法實現(xiàn)了碼元同步的功能,并對干擾有較強(qiáng)的抵抗能力。

關(guān)鍵詞 碼元同步 Gardner算法 ADS 16QAM

0 引言

在數(shù)字接收機(jī)中,為了在抽樣判決時刻準(zhǔn)確判決發(fā)送過來的碼元,需要提供一個確定抽樣判決時刻的定時脈沖序列。這個定時脈沖序列的重復(fù)頻率必須與發(fā)送的數(shù)碼脈沖序列一致(即接收、發(fā)送雙方必須同步,具有相同的主頻率),同時在最佳判決時刻對接收碼元進(jìn)行抽樣判決。這樣的定時脈沖序列稱為碼元同步。

16QAM(Quadrature Amplitude Modulation)接收機(jī)要完成16QAM信號的解調(diào)首先要完成碼元同步,再通過隨后的均衡、載波恢復(fù)等模塊完成信號的解調(diào)。因此碼元同步算法的實現(xiàn)是至關(guān)重要的一部分。

1 碼元定時同步原理及其在ADS中的設(shè)計

數(shù)字化的解調(diào)器中,經(jīng)過下變頻所得的基帶信號通過匹配濾波器,然后以時鐘周期為Ts的固定采樣頻率進(jìn)行采樣、量化后進(jìn)入碼元同步環(huán)路。

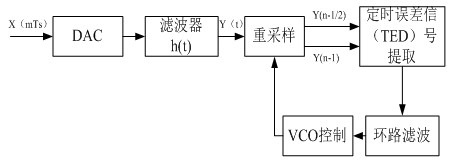

圖1 碼元同步模塊的結(jié)構(gòu)

在論文中,具體采用的定時同步模塊如圖1所示,它由內(nèi)插濾波器(由DAC、濾波器和重采樣等效實現(xiàn))、定時誤差提取(TED)、環(huán)路濾波器以及VCO控制器組成。從圖中可看出:信號經(jīng)過內(nèi)插后,每個符號內(nèi)有兩個采樣點(diǎn),再進(jìn)行時鐘誤差提取,得到的誤差信號經(jīng)過環(huán)路濾波器后送給VCO,最后控制內(nèi)插完成同步。即通過采樣點(diǎn)提取時鐘控制信號調(diào)整采樣時鐘來達(dá)到同步。

下面分別介紹各模塊的原理。

1.1 內(nèi)插濾波器原理

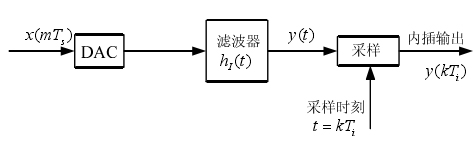

內(nèi)插濾波器實際上實現(xiàn)的是一個數(shù)據(jù)的速率轉(zhuǎn)換可以假設(shè)它的模型如圖2所示。

圖2 速率轉(zhuǎn)換

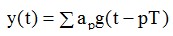

假定接收端固定采樣時鐘為 ,符號周期為T。內(nèi)插器接收的信號為

,符號周期為T。內(nèi)插器接收的信號為 ,通過DAC及濾波器后

,通過DAC及濾波器后 ,得到一個連續(xù)時間的輸出:

,得到一個連續(xù)時間的輸出:

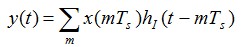

(1-1)

(1-1)

現(xiàn)在,對于y (t),在每個時刻 時對其再次進(jìn)行采樣,其中,k為正整數(shù)。T為內(nèi)插器周期,它與符號周期是同步的。

時對其再次進(jìn)行采樣,其中,k為正整數(shù)。T為內(nèi)插器周期,它與符號周期是同步的。

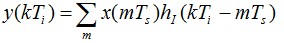

(1-2)

(1-2)

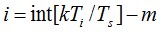

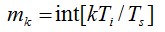

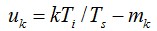

對于上式(5-2),m為輸入序列指針,定義濾波器指針為:

(1-3)

(1-3)

同樣,定義基本指針為:

(1-4)

(1-4)

分?jǐn)?shù)間隔為:

(1-5)

(1-5)

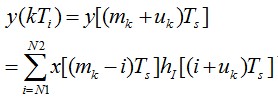

內(nèi)插公式可以重新寫為:

(1-6)

(1-6)

式(1-6)為數(shù)字內(nèi)插濾波器的基本方程。

引入?yún)?shù) ,

, 是有實際意義的。它們表示了

是有實際意義的。它們表示了 ,

, 之間的調(diào)整關(guān)系。其中,

之間的調(diào)整關(guān)系。其中,  決定了計算第k個內(nèi)插值

決定了計算第k個內(nèi)插值 的N=N2-N1+1個信號樣值,

的N=N2-N1+1個信號樣值, 指示了內(nèi)插估值點(diǎn),并決定用來計算內(nèi)插值

指示了內(nèi)插估值點(diǎn),并決定用來計算內(nèi)插值 的N個插值濾波器脈沖響應(yīng)樣值。一般情況下,

的N個插值濾波器脈沖響應(yīng)樣值。一般情況下, 是個無理數(shù)且對每次內(nèi)插都是變化的,直到定時穩(wěn)定時,

是個無理數(shù)且對每次內(nèi)插都是變化的,直到定時穩(wěn)定時, 將穩(wěn)定在某一個定值上。

將穩(wěn)定在某一個定值上。

1.2 定時誤差(TED)信號的提取

Gardner碼元同步算法是一種異步時鐘恢復(fù)方法,本地生成碼元時鐘,采用插值方法得到抽樣時刻碼元值,不需要滿足采樣時鐘與碼元時鐘是整數(shù)倍關(guān)系的要求。Gardner碼元同步算法中,輸入的基帶信號經(jīng)過插值后得到2倍碼元速率的抽樣數(shù)據(jù),抽樣數(shù)據(jù)經(jīng)過反饋支路控制數(shù)控振蕩器輸出頻率從而調(diào)整碼元時鐘,采樣得到最佳采樣點(diǎn),完成時鐘的鎖定和跟蹤。

Gardner算法不需要判決反饋,每個數(shù)據(jù)需要兩個采樣點(diǎn),其中一個是strobe點(diǎn),即符號最佳觀察點(diǎn);另一個是midstrobe點(diǎn),即兩個最佳觀察點(diǎn)之間的采樣點(diǎn)。一個在符號判決點(diǎn)附近,另一個在兩個符號判決點(diǎn)中間附近,并且與載波相位偏差無關(guān),因此定時調(diào)整可先于載波恢復(fù)完成,定時恢復(fù)環(huán)和載波恢復(fù)環(huán)相互獨(dú)立,這給解調(diào)器的設(shè)計和調(diào)試帶來了方便。

假設(shè)接收信號為: ,式中

,式中 為傳輸?shù)膹?fù)數(shù)數(shù)據(jù),

為傳輸?shù)膹?fù)數(shù)數(shù)據(jù), 為基帶成型濾波波形,對

為基帶成型濾波波形,對 的采樣值可能產(chǎn)生定時誤差,Gardner算法提取的定時誤差為:

的采樣值可能產(chǎn)生定時誤差,Gardner算法提取的定時誤差為:

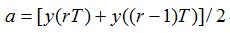

(2-1)

(2-1)

其中索引r表示符號數(shù)目,同相I和正交Q方向的第r個符號的判決值分別表示為 和

和 。同樣,將r和(r-1)兩個判決點(diǎn)中心位置的采樣值表示為

。同樣,將r和(r-1)兩個判決點(diǎn)中心位置的采樣值表示為 和

和 。整個誤差是I和Q兩個方向的定時誤差之和,且此誤差與載波相位無關(guān)。

。整個誤差是I和Q兩個方向的定時誤差之和,且此誤差與載波相位無關(guān)。

式中 ,

, 表示同相和正交分量,T為符號周期。Gardner算法適用于跟蹤和捕獲模式。

表示同相和正交分量,T為符號周期。Gardner算法適用于跟蹤和捕獲模式。

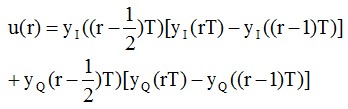

圖3 16QAM解調(diào)后波形

在16QAM調(diào)制信號中,例如果符號從-1變?yōu)?,1變?yōu)椋?,-3變?yōu)?,3變?yōu)椋?等的時候,則沒有定時誤差時,中間點(diǎn)的平均值應(yīng)為零。而有定時誤差時,將會產(chǎn)生一個非零的值,它的大小與差錯的大小成正比。另外一些情況,當(dāng)沒有定時誤差時,中間點(diǎn)的平均值并不是零。例如符號從3變?yōu)椋?,當(dāng)沒有定時誤差時,中間點(diǎn)的平均值是1,如圖3所示。

如果直接把Gardner算法運(yùn)用在16QAM解調(diào)系統(tǒng)中,定時誤差檢測的結(jié)果有些點(diǎn)上是正確的,有些點(diǎn)上是錯誤的。對于大量數(shù)據(jù),這些錯誤的平均值是零,因為沒有定時誤差的情況,中間點(diǎn)可能是0,-1,1,-2,2,其平均值為零。因此這些錯誤會導(dǎo)致定時時鐘的抖動,通過濾波器可以減小這些抖動。

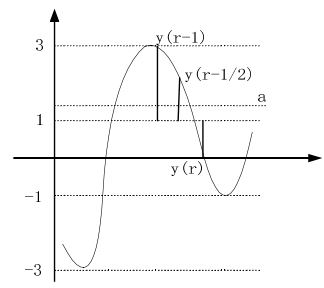

為了消除這些抖動。我們對Gardner算法做了進(jìn)一步改進(jìn),其改進(jìn)后算法為:

(2-2)

(2-2)

其中

當(dāng)定時超前,誤差為負(fù),定時滯后,誤差為正。Gardner算法具有兩個特點(diǎn):一是每個符號只需要兩個采樣點(diǎn),且以碼元速率輸出誤差信號;二是估計算法是獨(dú)立于載波相位的,不受載波相位偏移的影響,即可以在載波相位同步之前,進(jìn)行定時誤差估計。

1.3 壓控振蕩器(VCO Voltage Controlled Oscillator)

定時恢復(fù)環(huán)的內(nèi)插濾波器由VCO控制,它接受定時誤差信號,給內(nèi)插濾波器提供內(nèi)插運(yùn)算所需的參數(shù) 和

和 ,壓控振蕩器的時鐘頻率為1/

,壓控振蕩器的時鐘頻率為1/ 。

。

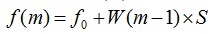

VCO的輸出頻率f(m):

,

,

為VCO預(yù)設(shè)基本頻率,

為VCO預(yù)設(shè)基本頻率, 為VCO控制信號,由定時誤差信號經(jīng)環(huán)路濾波器濾波后提供,VCO的輸出頻率隨著

為VCO控制信號,由定時誤差信號經(jīng)環(huán)路濾波器濾波后提供,VCO的輸出頻率隨著 的變化而變化,當(dāng)

的變化而變化,當(dāng) 穩(wěn)定時,輸出頻率也就保持穩(wěn)定。S為VCO對誤差信號的敏感度。VCO輸出每出現(xiàn)一次過零點(diǎn),則產(chǎn)生一個定時調(diào)整抽樣脈沖

穩(wěn)定時,輸出頻率也就保持穩(wěn)定。S為VCO對誤差信號的敏感度。VCO輸出每出現(xiàn)一次過零點(diǎn),則產(chǎn)生一個定時調(diào)整抽樣脈沖 ,從而可以決定

,從而可以決定 ,也就是決定哪些采樣信號值參加內(nèi)插運(yùn)算。

,也就是決定哪些采樣信號值參加內(nèi)插運(yùn)算。

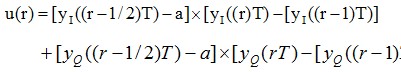

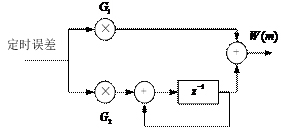

1.4 環(huán)路濾波器

采用二階數(shù)字濾波器對定時誤差信號進(jìn)行濾波如圖4,以減小定時誤差信號的抖動。環(huán)路濾波器系數(shù)和定時誤差S曲線系數(shù)以及數(shù)控振蕩器控制靈敏度共同決定環(huán)路相對等效噪聲帶寬 。

。

圖4 二階數(shù)字濾波

選定環(huán)路相對等效噪聲帶寬 和阻尼系數(shù),就可以求出二階數(shù)字濾波的參數(shù)

和阻尼系數(shù),就可以求出二階數(shù)字濾波的參數(shù) ,

, 。

。

2 ADS中的仿真結(jié)果分析

ADS,即HP Advanced Design System的簡稱。它是Agilent Technologies公司新推出的一套電路輔助設(shè)計軟件。Agilent Technologies公司把已有產(chǎn)品:HP MDS(Microwave Design System)和HP EEsof IV(Electronic Engineering Software)兩者的精華有機(jī)的結(jié)合起來,并增加了許多新的功能,構(gòu)成了功能強(qiáng)大的ADS軟件。ADS可應(yīng)用于整個現(xiàn)代通信系統(tǒng)及其子系統(tǒng),能對通訊系統(tǒng)能進(jìn)行快速、便捷、有效的設(shè)計和仿真。

ADS軟件分為Digital Signal Processing Network和Analog/RF Network兩個仿真設(shè)計模塊。接收機(jī)的仿真是在Digital Signal Processing Network中完成,里面加載了很多常用的通信器件,可供調(diào)用。

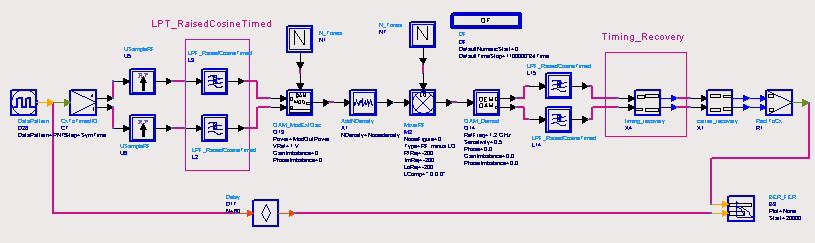

在ADS中,建立仿真模型,本文仿真基于16QAM調(diào)制、1.8GHHz中頻、720Mbps碼速率中頻采樣的全數(shù)字解調(diào)系統(tǒng)(如圖5),研究了高速全數(shù)字解調(diào)中碼元同步的關(guān)鍵技術(shù)。

圖5 通信系統(tǒng)誤碼率仿真工程

仿真設(shè)計:1、系統(tǒng)中,碼元的長度為5.6nsec。在發(fā)送端的低通成型濾波器(LPT_RaiseCosineTimed)中加入2nsc的延時來仿真碼元抖動。

2、改變VCO的預(yù)設(shè)基本頻率 來仿真接受端時鐘偏差,VCO的敏感度S為1MHz/V。

來仿真接受端時鐘偏差,VCO的敏感度S為1MHz/V。

仿真結(jié)果:

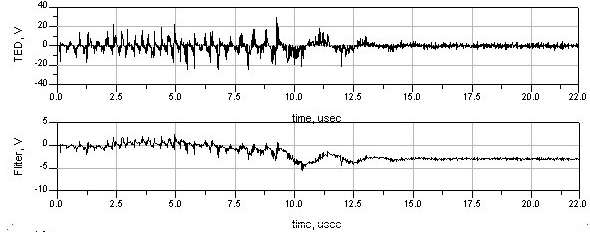

圖6 時鐘恢復(fù)環(huán)中誤差信號、環(huán)路濾波后的信號

圖6為從碼元同步模塊中測量出來的誤差信號、環(huán)路濾波后的信號。從圖中可得出,VCO根據(jù)反饋回來經(jīng)過濾波后的誤差信號(如圖6下)來實時調(diào)整采樣的頻率,直到VCO輸出時鐘頻率 等于2倍碼元速率為止,就達(dá)到了平衡狀態(tài),此時定時誤差為零(如圖6上)。

等于2倍碼元速率為止,就達(dá)到了平衡狀態(tài),此時定時誤差為零(如圖6上)。

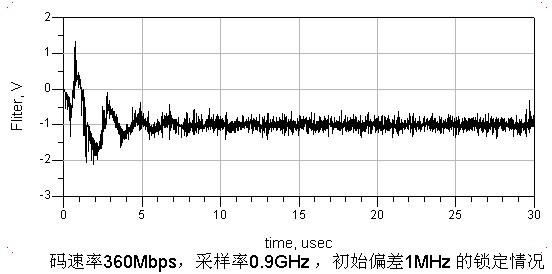

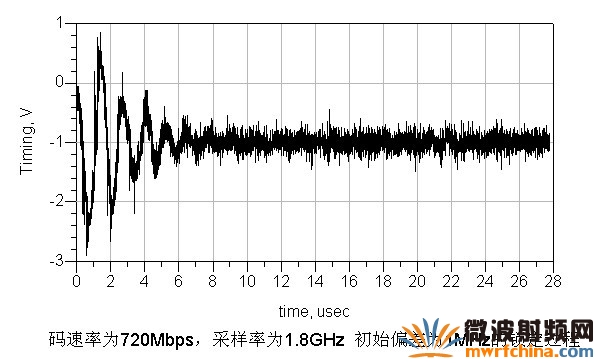

圖7 不同碼元速率的鎖定過程

圖7所示分別為1.8GHz采樣率,碼元速率720Mbps,初始偏差1MHz,信噪比20dB時碼元同步的鎖定情況;和0.9GHz采樣率,碼速率360MHz,初始偏差1MHz ,信噪比20dB時碼元同步的鎖定情況。仿真證明這種碼元同步方法能夠正確生成碼元時鐘滿足高碼速要求,并且適應(yīng)不同碼速率。能正確生成碼元時鐘滿足高碼速要求,并且適應(yīng)不同碼速率。

| 測試環(huán)境 測試項目 |

無碼元同步模塊時誤碼率(BER) | 有碼元同步模塊時誤碼率(BER) | |

| 理想系統(tǒng) | 4.554E-6 | 4.554E-6 | |

| 抖動 | 8.730E-5 | 9.039E-6 | |

| 接收時鐘偏差 |

Bias=0.5MHz | 0.017 | 4.554E-6 |

| Bias=1MHz | 0.036 | 4.554E-6 | |

| Bias=1.5MHz | 0.041 | 4.554E-6 | |

| Bias=2MHz | 0.054 | 0.065 | |

| 抖動和偏差 | 0.048 | 1.937E-5 | |

表1 仿真系統(tǒng)中的碼元抖動、時鐘偏差時的誤碼率

通過上表說明,如圖5所示的系統(tǒng)中,碼元同步模塊對于的信號的抖動和接收端時鐘的頻率偏差有較強(qiáng)的糾正能力。抖動為半個碼元長度時,模塊將誤碼率從1.730E-5降到了9.039E-6。對于時鐘的頻率偏差糾正能力尤為突出,達(dá)到3MHz的范圍(748.5MHz~~751.5MHz)內(nèi)都可以鎖定。當(dāng)同時加入碼元抖動和時鐘偏差時,系統(tǒng)也表現(xiàn)出了較強(qiáng)的糾錯能力。

3 結(jié)束語

本文簡要介紹了在ADS仿真器中,設(shè)計一個16QAM接收機(jī)的碼元同步模塊,以消除恢復(fù)時鐘偏差和I、Q兩路信號的不同步引起的碼元抖動的問題。并針對16QAM這種調(diào)制方式,提出了改進(jìn)的誤差提取算法。仿真顯示可以滿足不同速率下的接收機(jī)要求。

參考文獻(xiàn):

[1] 陳艷華李朝暉。《ADS應(yīng)用詳解》人民郵電出版社。

[2] F.M.Gardner,Interpolation in Digital Modems-Part I: IEEE Trans Comm, COM-41,pp501-504,Mar,1993.

[3] 黃載祿殷蔚華。《通信原理》科學(xué)出版社。

[4] 張輝,曹麗娜。《現(xiàn)代通信原理與技術(shù)》西安電子科技大學(xué)出版社,2002。

[5] 孔明東,邱昆。用于減小定時抖動的數(shù)字預(yù)濾波器設(shè)計[J]。電子科技大學(xué)學(xué)報,2002: 31。

[6] John G. Proakis. Digital Communication (Fourth edition)[M]. Beijing: Publishing house of electronics industry, 2001.

作者簡介:蘇鵬博西安電子科技大學(xué)在讀研究生,研究方向:高頻數(shù)字信號接收與處理技術(shù)研究。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號