電源是各種電子設備必不可少的重要組成部分,其性能的優(yōu)劣直接關系到整個電子系統(tǒng)的安全性和可靠性。單片開關電源集成電路由于其具有高集成度、高性價比、最簡外圍電路、最佳性能指標等優(yōu)點,顯示出了強大的生命力

|

|

PI公司于2002年9月推出的LinkSwitch(簡稱LNK)系列單片電源在正常工作時的開關頻率一般在42kHz,不僅對前級電路帶來很大的電磁兼容問題,而且也對鄰近的某些電子設備產生電磁干擾。故必須對整個電路進行電磁兼容(EMC)設計,使各個元件在復雜的電磁環(huán)境下都能正常運行。

1 LNK的電磁兼容性問題

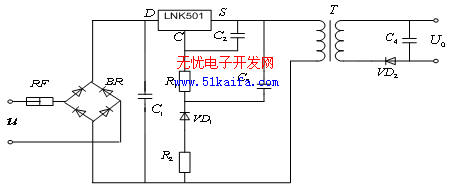

圖1 LNK開關電源電路模型

開關電源產生電磁干擾最根本的原因,就是其在工作過程中產生的高di/dt與高dv/dt,它們產生的浪涌電流和尖峰電壓形成了干擾源。開關管的驅動波形、MOSFET漏源波形等矩形波在脈沖邊緣時的高頻變化對開關電源的基本信號造成了干擾。圖1為由LNK構成開關電源的電路模型。下面具體分析圖1中噪聲產生的原因和途徑。

1.1 電源線引入的噪聲

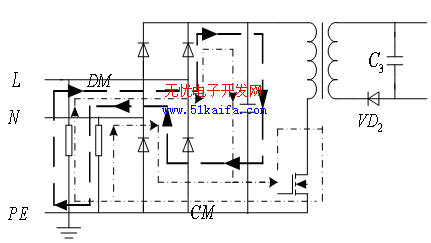

電源線噪聲是電網(wǎng)中各種用電設備產生的電磁騷擾沿著電源線傳播所造成的,對外表現(xiàn)為傳導干擾和輻射干擾。傳導干擾分為共模(Common Mode—CM)干擾和差模(Differential Mode—DM)干擾。共模干擾定義為任何載流導體與參考地之間的不希望有的電位差,差模干擾定義為任何兩個載流導體之間的不希望有的電位差。由于開關電路寄生參數(shù)的存在以及開關器件的高頻開通和關斷,使得開關電源在其輸入端產生較大的共模干擾和差模干擾。圖2即為圖1的共模差模干擾的傳播途徑。在高頻情況下,由于dv/dt很高,激發(fā)變壓器線圈間以及LNK的寄生電容,從而形成了共模干擾。如圖2的黑體虛線所示。在高頻情況下,在輸入輸出的濾波電容上產生很高的di/dt,從而形成了差模干擾。如圖2的淡體虛線所示。

圖2 共模、差模干擾傳播途徑

1.2 變壓器產生的干擾

高頻變壓器是開關電源實現(xiàn)能量儲存、隔離輸出、電壓變換的重要元件,在不考慮漏感以及開關動作時間時,高頻工作下的MOSFET產生的波形應該是標準的方波。但在實際變壓器制作時,繞組漏感是不可避免的。由于漏感存在,開關閉合時,原邊漏感將儲存一定的能量,當開關關斷時,儲存的能量得到釋放,使得開關器件的兩端出現(xiàn)電壓關斷尖峰,與原來的直流高壓和感應電壓疊加,可使MOSFET的漏極電壓超過700V(LNK系列的MOSFET的漏極擊穿電壓為700V),有可能影響開關的正常工作甚至損壞LNK。

1.3 輸出整流二極管的尖峰干擾

理想的二極管在承受反向電壓時截止,不會有反向電流通過。但實際二極管在承受反向電壓時,PN結內儲存的電荷在反向電場作用下被復合,形成反向恢復電流,它恢復到零點的時間與結電容等因素有關。反向恢復電流在變壓器漏感、引線電感以及二極管的結電容的影響下將產生強烈的高頻衰減振蕩,高頻衰減振蕩電壓與關斷電壓疊加,將形成一個相當大的關斷電壓尖峰。這個反向恢復噪聲也是開關電源的一個主要干擾源。

1.4 分布電容及寄生參數(shù)引起的干擾

開關電源的分布電容主要為開關電源與散熱器或外殼之間的分布電容、LNK的漏極與電源線之間的分布電容、變壓器初次級之間的分布電容。以上的分布電容都可以傳輸共模干擾。

在高頻下,普通的電阻電容電感都將呈高頻寄生特性,這將對其正常工作產生影響。例如,高頻工作時,導線寄生電感的感抗顯著增加,這將使其變成一根發(fā)射線,即成了開關電源中的一個輻射干擾源。

2 EMC設計

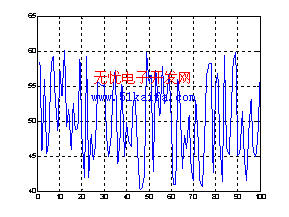

圖3 未考慮EMC設計的EMI仿真曲線

圖3為未考慮EMC設計時的EMI仿真曲線,根據(jù)廣泛采用的GB9254中規(guī)定的標準曲線,可看出干擾強度超過規(guī)定標準了,必須對電路進行相應的抗干擾設計。

EMC設計應該從三個方面去考慮:

1) 減小干擾源產生的干擾信號

2) 切斷干擾信號的傳播途徑

3) 增強敏感電路的抗干擾能力2.1 輸入側濾波器設計

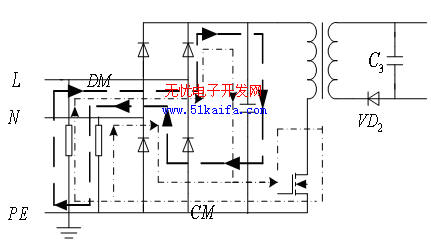

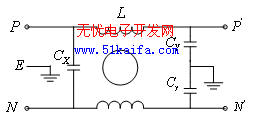

電源線干擾可以使用EMI濾波器濾除,EMI濾波器應是一個只允許直流至工頻(50Hz,400Hz)通過的理想低通濾波器,即從直流至截止頻率的通帶以最小衰減通過,一般以額定電流下的壓降表示;對電磁干擾的阻帶,給以盡可能高的衰減;通帶和阻帶之間的過濾帶應盡量的陡。

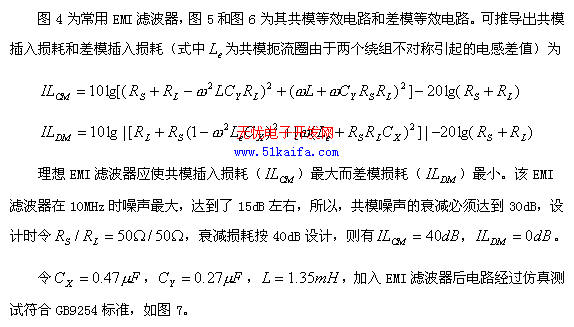

圖4 常規(guī)使用的EMI濾波器

圖5 共模等效電路

圖6 差模等效電路

圖7加入EMI濾波器后的仿真曲線

2.3輸出整流二極管尖峰抑制

對輸出整流二極管產生的反向恢復噪聲,可以通過在二極管兩端并聯(lián)RC緩沖器來抑制,也可以通過在二極管串聯(lián)一個飽和電感來抑制。并聯(lián)的RC緩沖器起到一階濾波器的作用,根據(jù)需要濾除高頻噪聲。串聯(lián)的飽和電感在整流二極管導通時工作在飽和狀態(tài)下,相當于導線;在整流二極管關斷反向恢復時,工作在電感特性狀態(tài)下,可以阻礙電流的大幅度變化。

2.4其他措施

1.對整流電路采用無源功率因數(shù)校正法來降低諧波成分并提高功率因數(shù);

2.對變壓器進行屏蔽來減少其漏感帶來的輻射;

3.對電路板進行合理設計,LinkSwitch應盡量遠離交流輸入端,盡量減小高頻變壓器初次回路所包圍的面積。

3結語

抑制開關電源的干擾是開發(fā)應用型開關電源的一個重要的課題。本文就不同的干擾源提出了針對性的解決方法,并就原電路的EMI仿真曲線重新設計了電路的參數(shù),改進后的電路基本符合GB9254標準。文末提出的幾種工藝改進的方法都能對開關電源的電磁干擾問題起到進一步的作用,這些都對開關電源的電磁兼容設計具有一定的參考意義

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號