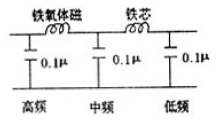

圖5、多級濾波器

圖5中,低頻帶寬為10 kHz~1 MHz;中頻帶寬為1 MHz~100 MHz;高頻帶寬為100 MHz~1GHz。在低通濾波器中,如果存在任何對地阻抗,該阻抗便成為高頻噪聲的旁路路徑,因此,濾波器的地應是寬頻帶且連接到低阻抗點或地線層上,以優化濾波性能。另外,高頻電容的引腳應盡可能短,最好采用低電感表面貼片式瓷片電容。

5、電源線的EMI/RFI抑制對策

電源線的EMI/RFI是由瞬變電壓引起的,因此,這類干擾的抑制對策主要是提高電路或系統對瞬變電壓的適應能力。分析和實踐證明下述措施對提高電源抗干擾能力是有效的。

(1)在電源引入端加混合電源瞬變保護網絡。

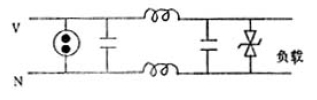

如圖6所示,氣體放電管和大功率齊納二極管提供差模與共模保護,在要求不高時,可用金屬氧化物壓敏電阻代替齊納二極管。扼流圈用來吸收浪涌電流。

圖6、混合電源瞬變保護網絡

(2)利用變壓器進行隔離。變壓器對大于300ns的瞬變有很好的保護作用。但在具體應用中應注意,變壓器的連接方式不同,所構成的保護模式也不同。一般由四種方式:1)采用無屏蔽的標準變壓器,且次級與安全地相連以消除中性點與地之間的壓差;2)采用單層法拉第屏蔽的變壓器,屏蔽與安全地連接以實現共模保護;3)采用單層法拉第屏蔽的變壓器,初級與中性線相連以實現差模保護;4)采用三層法拉第屏蔽的變壓器,可實現差模、共模保護,并能消除中性點與安全地之間的壓差。

(3)在電源的整流和穩壓輸出端除加有大電容低頻濾波外,應并接低容量無感高頻濾波電容器。其容量:

C=ΔIΔl/Δu

式中ΔI--電源電流波動的峰值;Δl--電流脈動寬度;Δu--電源電壓波動允許值。

(4)在每個電路模塊上電源線走線在接法上使其終端形成閉環,否則,在電源線終端相當于開路時,高頻干擾就會形成全反射,而使干擾信號成倍增加。

(5)盡量使電源線和地線平行走線,使電源線對地呈低阻抗以減小電源噪聲干擾。最好使用雙絞線饋電。

6、PCB設計中的EMI/RFI保護

印刷電路板上信號線的布設如何,將直接關系到系統對電磁干擾和電磁能輻射的靈敏度,一個不好的PCB設計很可能導致系統的EMC失敗。高頻噪聲在PCB上可能耦合、輻射的途徑有:電源線輻射、電源阻抗耦合、公共地阻抗耦合、I/O線的串擾與輻射。因此,在設計中,應從以下幾個方面來考慮抑制EMI/RFI。

(1)如果條件允許,應盡可能采用低于實際要求速度的器件。因為,器件速度越高,EMI問題就越嚴重。對于納秒級的器件,由于它們具有寬帶寬,采樣時鐘和輸入對任何形式的高頻噪聲都會響應。對于此類高速器件,可在其I/O端采用具有鐵氧體芯電感的小型濾波器以降低對EMI/RFI環境的敏感度。如果是雙極性供電,應在正、負供電線上均加鐵氧體芯電感。

(2)電源層、地線層和信號層的合理設計。一個好的PCB布局應將關鍵的模擬信號路徑與高頻源隔離、數字/模擬的高頻部分與低頻部分相互隔離。采用多層板可減小EMI發射,且對RF場的抗擾度要比雙面板增加10倍或更多。比較好的多層板排列是將信號線嵌入在電源層和地線層之間,這種設計的優點是低阻抗、低輻射、低串擾,可減小50MHz以上的輻射和串擾,但板內容量小,退耦困難,嵌入信號線的測試與檢修困難。

(3)PCB中走線的特性阻抗。為了防止反射,要求PCB上走線的特性阻抗應滿足單向傳輸延遲時間等于或大于信號上升/下降時間的一半。為此,一般應采用2英寸/ns準則。表3給出了常用數字邏輯基于2英寸/ns準則的走線長度。2英寸/ns準則也適用于模擬電路的走線設計。

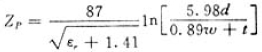

對于利用絕緣材料將信號層與電源/電線層隔離的PCB板的特性阻抗可用下式計算:

式中εr為PCB板材料介電常數;d為各層的厚度(mils);w為線寬(mils);t為線厚(mils)。

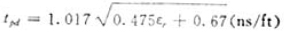

信號層走線的單向傳輸時間由下式確定:

例如:一個標準4層PCB板,一般利用0.021〃FR-4(εr=4.7)型絕緣材料隔離,采用8mil寬、1.4 mil厚的銅層走線,其特性阻抗為88Ω,單向傳輸時間為1.7 ns/ft。

總之,在PCB設計時,必須按實際情況和可能大些,將信號線間隙用地線填充。電源和地線采用平行走線,有利于減小電感。

粵公網安備 44030902003195號

粵公網安備 44030902003195號