隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則:

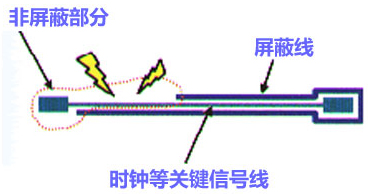

規則一:高速信號走線屏蔽規則

在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

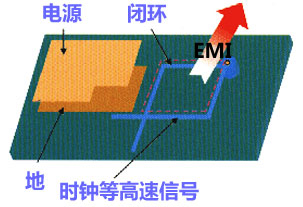

規則二:高速信號的走線閉環規則

由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加EMI的輻射強度。

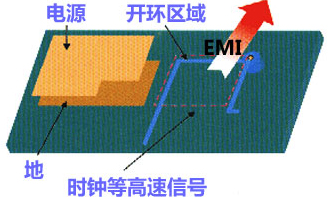

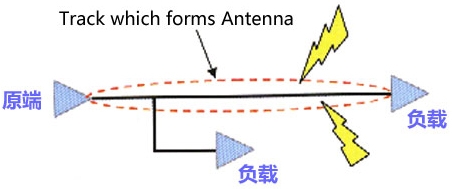

規則三:高速信號的走線開環規則

規則二提到高速信號的閉環會造成EMI輻射,然而開環同樣會造成EMI輻射。

時鐘信號等高速信號網絡,在多層的PCB走線的時候一旦產生了開環的結果,將產生線形天線,增加EMI的輻射強度。

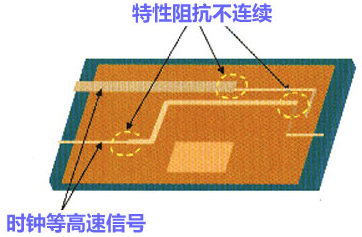

規則四:高速信號的特性阻抗連續規則

高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。

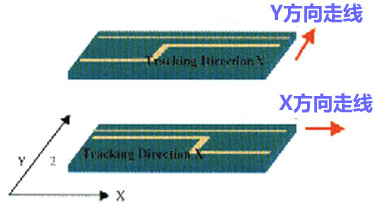

規則五:高速PCB設計的布線方向規則

相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。

簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串擾。

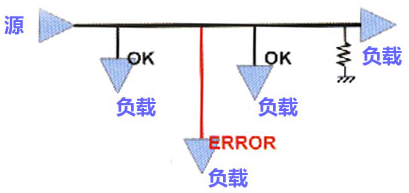

規則六:高速PCB設計中的拓撲結構規則

在高速PCB設計中,線路板特性阻抗的控制和多負載情況下的拓撲結構的設計,直接決定著產品的成功還是失敗。

圖示為菊花鏈式拓撲結構,一般用于幾Mhz的情況下為益。高速PCB設計中建議使用后端的星形對稱結構。

規則七:走線長度的諧振規則

檢查信號線的長度和信號的頻率是否構成諧振,即當布線長度為信號波長1/4的時候的整數倍時,此布線將產生諧振,而諧振就會輻射電磁波,產生干擾。

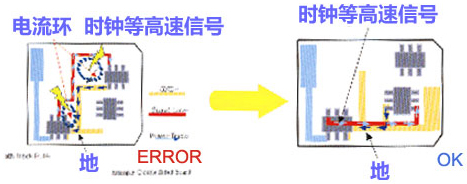

規則八:回流路徑規則

所有的高速信號必須有良好的回流路徑。盡可能地保證時鐘等高速信號的回流路徑最小。否則會極大的增加輻射,并且輻射的大小和信號路徑和回流路徑所包圍的面積成正比。

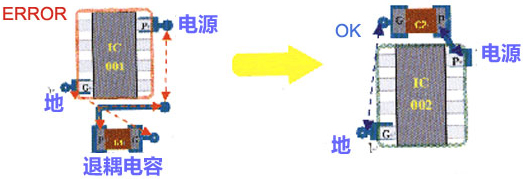

規則九:器件的退耦電容擺放規則

退耦電容的擺放的位置非常的重要。擺放不合理根本起不到退耦的效果。其原則是:靠近電源的管腳,并且電容的電源走線和地線所包圍的面積最小。

粵公網安備 44030902003195號

粵公網安備 44030902003195號