本章及隨后幾章將討論靜電放電引起的系統(tǒng)問題的硬件解決措施。為了便于對系統(tǒng)硬件解決進行討論,將系統(tǒng)上的靜電放電效應劃分成以下三個部分:

1. 靜電放電之前靜電場的效應

2. 放電產生的電荷注入效應

3. 靜電放電電流產生的場效應

盡管印刷線路板(PWB,通常也稱之為PCB)的設計會對上述三種效應都產生影響,但是主要是對第三種效應產生影響。下面的討論將針對第三條所述的問題給出設計指南。通常,源與接收電路之間的場耦合可以通過下列方式之一減小(這些通用方法也會在其它討論場的章節(jié)中提到):

1. 在源端使用濾波器以衰減信號

2. 在接收端使用濾波器以衰減信號

3. 增加距離以減小耦合

4. 降低源和/或接收電路的天線效果以減小耦合

5. 將接收天線與發(fā)射天線垂直放置以減小耦合

6. 在接收天線與發(fā)射天線之間加屏蔽

7. 減小發(fā)射及接收天線的阻抗來減小電場耦合

8. 增加發(fā)射或接收天線之一的阻抗來減小磁場耦合

9. 采用一致的、低阻抗參考平面(如同多層PCB 板所提供的)耦合信號,使它們保持共模方式

在具體設計中,如電場或磁場占主導地位,應用方法7 和8 就可以解決。然而,靜電放電一般同時產生電場和磁場,這說明方法7 將改善電場的抗擾度,但同時會使磁場的抗擾度降低。方法8 則與方法7 帶來的效果相反。所以,方法7 和8并不是完善的解決方案。不管是電場還是磁場,使用方法1 ~ 6 與9 都會取得一定的效果,但PCB 設計的解決方法主要取決于方法3 ~ 6 和9 的綜合使用。

下面詳細闡述通過方法 3 ~ 6 和9 解決問題的六條實踐法則及其原因所在。

一、保持環(huán)路面積最小

任意一個電路回路中有變化的磁通量穿過時,將會在環(huán)路內感應出電流。電流的大小與磁通量成正比。較小的環(huán)路中通過的磁通量也較少,因此感應出的電流也較小,這就說明環(huán)路面積必須最小。應用這一經驗的困難之處是如何找到環(huán)路。

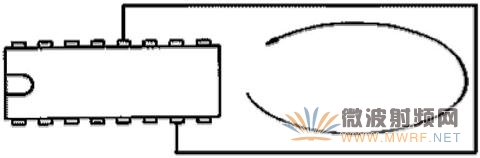

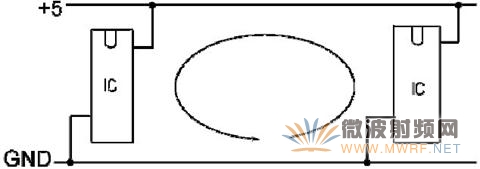

每個人都知道圖16 中所示的環(huán)路,但要正確識別圖17 中所示的環(huán)路則比較困難。

圖 16 簡單的PCB 回路

圖 17 電源線與地線構成的PCB 回路

與其試著去找出所有可能的環(huán)路,還不如采取下列步驟來減小環(huán)路面積:

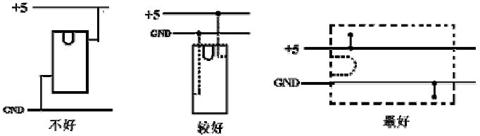

A、電源線與地線應緊靠在一起以減小電源和地間的環(huán)路面積。

圖 18 示例說明了電源線與地線同集成電路連接的幾種不同方法。

圖 18 電源與地形成的環(huán)路面積的減小

粵公網安備 44030902003195號

粵公網安備 44030902003195號