電子設計小型化是多層印刷電路板得到廣泛使用的驅動力。多層電路更多占用的是垂直空間而非水平空間,因此可以在緊湊的空間內實現設計堆疊。電路的層數是指電路中導體層的數量,通常由介質層隔開。由于介質材料的選擇范圍極廣,且材料特性和厚度多樣,因此電路開發人員通過采用多層電路的設計方法,可以在極小的空間內實現性能目標。某些獨特的射頻設計概念可以確保多層電路原型的實測性能水平達到或超過投產后的性能水平。

射頻/微波電路的多層印刷電路板通常在外層采用多種不同的高頻電路技術,如微帶線、帶狀線和接地共面波導電路等。這些電路技術均可設計為缺陷地結構來對射頻性能做一些優化和改善。缺陷地結構最初是為微帶諧振器開發,是在電路板接地平面上有目的性的產生銅挖空區域而呈現蝕刻圖形。在應用得當的情況下,缺陷地結構有助于改善電流流向,能有效減少波長,且可以實現信號隔離。

由于缺陷地結構易受電磁輻射影響,因此采用缺陷地結構的電路設計和制造始終受到擔憂。一直以來,電路內的缺陷地結構模型和電磁仿真軟件工具均有限。但是,隨著計算機和電路模擬器的發展,缺陷地結構模型也得到了改進,即使采用自定義缺陷地結構的電路,也可在合理的計算機處理時間內準確模擬大多數電路的行為。

抑制輻射

當電路較為簡單時,多層電路中的缺陷地結構可能無需擔心會產生非必要的電磁輻射。例如,在一些多層結構中,最上層作為信號層,依次往下是介質材料、第二層銅層、介質材料,以及第三層銅層,此時可以在第二層中設計缺陷地結構。如需設計濾波器,則可以將第二層中設計所需的尺寸,使形成在所需的頻率或頻率帶下的抑制凹陷而達到濾波器的所需頻率響應。對于僅有兩個導電層(即濾波結構電路和接地層)的電路,接地層中的缺陷可能是電磁輻射的潛在來源。但是,對于多層電路,第三層可抑制缺陷地結構發出的輻射。此外,缺陷地結構周圍密布的接地過孔有助于隔離三層中第二和第三銅層之間的任何電磁輻射。

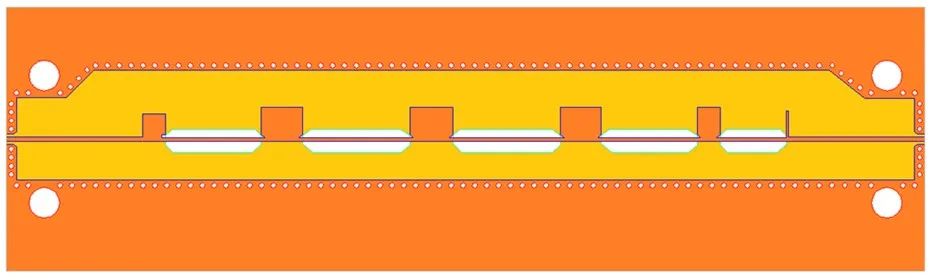

缺陷地結構有助于提升多種射頻/微波電路的性能,且即使應用于多層電路結構,也不會給電路制造商帶來額外挑戰。例如在一個三層電路結構實現的一種階躍阻抗低通濾波器。[1]這種階躍阻抗濾波器使用了窄導體來實現高阻抗,使用寬的導體來實現低阻抗(如圖所示)。通過增加高低阻抗之間的阻抗差,可增強濾波器性能(例如阻帶區)。然而,通常高阻抗值的實現受限于介質材料特性和制造工藝的蝕刻精度。

但是,在高阻抗區采用缺陷地結構可以大幅增加阻抗,同時能夠避免電路制造商的較窄線路的蝕刻風險。阻抗的增加有助于將降低無用的諧波而改善濾波器的阻帶響應。為便于說明,先以下圖的一個兩層低通濾波器進行說明,深橙色顯示電路的頂層信號,淺橙色顯示底層或接地層,接地層中的缺陷地結構以白色區域表示。如采用多層結構低通濾波器,則代表缺陷接地的白色區域位于第二層,再往下的第三層即作為濾波器的完整的接地層。

這種缺陷地的設計靈活性也可用于毫米波頻率的一些電路設計中。缺陷地結構的使用十分有益于毫米波雷達中常用的微帶線串聯供電貼片天線陣列。這種結構有助于調整陣列輻射貼片之間的相互耦合,減少無用的頻率響應,并抑制旁瓣。通過缺陷地結構,在輻射貼片之間的饋線可使用更寬的導體,從而滿足特定的阻抗需求。更寬的導體饋線有利于在貼片陣列天線的大批量制造過程中進一步提高生產良率。

在微帶線貼片天線陣列中采用缺陷地結構的另一種方法是使用帶狀線導體為陣列的輻射貼片饋電。帶狀線是一種可達到最小的輻射損耗和高隔離度的高頻低損耗傳輸線結構。通過電路板蝕刻出的開口,可將帶狀線饋電結構連接到位于帶狀線上方導體層的微帶線輻射貼片。幸運的是,這種蝕刻的開口,可實現與輻射貼片的良好耦合而進行饋電,且可在毫米波頻率下提供良好的天線性能。

使用不同的電路材料可以使小型化的多層電路具有優越的射頻/微波性能。例如,耦合帶狀線可以通過4層電路結構來實現,其中最上層(第1層)和最底層(第4層)作為接地層,兩個內層(第2層和第3層)作為耦合信號導體層。由于耦合強度會隨著電路材料介電常數(Dk)的增加而增加,因此,如果在介電常數較高的電路材料上制造兩個內導體層,則可達到較高的耦合系數和層間耦合。

需要注意的是,在帶狀線電路中使用不同的電路材料實現高頻耦合必須仔細建模,因為材料的介電常數差異會導致不同的偶模和奇模相速度。當相速差較大時,一些不必要的響應也隨之增加,從而可能影響電路性能。

使用介電常數有差異的電路材料有利于多層微帶線邊緣耦合結構。[2]例如,在包含三個銅層的多層板中,在第1、2層之間使用介電常數高的材料,在第2、3層之間使用介電常數低的材料。由此,在第2層中某些沒有銅箔的區域,由介電常數不同的兩種介質材料,將第1層和第3層上隔開。

由于存在偶模和奇模相速度差,因此微帶線邊緣耦合濾波器會產生非必要的諧振。這是因為耦合場會穿過有效介電常數不同的介質:在奇模下穿過空氣和介質材料,但在偶模下僅穿過介質材料。通過控制高、低介電常數材料的厚度比,奇模耦合場仍將部分穿過空氣,并且還將穿過介電常數較高的材料,但無法穿過介電常數較低的材料。通過優化高介電常數和低介電常數材料的厚度比,可以使兩種模式下的相速度盡可能相等,從而減少無用諧波,同時改善濾波器阻帶性能。

以上僅是采用多層印刷電路板結構來增強射頻性能的眾多應用中的示例。如需更詳細地了解多層電路的優勢,請聯系當地的羅杰斯代表或訪問我們的羅杰斯技術支持中心。

參考文獻

[1] John Coonrod, “Multilayer PCB Technology Supports Microstrip DGS Without Radiation Loss,” Microwave Journal, Vol. 61, No. 2, February 2018

[2] John Coonrod, “Harmonic Suppression of Edge Coupled Filters Using Composite Substrates,” Microwave Journal, Vol. 55, No. 9, September 2012

粵公網安備 44030902003195號

粵公網安備 44030902003195號