1月22日,Altera 在北京展示了號稱業界最全面的28nm 最新技術及強大解決方案。Altera公司的多位工程師為在京的媒體人士進行了講解。下面是演示圖片、相關資料及簡短說明。

Altera工程師為媒體朋友現場講解

首先是面向帶寬設計的Stratix V GT FPGA系列。該器件基于TSMC 28nm HP高性能工藝制程,單管芯集成收發器和FPGA確保高性能互連。集成4路28.05Gb/s極高速雙工收發器,單通道功耗僅200mW。它同時集成32路0.6-12.5Gb/s通用高速雙工收發器。

業界唯一集成28Gb/s收發器的量產FPGA

收發器是Altera引以自豪的技術。Stratix V的收發器芯片到芯片速度達到28Gb/s,芯片到背板速度為14Gb/s(受限于連接器的信號衰減)。圖片右側是專門從泰克公司借來的設備,據說兩臺儀器價值分別為100萬美元和50萬美元。經過10英尺的線路板,數字分析儀顯示出Stratix V漂亮的眼圖。

下面的演示用的是Stratix V GX開發板。Stratix V GX器件可提供多達66個全雙工600Mb/s到14.1Gb/s的高速收發器通道,具備符合10GBase-KR和CEI-11G標準的高速背板支持能力。它支持EDC以簡化與光模塊接口,時鐘資源可以提供最多44組完全獨立的通道速率。每個收發器通道均內嵌完整的PMA和PCS功能,可以以硬核支持多種速率。它支持高級的通道發送和接收均衡功能包括預加重,自適應線性均衡和DFE。支持通道參數的動態重配置功能,并支持EyeQ。Stratix V GX系列已經大規模進入量產。

突破帶寬:Stratix V GX系列可提供多達66個14.1Gb/s收發器通道

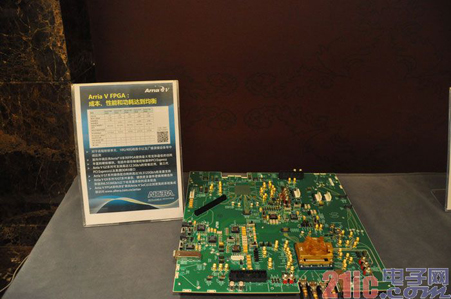

下圖是Arria V系列的演示。Arria V 是兼顧成本、性能和功耗的中端器件。新推出的Arria V GZ是最大帶寬的中端器件,填補了高端與低端器件之間的空白。它可提供多達36個600Mb/s到12.5Gb/s的全雙工收發器并支持背板傳輸。它是中端器件唯一可完整支持第三代PCI Express的。Arria V GZ支持1600Mb/s DDR3接口速率,提供業界最高的中端器件內核性能。

Arria V FPGA:成本、性能和功耗達到均衡

Arria V GZ:最大帶寬的中端器件

下圖是Cyclone V開發套件。Cyclone V GX/GT FPGA系列面向低功耗和低成本應用,基于TSMC 28nm LP低功耗工藝制程。它集成12路3.125 / 5Gb/s雙工收發器,5Gb/s單通道功耗僅88mW,內嵌硬核PCIE和DDR3控制器,節省邏輯資源,提高系統性能和開發效率。

該系列采用Avalon Memory Mapped架構,自動生成PCIE TLP編/解碼邏輯,極大地縮短工程開發時間。PCIE接口帶寬吞吐效率大于80%。Cyclone V GT FPGA支持PCIE Gen2,可將PCIE帶寬再提升1倍。400MHz DDR3控制器接口靈活支持x8 / x16 / x32bits數據位寬,支持ECC校驗。采用Avalon Streaming接口,總線效率可達90%以上。

Cyclone V FPGA:PCIe / DDR3 DMA

下面的是OpenCL演示。OpenCL標準是第一個開放編程模型,能夠在異構系統上加速算法實現。一個演示展示OpenCL是怎樣加速Mandelbrot算法性能的。另一個演示展示OpenCL怎樣為異構計算提供統一的平臺:把為GPU編寫的NVIDIA代碼移植到Stratix V FPGA上。

業界首款提供FPGA支持OpenCL開發環境

下圖展示的是Cyclone V SoC開發板,在雙核CPU上啟動并運行Linux。這是Altera發售的第一款器件是低功耗、低成本Cyclone V SoC (FPGA+ARM)。這個開發板剛剛到貨,Altera的工程師也是第一次見到。該器件的特點是具有硬核的存儲器控制器、靈活的啟動功能、以及在全部SoC器件集成PCI Express。Altera是目前唯一發售支持32位糾錯碼(ECC)的SoC的FPGA供應商,保證了整個嵌入式系統的數據完整性。

前不久,Altera和ARM聯合開發了Altera版的ARM Development Studio 5(DS-5)工具包,具有專門支持Altera SoC器件的FPGA自適應調試功能,產品應用包括無線通信、工業、視頻監控、汽車和醫療設備等市場。

Altera第一款SoC器件:Cyclone V SoC (FPGA+ARM)

粵公網安備 44030902003195號

粵公網安備 44030902003195號