為了測量高頻率的S參數設計的設備,每個SBD被放置了有三個探頭焊盤。中間信號墊的大小是85μm×85μm和頂部/底部的的地面尺寸是85μm×135μm的。使用GSG探頭和網絡分析儀,我們可以得到S參數設計的SBD.但是,S參數的直接測量結果包括墊片、金屬線和覆蓋的寄生電容。對于設計的設備而言,盡管寄生參數是非常小的,但這些寄生參數是絕對不能被忽視的,在計算的時候應該將GSG探頭直接測量的S參數減去。在本文所研究的設計中,我們制作兩個虛擬的GSG信號墊作為測試裝置,假如兩個信號墊一個是偽GSG信號墊,一個是SBD信號墊,且兩個信號墊同等大小。除此以外的虛擬信號墊都是開放的,這也就是我們所說的開放式信號墊。S參數由啞墊進行測量。接著就可以得到信號墊和金屬線的寄生電阻和電容。將這些寄生參數減去,就能夠得到S參數的無寄生電阻和電容。將這種方法稱之為去嵌入技術。

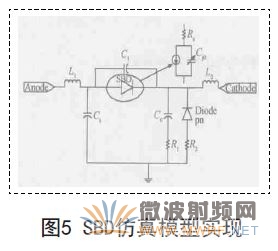

使用測得的S參數可以抽象為高頻模擬SPICE模型。圖5顯示SBD仿真離子模型的實現。L1和L2顯示出的輸入和輸出串聯電感。Ci和Co表示陽極輸入輸出電容和陰極節點。C1具有相互交織的肖特基二極管的兩個端口之間的寄生電容。R1和R2為連接S參數下NWLL到地面下電阻的n-阱的模型。pn二極管反映的寄生蟲n阱p-次二極管。在我們的設計中,可以用得到的pn二極管的參數通過標準CMOS工藝0.35μm的SPICE模型。

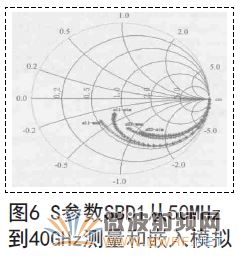

如圖6所示,為S參數SBD1測量和模擬。

表2給出了仿真離子模型的參數,頻率SBD1從50MHz到40GHz,該模型可以匹配到30GHz的測量結果。

6.結束語

隨著無線通訊具有的靈活性和高機動性的特點,其應用越來越廣泛,也順應了市場的需求。由于CMOS工藝在諸多的工藝中最為成熟、成本最低,卻功耗最小,因此得到廣泛的應用,隨著技術的不斷成熟,CMOS工藝基礎上的肖特基二極管設計及實現也成為現實。也是未來射頻集成電路發展的必然趨勢。通過MPW在標準CMOS工藝制造的肖特基勢壘二極管中的設計應用,可知鋁硅接觸的勢壘高度約0.44eV.

通過I-V,C-V和S參數測量可以實現SBD.通過本文所示,SBD設計的優勢較為明顯,最為顯著的是設計成本較低,能夠被廣泛的應用與商業標準的CMOS工藝中。在以后的工作中,更多的重點將集中在標準CMOS工藝設計的SBD的反向擊穿電壓和頻率范圍擴展。

粵公網安備 44030902003195號

粵公網安備 44030902003195號