摘要:貝爾實驗室的研究人員展示了如何利用賽靈思FPGA、IP 核和MATLAB 為RFDAC 的快速評估創建一個靈活平臺。

無線通信行業已經進入了一個全新的一體化時代;每個網絡運營商都在尋求更緊湊、多頻帶基礎架構解決方案。新興射頻類數據轉換器——RF DAC 和RF ADC —— 在架構上使創建緊湊的多頻帶收發器成為可能。但這些新興器件固有的非線性將成為這一發展趨勢的絆腳石。

例如,頻域中射頻器件的非線性包括帶內和帶外兩種情況。帶內非線性是指TX 頻帶內不需要的頻率成分(frequency term),而帶外非線性則是指TX 頻帶外不需要的頻率成分。

對于正在使用RF DAC 對多頻帶發射器進行原型設計的系統工程師而言,確保關鍵組件符合標準線性要求是非常重要的。因此,在早期原型設計階段,從根本上需要一個靈活的測試平臺,以正確評估AR DAC 在多頻帶應用中的非線性性能。

在愛爾蘭貝爾實驗室,我們已經創建了一個靈活的軟硬件平臺,可用于快速評估下一代無線系統潛在備選設備RF DAC。這個研發項目的三個關鍵因素分別是:賽靈思高性能FPGA、賽靈思IP 和MATLAB?。

在開始這段工程設計傳奇故事之前,我們還要強調幾點。在設計中,我們試圖盡量減少FPGA 資源的占用,同時盡可能保持系統靈活,所以我們只需要集中精力實現必要的功能。為建立完整的測試系統,我們選用ADI 公司的最新RF-DAC 評估板(AD9129 和AD9739a)和賽靈思ML605 評估板。ML605 評估板配套提供Virtex?-6 XC6VLX240T-1FFG1156 FPGA 器件,其包括快速切換I/O ( 頻率高達710 MHz) 和SERDES 單元( 頻率高達5 Gbps),用于連接RF DAC。

現在,讓我們仔細看看如何使用賽靈思FPGA、IP 和MATLAB 創建這個簡單而又功能強大的測試平臺。

系統級要求與設計

該評估平臺的主要目的是通過各種用戶自定義的測試數據序列來激勵RF DAC。為此,我們設計了兩個測試策略:連續波(CW)信號測試(xDDS)和寬頻帶信號測試(xRAM)。

多頻音連續波(CW)測試一直是RF 工程師對RF 元件非線性進行特性描述的首選。遵循相同的測試理念,我們創建了一個基于直接數字綜合器(DDS)的可調四音邏輯內核,實際上是采用一對雙音信號在兩個獨立頻帶上激勵RF DAC。通過獨立調諧四音,我們可以評估RF DAC 的線性性能- 即頻域內的互調位置與功率。

連續波(CW)信號測試是一種固有窄帶操作。為進一步評估RF DAC的寬頻帶性能,我們需要通過并發多頻、多模信號(如分別為2.1 GHz 和2.6 GHz 的雙模UMTS 和LTE 信號)對其進行激發。為此,我們創建了一個基于片上BRAM 陣列的數據存儲內核;該內核有兩個子組,可以為重復測試存儲各自的雙頻用戶數據。

圖1 顯示了簡化的系統級平臺設計圖。可以看到,我們采用簡單直觀的設計策略,構建盡量簡單的平臺并通過升級功能對其進行模塊化。

圖1 - 簡化的系統級平臺方框圖

硬件設計:賽靈思FPGA內核圖1 中的FPGA 部分列出了系統基本需要實現的邏輯單元。包括時鐘分布單元、基于狀態機的系統控制單元和基于DDS 內核的多音生成單元,以及嵌入在RAM 周圍的兩個單元:基于BRAM 的小型控制消息存儲單元(cRAM 內核) 和基于BRAM 陣列的用戶數據存儲單元 (dRAM 內核)。還包括連接PC 的UART 串行接口和連接RF DAC 的高速數據接口。

時鐘是FPGA 的生命脈搏。為確保多款時鐘在FPGA Bank 上正確分配,我們選用賽靈思時鐘管理內核,為時鐘的定義和指定提供一種簡單的交互方式。

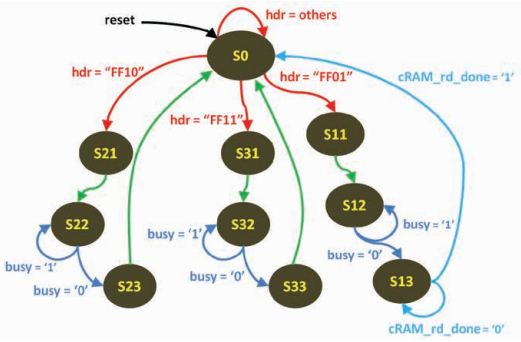

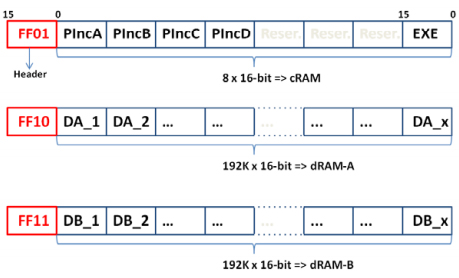

嵌入狀態機周圍的小型指令內核用作系統控制單元。如圖2 所示,在初始狀態(S0)下,報頭檢測器單元工作,負責監測并過濾來自UART 接收器的輸入數據字節。數據字節被生成并封裝在MATLAB 數據幀內(如圖3 所示)。

圖2 - 關鍵狀態機詳細設計圖

圖3 - 數據幀封裝例解

系統中基本上有兩種類型的數據幀。帶報頭“FF01”的數據幀(cRAM幀)用來為DDSes 和系統控制消息傳輸相位增量值。帶報頭“FF10”或“FF11” 的其他數據幀(dRAM 幀)用來傳輸用戶自定義的數據。狀態幀“S1x”只處理帶報頭“FF01”的數據,用以更新相位增量值和執行控制指令。狀態幀“S2x”和“S3x”分別為兩個頻帶接收并存儲用戶自定義數據。占線信號用來連續鎖存數據,直至看到數據序列末尾的最后停止位。控制消息—— 例如調用單個/ 多個DDS 或用戶數據序列—— 存儲在cRAM 數據幀的最后兩個字節內。它們將在cRAM_rd_done 信號上升沿處執行。

然后,我們舉例說明四個采用賽靈思DDS 內核的獨立的頻音生成單元,并將其配置為相位增量模式。特定頻率的相位增量值在MATLAB上生成并通過cRAM 數據幀下載到FPGA。通過混頻器,我們將多個頻音組合在一起,并通過管道將這些頻音輸送至下一級。由于DDS 內核輸出是二進制補碼格式,如果RF DAC需要另一種數據格式,如偏移二進制碼,則需要格式轉換單元。

一般來說,高性能片上BRAM通常是創建中小型用戶存儲系統的首選。例如,在這個平臺上,我們利用賽靈思 模塊存儲生成器(Block Memory Generator)內核為兩個頻帶創建兩個獨立的數據存儲RAM。每個RAM 的寬度為16 位,深度為192k。

對于PC 與FPGA 之間的通信,我們創建了一個UART 串行接口單元并將其設置為相對較低的速度,即921.6 kbps(相當于115.2 字節/ 秒)。傳輸cRAM 數據幀(18 字節) 和dRAM 數據幀(約384k 字節)分別需要約0.16 毫秒和3.33 秒時間。

器件廠商通常會以VHDL 或Verilog 格式提供芯片高速數據接口的實例設計。對于經驗豐富的FPGA工程師而言,復用或定制參考設計并不是很難。例如,就我們系統的AD9739a 和AD9129 RF DAC 而言,ADI 公司會提供并行LVDS 接口的參考設計。順便提一下,如果無法從芯片廠商處獲得實例設計,賽靈思有幾款簡單易用的高速接口芯片,如CPRI和JESD204B。

軟件設計:MATLAB DSP功能與圖像用戶界面(GUI)

我們選擇MATLAB 作為軟件主機,只是因為它在數字信號處理(DSP)性能方面具備諸多優勢。另外,MATLAB 還為圖形用戶界面(GUI)的布局提供一種稱為GUIDE 的簡便易用的工具 。所以現在,對于這個項目,我們需要從MATLAB 獲得什么?

事實上,我們需要與低級DSP功能和數據流控制功能相關的用戶界面。所需DSP 功能為相位增量值計算器、基帶數據序列發生器和數字上變頻器。控制功能為數據幀封裝器、UART 接口控制器和系統狀態指示器。

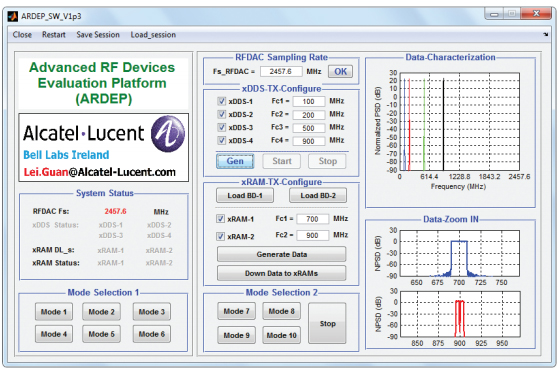

圖4 - 圖形用戶界面截圖

圖4 顯示了我們為該平臺創建的圖像用戶界面(GUI)。應首先定義RF DAC 關鍵參數—— 采樣率,然后才能選擇xDDS 模式或xRAM 模式激勵器件。然后,在各個子面板上,我們可以自定義參數,以調用相應MATLAB 信號處理功能。在xDDS 模式下,可以通過簡單方程式,phase_incr = fc*2nbits/fs,計算頻音fc 與采樣率fs 的相位增量值。其中,nbits 表示DDS 用來綜合頻率的二進制位數量。按下“啟動”按鈕,生成的相位增量值會轉化成定點格式并封裝在帶不同報頭和控制消息的2 字節數據幀內(如圖3 所示),然后通過UART 發動至cRAM 單元并在FPGA 內執行。

在xRAM 模式下,我們生成基帶數據序列,將其標準化為滿刻度(帶符號的16 位)并將其上變頻為在MATLAB 下所需的頻率。通過UART將處理過的數據下載到dRAM 之后,按下啟動按鈕,我們就可以調用寬頻帶信號測試。切記,要用FPGA 側所用相同協議參數在MATLAB 配置UART 串行接口。

最后,我們采用信號發生器——R&S SMU200A —— 來提供采樣時鐘,從而從邏輯上“開啟”RF DAC。我們還將RF DAC 輸出連接至頻譜分析儀,來評估頻域內RF DAC的線性性能。

快速評估

在原型設計的早期階段,關鍵RF 組件的線性性能評估是一個關鍵問題,但通過我們的軟硬件平臺,在不影響性能的條件下可以快速進行這項評估。然后,可以添加RF 功率放大器并使用所建議的平臺來評估級聯系統的線性。在確定非線性之后,可以執行一些數字預失真算法來消除級聯系統不必要的非線性。

在FPGA 設計中合理使用賽靈思IP 核可以大大縮短開發周期并提升數字系統的穩健性。展望未來,我們預計會將平臺上的數據接口模塊升級至JESD204B 標準,以支持更高數據傳輸速率,從而滿足多個同步RF DAC 需求。同時,我們正在將FPGA主機從賽靈思ML605 遷移至Zynq®-7000All Programmable SoC ZC706 評估套件。Zynq SoC 設計是在單臺PC上創建無需任何外部DSP 和控制功能的獨立解決方案的一個很好的選擇。

如需了解有關平臺和數字預失真的更多信息,敬請發電子郵件至lei.guan#alcatel-lucent.com ,與作者取得聯系。

作者:Lei Guan 技術人員Alcatel Lucent Ireland公司貝爾實驗室

粵公網安備 44030902003195號

粵公網安備 44030902003195號