摘要

隨著ADC和DAC的性能規(guī)格、形狀參數和新的傳感器技術(Rx和Tx)的不斷發(fā)展,RF數據轉換系統正在發(fā)生快速變化。在這期間,一個系統級的設計問題一直存在,即如何平衡模擬和數字電路的設計,以實現最大的軟件/系統靈活性(從傳感器到數字處理單元的輸入/輸出)。這個基本問題需要系統設計師劃分(或組合)數據轉換電路器件,并結合模擬和數字信號的布線,實現多種服務的軟件最大化。現在,隨著高級的SiP(系統級封裝)組裝技術的發(fā)展,數據轉換器系統的設計正逐步從硬件中心向軟件中心轉變。Teledyne e2v的SiP設計、發(fā)展和組裝的專業(yè)技術革新了系統級設計,可實現最大的靈活性并支持多任務的應用。利用最先進的技術(倒裝芯片、有機封裝等)開發(fā)的RF混合信號數字處理應用可用于工業(yè)、醫(yī)療、航空電子、儀器、電信、軍事和宇航等應用。Teledyne e2v在高級SiP設計和組裝技術方面擁有超過40年的經驗,可幫助系統設計師實現高級數據轉換系統平臺的最高性能和最大價值。

用于SiP設計的高級數據轉換器件

高頻數據轉換器系統需要高性能(和可靠的)半導體器件來處理整個信號鏈的關鍵功能。選擇可以滿足整個系統性能要求的合適的半導體器件對SiP的實現至關重要。Teledyne e2v為SiP的實現提供了高速數據轉換器、微處理器、存儲器以及各種模擬和邏輯功能器件。

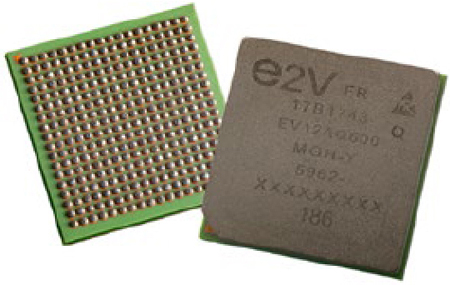

顯然,數據轉換接收(Rx)系統的核心器件是ADC。Teledyne e2v在過去的20多年里一直致力于數據轉換器技術的創(chuàng)新,并提供了多通道、低噪聲、低失真的微波頻率ADC(如上圖的EV12AQ600)。這種數據轉換器使系統設計師能(通過直接RF轉換)消除傳統架構中下變頻所需的模擬環(huán)節(jié)。利用Teledyne e2v的高端ADC減少模擬環(huán)節(jié),并使用高級的SiP設計技術配合無需許可證的標準和定制解決方案,設計師可以研發(fā)許多標準產品和定制產品,以滿足特定的性能和/或環(huán)境需求。

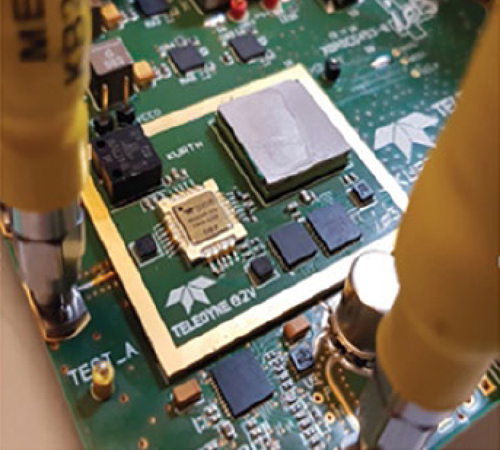

未來高速SiP直接RF數據轉換接收(Rx)方案的核心是EV12AQ600。結合RTH120跟蹤保持放大器(THA),PS620實驗SiP RF前端接收板(如下圖所示)的性能非常優(yōu)秀(見第2頁上器件的核心參數)。EV12AQ600是一款四核ADC,包含交叉點開關(CPS)前端,允許四個ADC核心同時、獨立或成對地工作,支持四通道1.6Gsps,兩通道3.2Gsps或單通道6.4Gsps的采樣率。典型的四通道模式的SFDR(不考慮H2和H3諧波)優(yōu)于70dBFS(-1dBFS輸出,頻率高達5980MHz)。

這款器件可提供多種級別,包括商業(yè)級、工業(yè)級、軍級,最高支持耐輻射宇航級。EV12AQ600可用于多種應用,如高速數據采集、高速測試儀器、自動測試設備、地球觀測SAR雷達載荷、電信MIMO衛(wèi)星載荷、超寬帶衛(wèi)星數字接收機、C波段直接RF轉換、微波軟件定義無線電、點對點微波接收端、機器狀態(tài)監(jiān)測系統、飛行時間質譜分析、LiDAR、高能物理等。

|

器件核心參數 EV12AQ600 ADC: • 四個12-bit 1.6 GSps ADC核心,支持1、2或4通道時域交織• 全交織模式采樣率高達6.4 GSps • 6.5 GHz輸入帶寬(-3dB) • 集成的寬帶交叉點開關 • 支持多通道同步的同步鏈 RTH120 THA: • 24GHz 輸入帶寬• 雙THA使輸出保持時間超過半個采樣時鐘周期 • 全差分設計 |

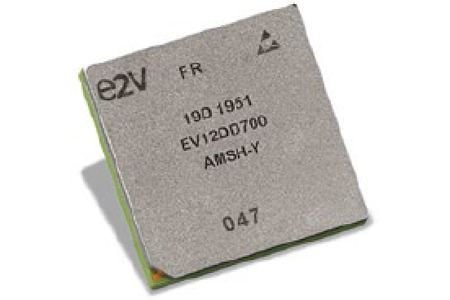

在實現高速、最先進的SiP數據轉換發(fā)射端(Tx)解決方案方面,關鍵的技術是EV12DD700(如圖所示)。

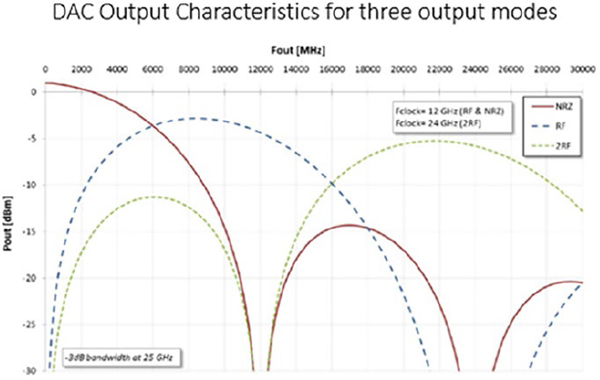

該雙路12位DAC支持高達12Gsps的采樣率,可直接產生高達21GHz的輸出信號,滿刻度階躍響應時間低至15ps,在微波頻率的噪聲很低,性能優(yōu)秀。EV12DD700雙通道DAC也支持Ka波段工作,支持波束形成的應用。這款DAC有25GHz的3dB輸出帶寬,即使超過25GHz也僅有略大于3dB的衰減(見下圖)。

每個DAC都集成了一系列復雜的信號處理功能,包括一個用于直接數字合成(DDS)功能的可編程anti-sinc濾波器,一個可編程的復雜混頻器,以及一個包含四個插值環(huán)節(jié)的數字上變頻器。數字處理功能包括:插值(4x, 8x和16x)、帶有數字控制振蕩器(32位NCO)的數字上變頻(DUC)、直接數字合成(DDS)、數字波束形成和波束跳變。DAC的主要功能包括:可編程輸出模式(NRZ, RF, 2RF)、增益調節(jié)、可編程SINC補償功能和多器件同步。

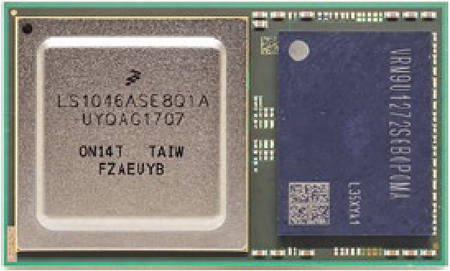

當然,所有的高速數據轉換系統也需要先進的數字處理能力。例如,Teledyne e2v已經認證并發(fā)布了一款從NXP最新的Layerscape® 系列篩選出的微處理器LS1046A,可工作在-55℃到125℃(宇航級LS1046-Spacce也很快會發(fā)布)。LS1046A是NXP的64位ARM® Layerscape產品系列的一款器件,使用四核ARM® Cortex® A72設計。

這種設計在盡可能小的封裝里實現了無與倫比的性能。用戶可以使用與ARM® 技術兼容的龐大的軟件、應用、工具的生態(tài)系統。LS1046A是一款1.8GHz的處理器,集成了包處理加速和高速外設,使用了高性能的架構,有業(yè)內領先的計算密度。其超過45,000CoreMarks® 的計算性能(即30K DMIPS@1.8GHz),搭配雙路10Gb以太網、3路PCIe Gen3和1路SATAGen3,適用于一系列高可靠性的軍用、航空和航天的應用。LS1046A也集成到了Teledyne e2v最新的Qormino® 計算模塊中,這個模塊還包含了一個4GB的DDR4存儲器(見左側的照片)。此外,作為Teledyne e2v的半導體生命周期管理計劃SLiM™的一部分,這款器件的生命周期可達15年以上,避免了常見的昂貴的器件過時問題。

數據轉換SiP實現峰值系統性能:適用于所有細分市場

在工業(yè)、醫(yī)療、飛行電子、儀器、電信、軍事和宇航領域,數據轉換系統正在經歷快速的變化。對于所有的細分市場,首要的系統級設計問題是,如何在模擬和數字電路之間取得平衡,實現最大的軟件/系統靈活性(從傳感器到計算機輸入或從計算機輸出到傳感器)。這個基本的問題要求系統設計師劃分(或組合)數據轉換電路器件,并結合模擬和數字信號的布線,以實現多種服務的軟件最大化。

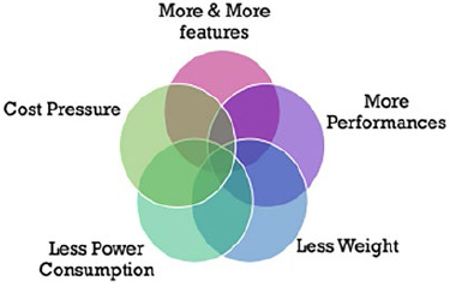

系統工程師了解他們的市場、應用和電路性能的規(guī)范需求,但設計參數,例如風險、技術選擇、形狀參數、開發(fā)時間表(包括時間表同步)、可靠性,以及與高性能數據轉換系統相關的成本,都是高度可變的。這些設計參數,加上不斷變化的系統性能規(guī)格需求,最終導致更窄的設計實現“交集”(圖2)。

圖2 - 不斷增加的設計參數和系統級性能需求,產生了更窄的“交集”。

當然,在任何設計參數上犯錯誤,都會付出巨大的代價。因此,任何可以嵌入到設計開發(fā)中的靈活性,只要能為項目增加整體價值而不是降低價值,都是值得投資的。

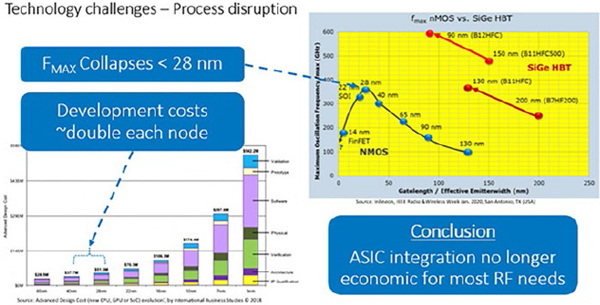

有一個設計參數可以提高設計階段的靈活性,并最終滿足必要的性能需求,特別是對于數據轉換系統。它是利用SiP(系統級封裝)技術實現所需的功能。過去,半導體工藝技術的不斷進步使系統級設計師能夠在SoC(片上系統)上實現完整的電路功能。隨著門電路長度縮短至10nm甚至更小,需要大量數字計算的SoC應用已可以通過半導體技術實現。不幸的是,隨著半導體特征尺寸的減小,芯片的開發(fā)成本呈指數級增長(見圖3)。

圖3

圖3也顯示了最小幾何門尺寸和最大器件振蕩頻率之間的相關性。如圖所示,Fmax的拐點在門長度<28nm的位置。相應的,隨著門長度的減小,開發(fā)成本呈指數增長(G=28nm(平均開發(fā)成本5130萬美元),G=16nm(平均開發(fā)成本1.063億美元),G=7nm(成本2.97億美元),G=5nm(成本超過5億美元) )。

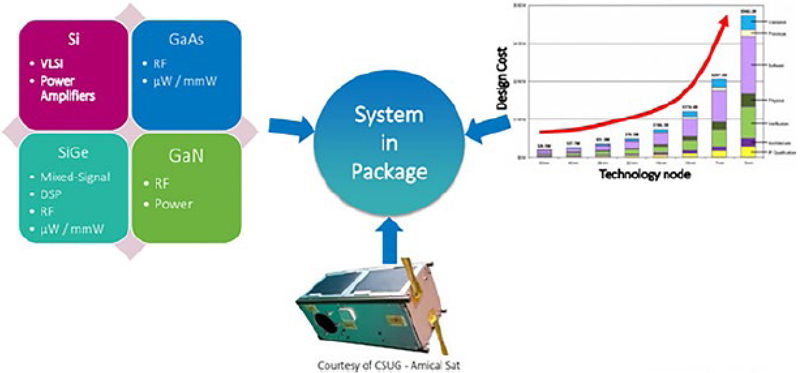

隨著SoC包含更多的功能,需要使用更小的門長度,其開發(fā)的成本變得令人望而卻步。例如,SoC一直是移動電話行業(yè)的驅動技術,但對模擬技術(如MEMS傳感器)的需求不斷增加,導致從SoC到SiP方案的變革。圖4說明了當前推進從SoC到SiP的變革的三個共存的設計參數:1)技術:為最優(yōu)系統性能選擇最合適的工藝技術(即Si、GaAs、GaN、SiGe等),2)小型化,3)成本。

圖4

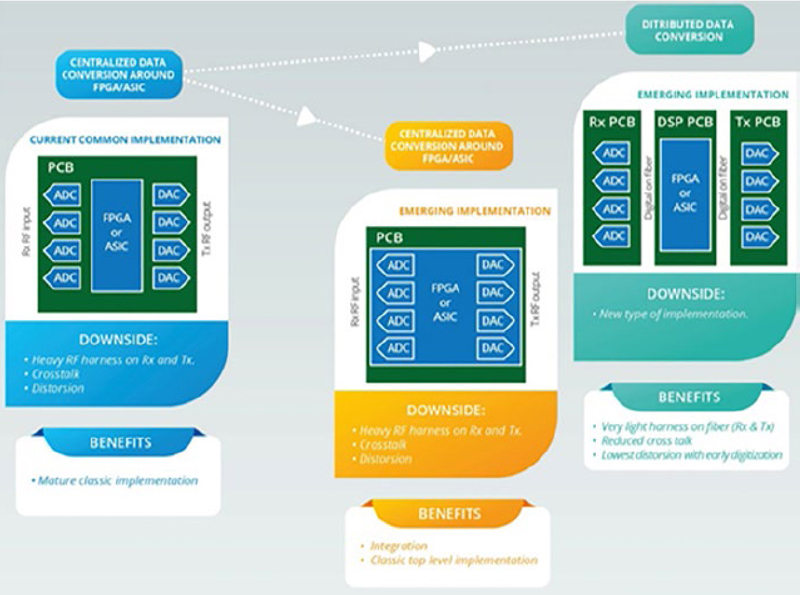

推動數據轉換系統從SoC向SiP發(fā)展的另一個因素是對數據轉換電路器件的劃分(或組合)以及模擬和數字信號的布線,這將允許對多種服務進行最大程度的軟件化。簡單來說,數據轉換系統可以設計為“集中式”或“分布式”系統(見圖5)。集中式數據轉換系統需要大量的模擬信號布線,因此會有額外的串擾和失真。相比之下,分布式數據轉換系統可以將ADC放在Rx傳感器上,將DAC放在Tx傳感器上。數字信號可以通過輕便、緊湊的高速光纖傳遞。

圖5

因此,Teledyne e2v的高級的SiP設計、開發(fā)和組裝的專業(yè)技術使數據轉換系統的開發(fā)發(fā)生了巨大的變革,實現了多任務應用設計參數的最大靈活度(即組合和劃分)。通過使用最先進的技術(焊線、倒裝芯片等),組合(或劃分)RF、混合信號和數字處理半導體,高級的SiP設計和組裝技術能為系統設計師帶來最高性能、最低成本的高頻數據轉換系統平臺。

例如,圖6的PS640是一款SiP實現的RF數據轉換系統產品,目前正在研發(fā),用于未來的L波段到Ka波段的頻率接收機(1GHz至40GHz)。

圖6a

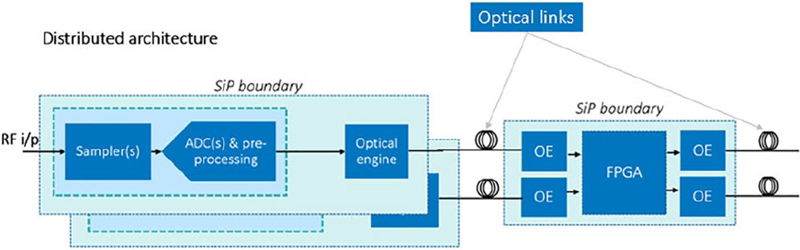

PS640使用Teledyne e2v基于STMicro BiCMOS055工藝設計的新型THA和兩片互相交織的EV12AQ600ADC,是一款“集中式”的高速SiP數據轉換接收器(Rx)。圖6也描述了其性能指標。圖7描述了一種相同的數據轉換系統的未來概念,這是一種“分布式”數據轉換接收器的實現方式,使用光引擎(包含在SiP中)驅動數字處理器(FPGA),實現最大軟件化(軟件中心)。

圖6b

圖7

TE2V的高級SiP組裝技術

SiP是將多個器件(主動器件或被動器件)封裝在一起的單個設備。SiP用于在電子系統層面執(zhí)行多項功能。嵌入在SiP中的半導體器件(包括被動器件)可以水平和/或垂直堆疊在基材上,然后進行封裝。半導體可以通過焊線或焊接凸點的方式與基材連接(也可以用于將裸片堆疊成垂直的結構)。

如前所述,數據轉換SiP可能包含多個裸片,如前置放大器、混頻器、ADC、DAC,專用處理器、存儲集成電路和被動器件(如電阻和電容)。這些裸片是使用不同的安裝技術固定在同一個基材上。SiP的組裝技術促進了細分市場的發(fā)展,特別是與超高RF(地面和非地面)、需要MEMs電路的物聯網(IOT)、移動和可穿戴設備等應用相關的領域。憑借一系列的使用SiP技術的產品和封裝解決方案,Te2v為工業(yè)、醫(yī)療、航空、軍事、科學和空間等應用的細分市場提供設計和組裝服務。此外,Teledyne e2v的許多產品都是通過與NXP、Everspin、Micron等公司的戰(zhàn)略合作開發(fā)的。

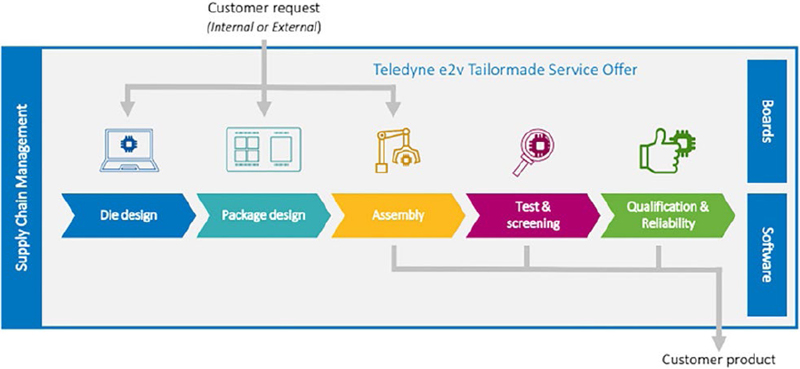

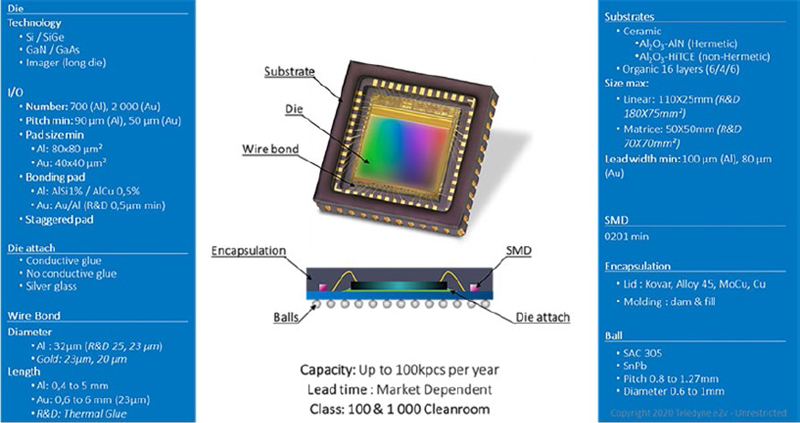

Te2v可提供一系列SiP設計開發(fā)的供應鏈管理服務,包括:裸片設計、封裝設計、高可靠組裝、高性能速度測試、質量服務和半導體生命周期管理(SLiMTM,見圖8)。Te2v擁有超過40年的宇航設計經驗,包括ADC、DAC、微處理器、存儲器以及內部測試和質量服務,能為所有細分市場提供滿足任何質量等級需求的高級SiP的產品和服務。Te2v的高級的SiP組裝技術包括:焊線、倒裝芯片、有機和陶瓷封裝(密封和非密封)以及混合組裝。

圖8

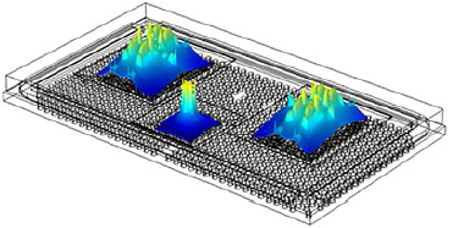

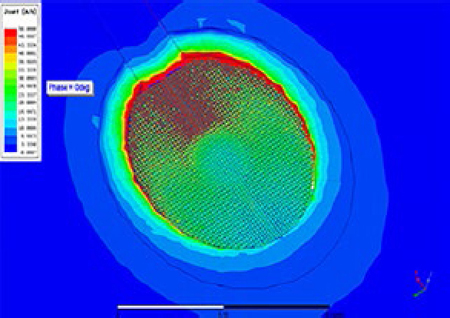

當然,在組裝之前,高級高速SiP開發(fā)需要封裝仿真和封裝參數的測試,以評估散熱和可靠性。例如,圖9介紹了上文提到的PS640的熱仿真。對于散熱設計,將多個裸片緊密地放置在一起是一個挑戰(zhàn)。為了準確預測器件最關鍵區(qū)域的結溫,需要進行仔細的熱仿真。Te2v使用與設計師和客戶討論商定的邊界條件,使仿真的性能匹配最終的測試結果(這對于SiP集成的關鍵器件是必需的)。此外,Te2v使用高頻3D場解算器(Ansys HFSS)對RF SiP的開發(fā)進行仿真和設計。

圖9 - PS640 SiP的熱仿真

HFSS是一款用于電磁結構的商業(yè)有限元方法解算器,適用于SiP封裝包含的復雜RF電子電路/半導體器件、濾波器、傳輸線的封裝設計(見圖10)。

圖10 - 對PS640 進行40GHz 模擬輸入的3D 場解算器仿真(Ansys HFSS) 顯示封裝到THA 的裸片之間的連接狀況,并分析了硅金屬填充里的信號傳遞。

在這個例子里,Te2v的封裝團隊和負責Te2v的SiP開發(fā)流程的半導體團隊共同設計了這個RF模擬前端。

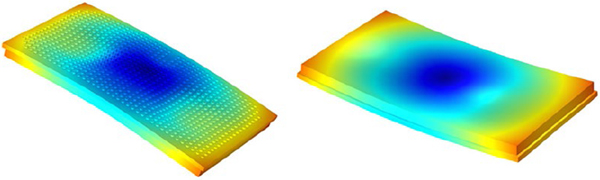

由于嵌入在單個有機基材里的硅技術有所不同,以及C4(受控塌陷芯片連接- 倒裝芯片凸點)和C5(焊球)機電接口中的RoHS焊點,SiP設計的可靠性是一個重大的工程挑戰(zhàn)。Te2v不斷開發(fā)新技術,通過熱機械分析,并考慮諸如焊料蠕變和粘塑性等的非線性行為,快速并準確地預測產品的翹曲和板級的可靠性(見圖11)。

圖11 - PS640 在室溫組裝后發(fā)生的封裝翹曲的50 倍放大圖

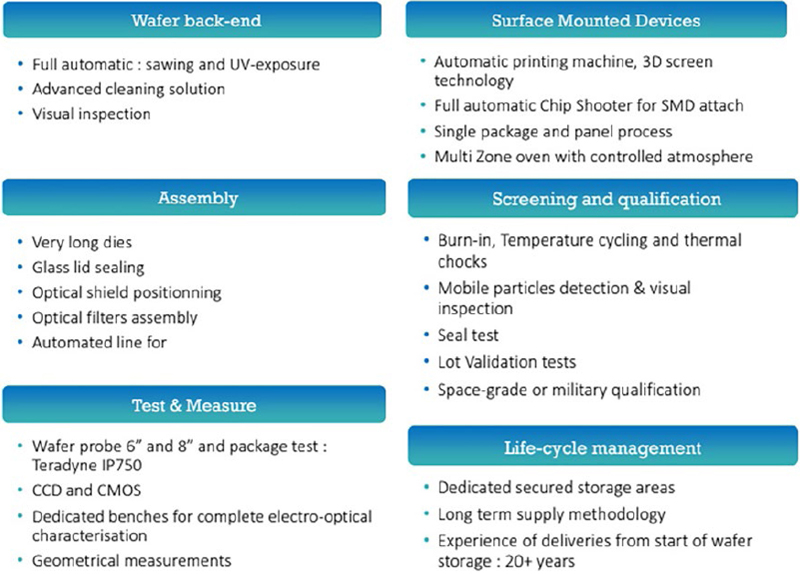

具體的設計和組裝服務還包括:定制產品、中/低用量產品、高可靠/高端產品、QML-V/QML-Y認證以及宇航認證(參考圖12中的技術總結):

圖12 - Te2v 的高級組裝技術,可用于SIP 的組裝

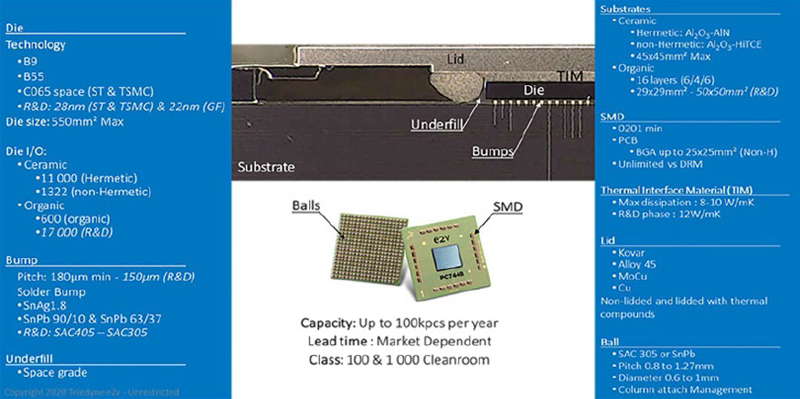

圖13說明了Te2v的高級SiP焊線和倒裝芯片組裝技術。對于焊線,圖13(上圖)說明了滿足不同半導體類型(Si、GaN、GaAs等)和封裝類型的最新發(fā)展所需的眾多組裝技術。隨著新一代的半導體和封裝的發(fā)布,必須開發(fā)新的焊線技術,以滿足性能的要求。焊線大約占所有電子封裝組裝(包含flash存儲器和傳感器等)的三分之二。對于一些硅節(jié)點,如MEMS傳感器,無法使用先進的倒裝芯片互聯技術。在這些情況下,焊線依然具有成本和可靠性方面的優(yōu)勢。

圖13 - Te2v 的高級焊線(上)和倒裝芯片(下)技術,可用于SIP 的組裝

倒裝芯片技術(也如圖13所示)基于半導體頂部形成的一系列凸起或銅柱。倒裝芯片的流程和傳統IC的制造類似,只需要增加幾個步驟。在制造過程接近尾聲時,對焊盤進行金屬化或焊料預處理,使其更容易焊接。在最后的晶圓流程中,焊接凸起會在晶圓頂部的芯片焊盤上形成,然后像往常一樣從晶圓上切下芯片。為了將芯片安裝在外部電路(SiP電路板和/或另一個芯片或裸片)上,需要翻轉芯片使其頂部朝下,并使它的焊盤與外部電路的焊盤對齊,然后進行回流焊(通常使用熱超聲焊接或回流焊接),以使它們互相連接。這會在芯片電路和底部之間留下了一個很小的空間。在很多情況下,需填充電氣絕緣的粘合劑,以保證更強的機械連接,并產生熱橋,確保焊點不會由于芯片和系統的其他部分的熱量不同而受到應力。這些填充物減少了芯片和板子之間的熱膨脹系數的不匹配帶來的影響,防止應力集中于焊點,防止器件過早失效。倒裝芯片技術與焊線技術不同,在焊線技術中,芯片被簡單地安裝,然后用線將芯片的焊盤和外部電路連接起來。

TE2V:為高級SiP的設計和組裝提供一站式服務

在性能生命周期內,SiP可降低特定產品和系統的總體成本,特別是與其他設計選項(如SoC等)相比時。SiP可在產品生命周期的各個階段減少總體的系統開發(fā)成本,如:

1. 降低工程成本:在工程開發(fā)時間、材料和上市時間方面顯著降低設計的難度。2. 降低PCB成本:簡化特定器件的開發(fā)和使用(利用COTS或定制半導體)。

3. 降低組裝成本:將多個器件集成到一個封裝里,可在系統整體制造流程中顯著降低成本。

4. 降低供應鏈成本:簡化供應鏈。來自不同制造商的多個器件可被單個SiP取代,這樣只需管理較少的供應商和器件,可大大簡化供應鏈。

5. 驗證:子系統和系統級的測試和認證。

Te2v的高級SiP設計和組裝服務成為所有細分市場和產品類型的“一站式商店”(參見圖14)。簡單來說,Te2v不但為宇航級的應用提供設計、組裝和認證服務,也面向其他所有的細分市場、應用和質量等級。

圖14

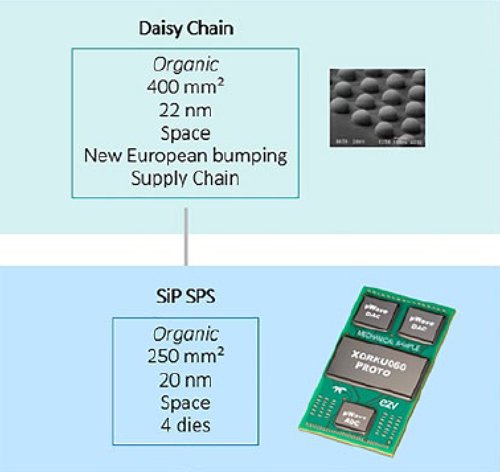

最后,隨著高級系統的發(fā)展進入下一個十年,SiP技術已成為減少門長度、減小半導體尺寸的關鍵要素。隨著越來越大的SoC逐漸成為SiP包含的眾多器件之一,使用有機基材和封裝材料進行可靠組裝(焊線或倒裝芯片)的技術需要大量的技術投資。當前,Te2v正準備在未來幾年內實現這類技術的進步,所有的技術研發(fā)都由ESA贊助。

結語

當前,數據轉換系統的設計師正在經歷半導體工藝選擇(和幾何尺寸)、電路小型化需求以及不斷增加的開發(fā)成本等關鍵設計參數的挑戰(zhàn)。此外,高級系統的開發(fā)可以使用越來越先進的ADC、DAC、微處理器和存儲器件。在工業(yè)、醫(yī)療、航空電子、儀器儀表、通信、軍事和宇航應用領域,一個系統設計的問題一直存在,即如何在模擬電路和數字電路之間取得平衡,以實現最大的軟件/系統靈活性(從傳感器到計算機輸入/輸出)。現在,高級SiP(系統級封裝)技術的發(fā)展在所有的細分市場和應用中推動了數據轉換系統的設計從硬件中心到軟件中心的變革。Teledyne e2v的SiP設計、開發(fā)和組裝的專業(yè)技術革新了系統級設計,實現了最大的靈活性和多任務的能力。Teledyne e2v擁有超過40年的RF、混合信號和數字處理應用的封裝設計經驗,其最先進的SiP設計和組裝技術(焊線、倒裝芯片、有機封裝等)將幫助系統設計師實現高頻直接RF數據轉換系統平臺的最高性能和最大價值。

粵公網安備 44030902003195號

粵公網安備 44030902003195號