作者:ADI系統(tǒng)工程師 Brad Brannon

摘要

O-RAN旨在推動無線社區(qū)轉型、開辟新無線設備通道和推動創(chuàng)新,以履行3GPP關于5G的承諾。1要取得成功并保持高性價比,必須提供開源的無線電設備和優(yōu)化的5G技術。本文將介紹其中一種用于設計和構建高功效比的解決方案。

5G帶來了哪些挑戰(zhàn)?

無線電和網絡工程師目前使用幾種技術來實現這些目標。除了將數據服務移動到網絡終端之外,還使用大規(guī)模MIMO和小型蜂窩技術來幫助提高容量和吞吐量。大規(guī)模MIMO技術在陣列中使用多個無線電,此舉不僅可以實現容量,還可以覆蓋中心位置。和它的前身宏蜂窩一樣,大規(guī)模MIMO無線電可以圍繞該位置提供相對廣泛的覆蓋范圍。但是,大規(guī)模MIMO無線電使用更高的頻率,一般是2.6 GHz及以上,這個頻率對建筑物的穿透性并不高。為了服務室內位置和其他難以到達的室外區(qū)域,我們將使用小型蜂窩。鑒于室內和室外位置的數量,從家庭到企業(yè)安裝,再到消費購物場所乃至競技場,小型蜂窩的使用將是5G取得成功的關鍵。由于網絡中需要使用數量龐大的小型蜂窩和多種部署,所以安裝和運行成本必須低廉;這是推動實現5G的關鍵。

可以使用哪些技術?

在過去幾年里,多種技術朝著支持5G解決方案的方向發(fā)展。首先,從基帶角度來看,摩爾定律不僅繼續(xù)降低每個柵極的硅成本,而且將更復雜的功能集成到無線電技術中。現在可以將許多所需的控制算法直接集成到無線電器件中,包括數字預失真(DPD)等功能。隨著新生代無線電的問世,出現了許多其他的可能性。

其次,像O-RAN2這樣的行業(yè)聯(lián)盟正在整個無線行業(yè)進行合作,以實現規(guī)模經濟,不僅可以降低成本,還可以提高供應鏈的安全性,并提供通過這些無線網絡盈利的新方法。具體來說,“O-RAN聯(lián)盟是由運營商建立的,旨在明確定義要求,并幫助建立供應鏈生態(tài)系統(tǒng)來實現其目標。為了實現這些目標,O-RAN聯(lián)盟的工作奉行“開放和智慧的原則”。3因此,他們側重于定義3GPP指定的物理接口,以實現標準化,并在行業(yè)中作為可互操作的白盒解決方案使用。此外,O-RAN還定義了硬件要求,并提供了O-CU、O-DU和O-RU(分別表示開放式集中單元、開放式分配單元和開放式無線電單元)的參考設計。它們會使前傳網路和基帶處理器實現標準化,進一步降低解決方案成本。它們與其他集成式5G器件(例如集成式無線電)一起,可用于定義小型蜂窩的發(fā)展,并推動實施這些標準。這些機構的工作是非常關鍵的一步。

第三,無線電技術在過去幾年中得到迅速發(fā)展。高性能無線電現在有多種架構,可以滿足3GPP在38.104和相關文檔中要求的性能標準。1這些無線電高度集成,不僅包含模擬和RF元件,還包括DPD和削峰(CFR)等關鍵算法。雖然這些無線電是基于細線CMOS構建的,但RF前端也在經歷其他發(fā)展,其中,低成本RF工藝(SiGe、SOI、GaN、GaAs等)正轉變?yōu)楦叨燃傻腖NA和高功率、高性能的PA,可以滿足這些標準的要求。

最后,提供高度集成和節(jié)能的解決方案,包括以太網供電(PoE)、標準電源器件、監(jiān)控和保護解決方案,它們尺寸緊湊,但可以提供所需的電源。這些解決方案在無線電環(huán)境中提供非常高的效率和非常低的噪聲,且提供選項,用于保護關鍵器件,例如功率放大器。

這些技術結合在一起,實現了低成本、高性能的小型蜂窩平臺,可以高效部署在運營商網絡中,以支持小功率和大功率系統(tǒng)。

系統(tǒng)概述

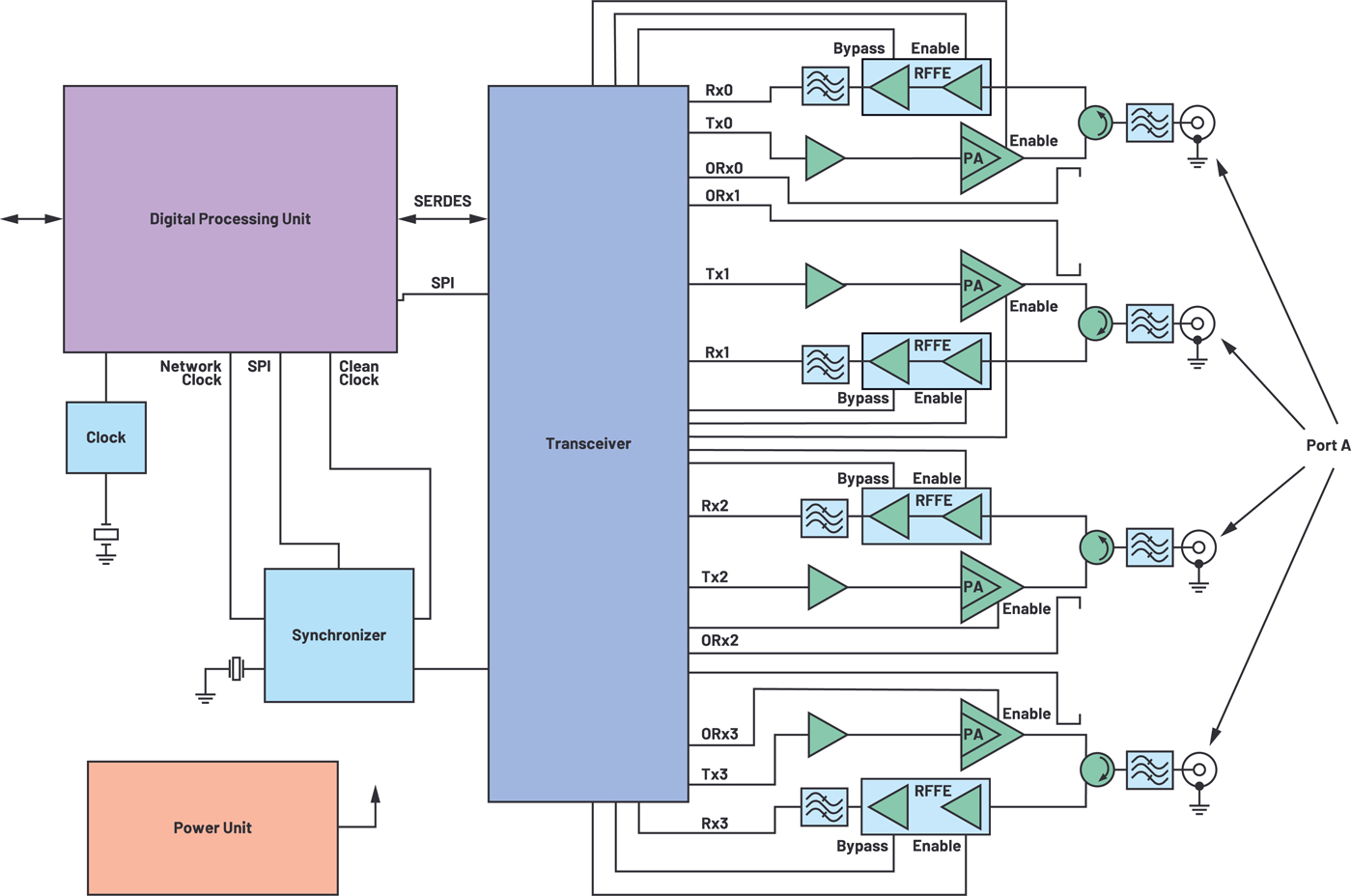

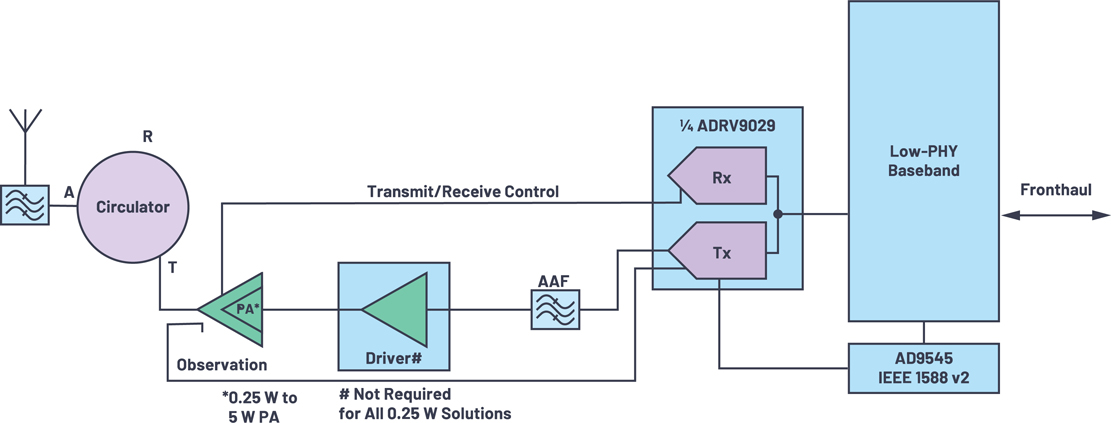

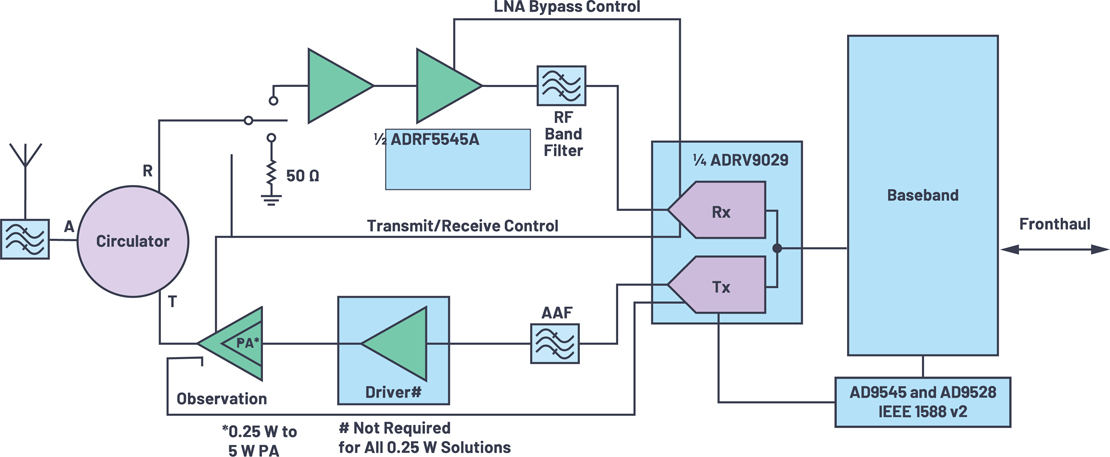

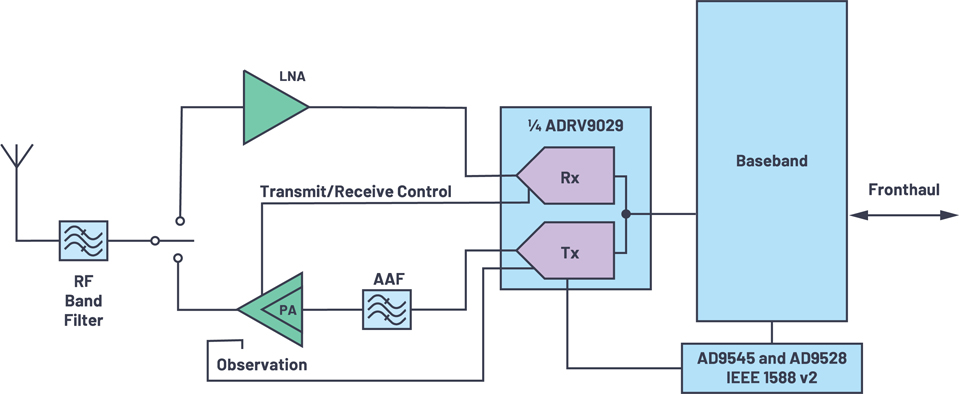

圖1顯示了典型的4T4R(4個發(fā)射器和4個接收器)5G小型蜂窩的框圖。可以采用多種排列,包括2T2R和一系列功率等級(從24 dBm和更高)。后續(xù)討論以此圖為基礎,主要介紹可以輕松擴展,適應O-RU中的頻段和功率變化的5G技術器件。

圖1. 小型蜂窩功能框圖

主要無線電元件

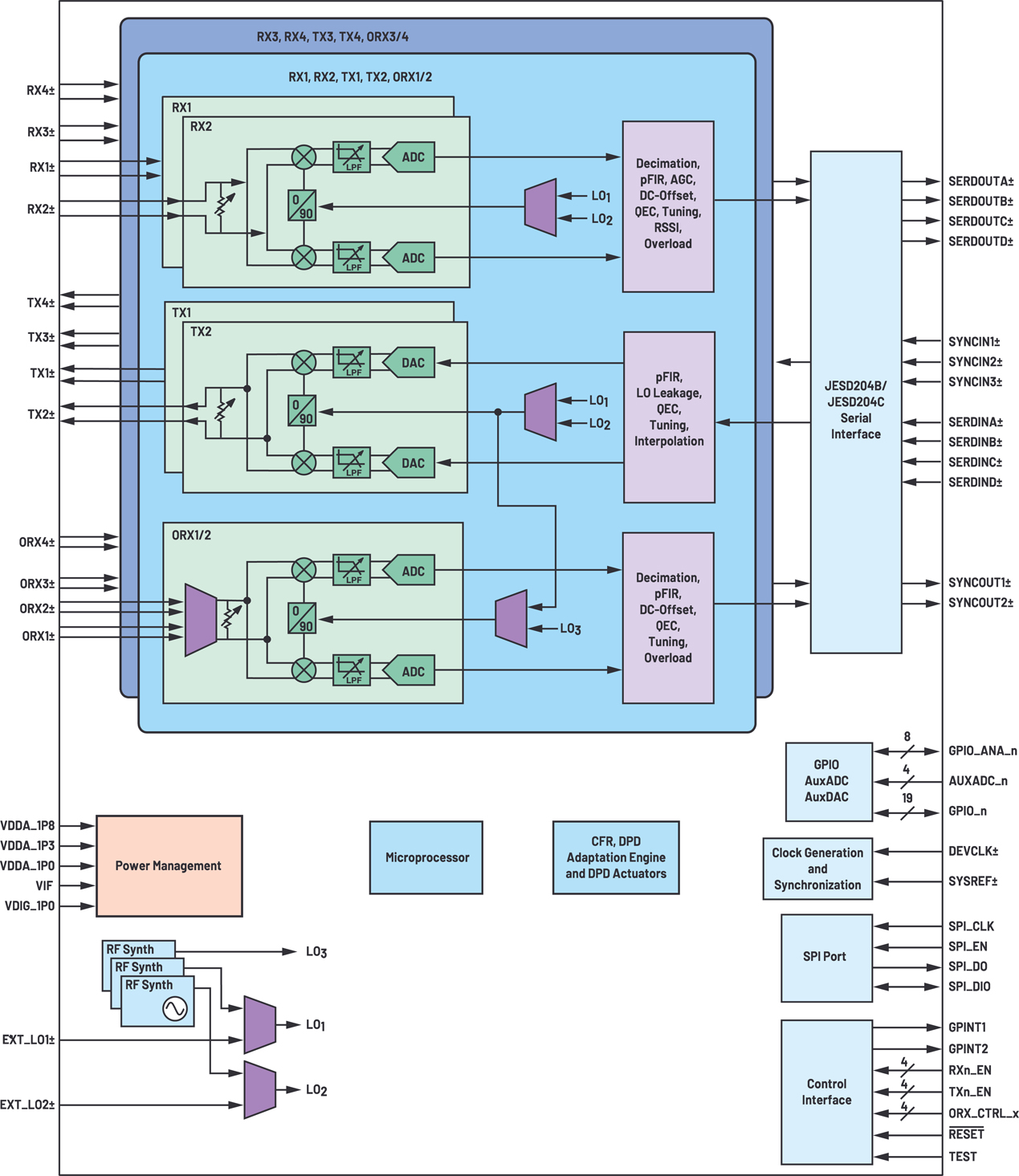

在過去10年,集成式收發(fā)器已發(fā)展成為高性能平臺。ADI RadioVerse™系列包含多種集成式收發(fā)器,它們支持高達200 MHz占用帶寬,集成了DPD等先進功能。該系列產品不僅滿足5G技術器件的要求,也一如既往地支持LTE和多載波GSM RF要求。對于這些器件,雖然我們在不斷進行新一代的開發(fā),最新一代如圖2所示,為ADRV9029,是一種4T4R配置。還提供其他產品,包括帶和不帶集成式DPD,以及采用包括2T2R在內的其他配置的器件。

每款RadioVerse器件都包含構建完整無線電所需的一切(LNA和PA除外)。這包括發(fā)送和接收、合成器和時鐘等所有功能。還包括運行AGC和增益控制放大器所需的狀態(tài)機和VGA。雖然RadioVerse產品都使用高達6 GHz的寬帶,但LNA和PA并非如此,必須制定頻段或頻率范圍。因此,為了完成無線電設計,必須將合適的LNA和PA與RadioVerse IC配對。以下章節(jié)將描述5G NR小型蜂窩的接收和發(fā)送信號鏈,并對如何選擇這些器件提供一些見解。

圖2. ADRV9029收發(fā)器

接收器信號鏈示例

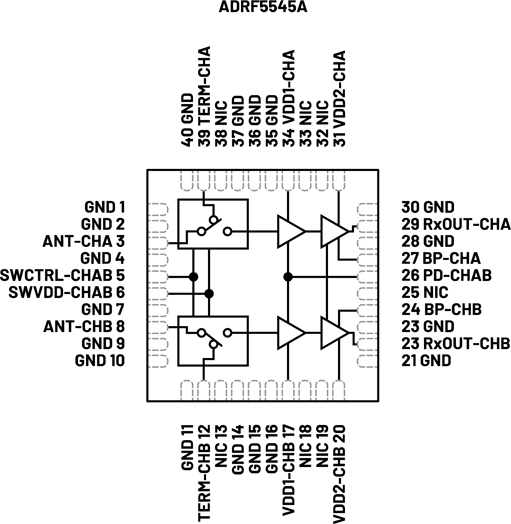

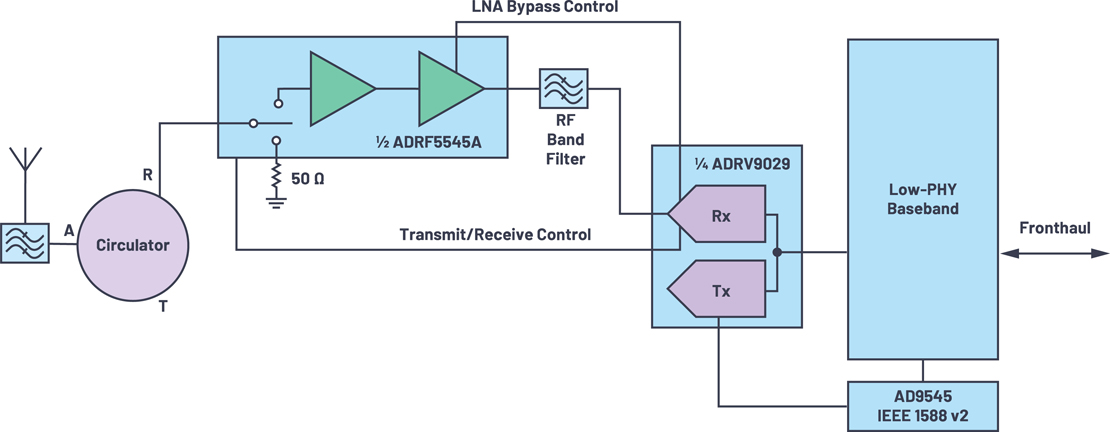

ADRV9029與ADRF5545A組合使用時(如圖3所示),可以輕松構建2芯片接收器。ADRF5515引腳兼容,也可以使用。它與幾個無源元件組合,就可以構成非常緊湊的高性能接收器設計,如圖4中的信號鏈所示。此架構的關鍵優(yōu)勢在于可能達到高水平集成,如此不但可以實現極低的實施成本,還能使功耗降至最低。4

RadioVerse系列的架構取消了經典接收器設計中常使用的許多元件,包括一些RF放大、濾波和剩余大部分無線電功能的集成,包括通道濾波器(模擬和數字)和基帶放大器。這些元件通常是系統(tǒng)中最大、功率最高的器件,相比包括直接RF采樣在內的其他架構,此架構可以顯著節(jié)省成本。

圖3. ADRF5545A雙通道TDD接收器前端

如圖4所示,小型蜂窩接收器系列包括環(huán)形器(適用于TDD應用)、ADRF5545A、SAW/BAW(表面聲波/體聲波)或整體式濾波器、巴倫和收發(fā)器。鑒于ADRV9029和RadioVerse系列中的其他產品具有出色的噪聲性能和低輸入IP1dB,所以無需使用其他放大器或VGA。使用這個信號鏈之后,從天線到數據比特位,可以支持整個系統(tǒng)低至2 dB的噪聲系數。雖然此設計中包含一個集成式RF前端模塊(FEM),但許多設計仍然使用分立式設計(此處不予詳述)。集成式FEM利用集成來滿足天線濾波器稍微提高的濾波器要求,但仍然提供對于許多高度集成的解決方案來說具有吸引力的設計,例如大規(guī)模MIMO和其他TDD部署。通常,使用分立式前端來實現FDD設計。

假設LNA之前的耗損為約0.5 dB,如果帶濾波器的耗損為1 dB,根據兩款有源器件的數據手冊規(guī)格,則整個接收器信號鏈的標稱NF應為約2 dB。假設與MCS-4一致的信噪比和信納比為0 dB,那么G-FR1-A1-1 5G載波(~5 MHz)的參考靈敏度為約-104.3 dBm。這足以滿足章節(jié)7.2.2中38.104的廣域傳導要求,且留有余量,對局域/小型蜂窩來說也綽綽有余,如表1所示,在這種情況下需要-93.7 dBm。一些低性能小型蜂窩應用可能能夠使用單級LNA,例如GRF2093,后接一個SAW濾波器。

圖4. 接收器信號鏈詳情

表1. 38.104接收器分類

|

|

廣域(dBm) |

中程(dBm) |

局域(dBm) |

|

5 MHz BW/15 kHz |

–101.7 |

-96.7 |

-93.7 |

|

20 MHz BW/15 kHz |

-95.3 |

-90.3 |

-87.3 |

|

50 MHz BW/30 kHz |

-95.6 |

-90.6 |

-87.6 |

|

100 MHz BW/30 kHz |

-95.6 |

-90.6 |

-87.6 |

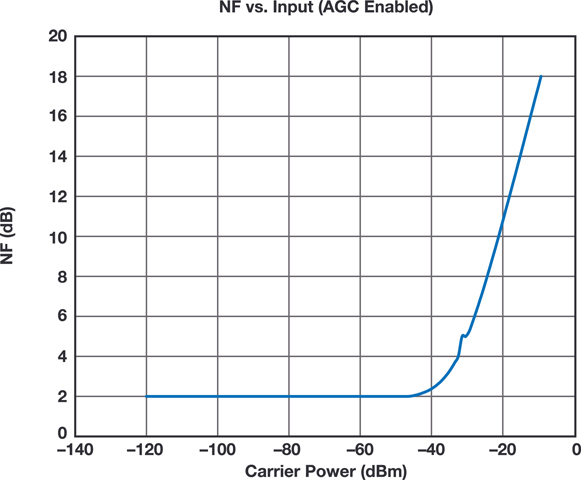

此外,38.104章節(jié)的7.4.1要求在低于-52 dBm(廣域)ACS阻塞下,接收器的衰減不超過6 dB。根據圖5所示的NF與輸入電平,在-52 dBm時產生的額外噪聲并不比在更低電平下產生的噪聲多。事實上,本底噪聲在Blocker信號達到-40 dBm后才會上升,非常適合需要-44 dBm容差的局域ACS。

一般阻塞要求(7.4.2)要求對相關頻段內的接收器施加-35 dBm(局域)的干擾,偏移為±7.5 MHz,衰減不得超過6 dB。從圖5顯示的ADI公司的信號鏈的性能來看,衰減僅為約0.9 dB。窄帶阻塞是一種功率稍低的CW類阻塞,但這也不是問題。

圖5. 接收器NF與輸入電平

章節(jié)7.5.2中的帶外阻塞可能算是一種更為有趣的挑戰(zhàn)。其中,-15 dBm信號被傳輸至天線輸入。對于頻率低于200 MHz的小型蜂窩,此信號最接近頻帶邊緣的頻率為20 MHz。測試要求對1 MHz至12.75 GHz范圍進行掃描,不包括20 MHz工作頻率以內的頻段。這里,有幾個因素會推動信號鏈產生優(yōu)勢。第一,環(huán)形器具有有限帶寬,會拒絕許多帶外信號,但包含在內的信號不會產生很大影響。第二,ADRF5545A之后的濾波器會提供一定程度的濾波,一般來說,對于帶外20 MHz,~20 dB抑制是合理的。第三,ADI收發(fā)器系列獨有且最有用的特性要屬內置的帶外抑制,這是收發(fā)器結構固有的特性。在ADI公司應用筆記AN-1354的圖20中,固有的帶外抑制被表示為增加的阻塞信號電平。在該應用筆記中,圍繞通帶任一方向的頻率掃描顯示,在相同等級的衰減下,可以支持更大的信號。在該應用筆記中可以看到,在靠近頻帶邊緣的位置,6 dB衰減可以對應10 dB。之后,集成式濾波器對帶外信號進行大幅衰減,這些信號不會在帶內混疊,主要被片內濾波和外部濾波衰減。

這些模塊將-15 dBm帶外干擾濾波到約-40 dBm至-45 dBm,直到20 MHz排斥帶。繼續(xù)向前,可能受到更高的抑制。在這個階段,圖5顯示出現的衰減可能非常小。

前端模塊的線性度可能是更大的問題。此時,可能得出很大的IM3產物。根據實際選擇的FEM,可能需要將頻帶選擇濾波器移動到第二個LNA之前,以保護其不受帶外信號影響,這通常會產生較大的IM產物。無法在這類FEM的級之間放置濾波器,所以需要采用備用選項。

為了幫助限制大型帶外阻斷器的互調的影響,典型的FEM包含二級旁路開關,用于降低增益和保護二級不會被驅動產生非線性,如圖3所示。切換LNA增益使信號鏈SNR降低1 dB,但限制這些大型阻斷器引起的交調失真有助于保護整體動態(tài)范圍,抵消噪聲性能的損失。總體而言,如此產生的最差NF為約5.7 dB,這仍然在參考靈敏度的局域(小型蜂窩)覆蓋范圍要求之內。剩余的濾波器要求由天線濾波器提供,抑制可以根據接收器FEM的低增益壓縮點和IP3決定。

變送器信號鏈示例

將ADRV9029和合適的RF驅動放大器,或RFVGA組合使用時(訪問analog.com/rf了解更多選項),可以輕松構建合適的PA、緊湊的室內微微蜂窩、室外微微蜂窩或室外微蜂窩5。這些5G技術器件與幾個無源元件組合,就可以構成非常緊湊且高效的變送器設計,如圖6中的信號鏈所示。此架構的關鍵優(yōu)勢在于可能達到的高水平集成,通過使用所選的ADI收發(fā)器具備的集成式DPD功能,不但可以實現極低的實施成本,還能使功耗降至最低。

如圖6所示,小型蜂窩變送器系列由環(huán)形器、PA、濾波器和收發(fā)器組成。此外,電路的PA輸出端中包含一個耦合器,用于監(jiān)測輸出失真(也可以用于監(jiān)測天線的VSWR和正向功率),可以配合DPD使用,以改善發(fā)送功能的運行效率,以及改善雜散性能。雖然可以使用外部DPD,但選擇的ADI收發(fā)器包含完全集成的DPD,該DPD采用350 mW或更低的增量功率,具體由給定的PA所需的校正量決定。低功率PA需要進行的校正較少,所以DPD消耗的功率更低。此外,由于DPD的帶寬擴展完全在收發(fā)器內部進行,觀察接收器SERDES路徑被完全取消,變送器有效載荷降低,使得集成式DPD將SERDES路徑的數量降低至外部基帶芯片的一半。FPGA中的等效DPD通常具有10倍以上的功率,對于低功耗小型蜂窩和大規(guī)模MIMO來說是無效或低效的。但是,通過將DPD集成到收發(fā)器中,非常低的功耗和低成本使得DPD能被用于低功耗小型蜂窩中,可以在不增加外部計算負擔的情況下提高效率和變送線性度。

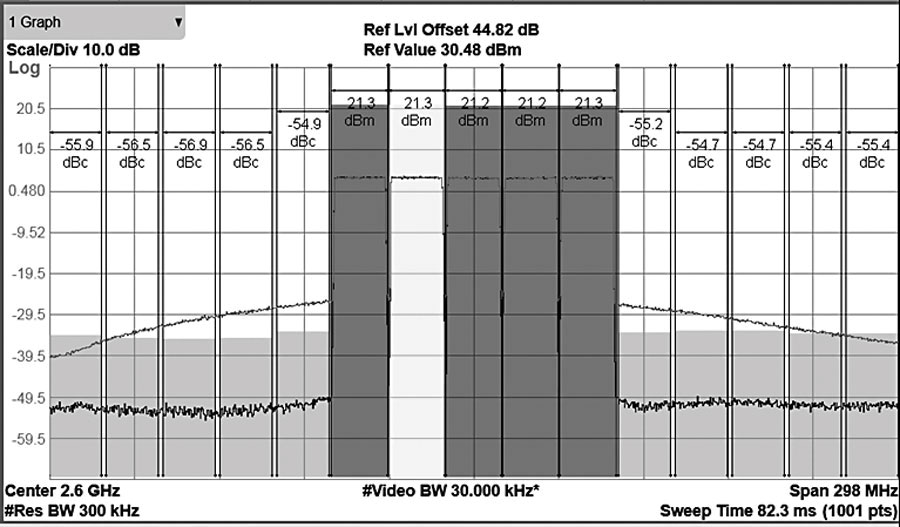

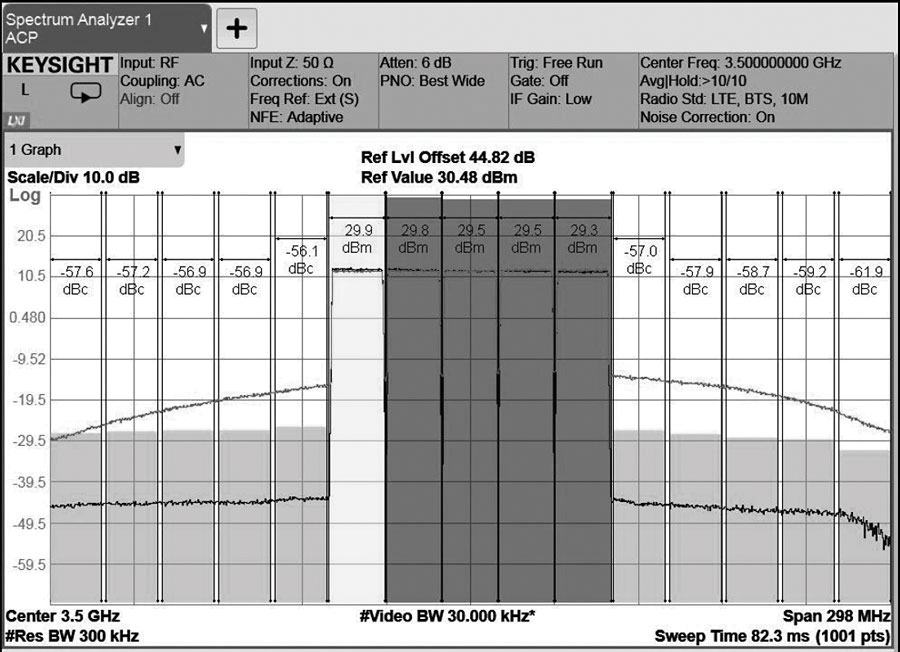

圖7和圖8顯示ADI的DPD用于低功耗和中功耗小型蜂窩應用的示例。圖示的激勵源是針對5個相鄰的20 MHz LTE載波,總共100 MHz。一般來說,LTE要求最低達到45 dB ACLR,大多數部署都可以超過此值。ADI運行一個連續(xù)測試實驗室,始終會檢查所有功率等級的新PA。查看功率放大器測試報告,或咨詢工廠,獲取ADI提供的可用的DPD技術的最新信息,以及最近通過測試的PA的列表。

圖6. 變送器信號鏈詳情

圖7. 帶和不帶DPD的典型PA頻譜,RF總和為26 dBm

圖8. 帶和不帶DPD的典型PA頻譜,RF總和為37 dBm

它們如何組合使用?

圖9顯示完整的信號鏈,其中包括一些所需的控制信號。為了提高功效,該電路包含變送和接收信號功能,以在各自的周期內為TDD啟用和禁用放大器。同樣,它可與FDD配合使用,在插槽未使用時關斷電源,以節(jié)省功率。還需要使用LNA開關來更改LNA上的輸入開關,以將返回的變送功率分流至端電極,而不是分流至內核放大器輸入。這些不同的信號可以由ASIC、FPGA或收發(fā)器生成和編配。

接收器信號鏈包括一個可以相應改變數字數據流的函數,以說明模擬增益降低的原因,在信號發(fā)送至低PHY,然后發(fā)送至基帶下游其他部分時保持絕對信號電平。

此處所示的應用適用于單頻段。雖然收發(fā)器使用寬帶且覆蓋至高達6 GHz的所有頻率,但并非設計中的所有器件都是如此。LNA和PA這類器件通常使用頻段,需要根據支持的頻段進行選擇。通常情況下,這些器件在引腳兼容選項中提供,覆蓋6 GHz以下的所有常用頻段,且易于掃描。如此,可以支持所有的常用TDD和FDD頻段,包括用于5G和提議用于O-RAN的頻段。

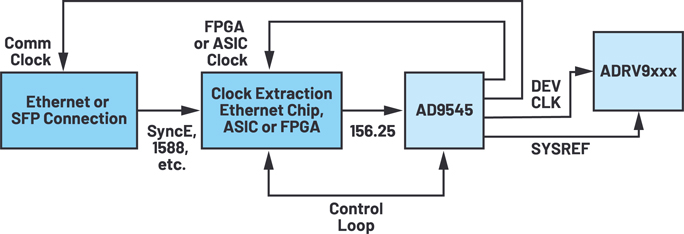

時鐘樹

根據配置,可以使用幾種不同的時鐘配置。如果需要精確的時間校準,則需要使用2級時鐘合成。第一級是通過ASIC、FPGA或控制器連接至基帶,以準確計時和校準無線電數字化功能。此應用要求通過前傳網路或本地GPS接收器來處理提供的精確時間協(xié)議(PTP)信息。如此確保無線電和基帶處理器知道應對無線電幀實施處理的準確時間。

AD9545系列非常適合用于準確調節(jié)無線電的主時鐘的頻率、相位和時間。其優(yōu)點在于,可以配置為在無參考時鐘的情況下臨時運行,且在與TCXO(溫度補償晶體振蕩器)或OCXO(恒溫晶體振蕩器)耦合之后,且在參考時鐘出現故障或斷續(xù)的情況下保持精度。

對于無需準確的時間校準的配置,或者作為校準的第二級,需要使用時鐘分配器件。分配器件的作用在于,為整個無線電生成時鐘范圍。這包括JESD、eCPRI、以太網、SFP所需的范圍,以及整個無線電的其他關鍵信號所需的范圍。AD9528提供14種不同速率的低抖動時鐘,包括支持JESD204B/JESD204C器件時鐘和SYSREF信號功能。

2級時鐘框圖如圖10所示。對于無需準確校準時間的應用,可以去掉或旁路AD9545,僅使用AD9528。系統(tǒng)的輸入時鐘來自于基本的網絡定時,由以太網功能塊或FPGA中的基帶和網絡功能恢復,具體由實際架構決定。可以根據無線電的具體要求選擇多種備用配置,此處只顯示一種表示方法。

圖9. 完整的收發(fā)器信號鏈

圖10. 時鐘樹示例

功率

功耗是由多種因素決定的。這些因素包括選擇的FPGA、采用的功能、選擇的收發(fā)器、啟用的選項、所需的時鐘樹,以及生成的RF功率。

實施O-RAN CUS和M面處理的典型中等范圍FPGA SoC,加上與IEEE 1588 v2 PTP堆棧同步,會消耗約15 W。典型的ADRV9029收發(fā)器會消耗5 W至8 W,由TDD或FDD配置,以及啟用的DFE功能的范圍決定。為此,必須增加時鐘功率、接收器功率、變送器功率,以及其他功率。表2顯示系統(tǒng)(不包括變送器鏈)的功耗總和示例,功率輸出等級不同時,該值存在很大差異。

將無線電的功耗相加,Tx:Rx在70:30占空比下的總功耗為26 W至29 W,具體由實際采用的無線電配置決定(不包括與PA相關的功耗)。表3顯示少數幾個PA功耗示例。由于PA主要在AB類晶體管的線性范圍內工作,所以它們的效率在20%到50%之間。在這個范圍內,集成式DPD大有優(yōu)勢。即使對于小帶寬、低功耗PA,幾十mW的DPD功耗也會抵消PA效率的改進。

表2. 預算功耗

|

器件 |

需要數量 |

TDD 70:30典型功耗(4T4R) |

|

中等范圍FPGA SoC |

1 |

~15 W |

|

ADRV9xxx |

1 |

~5 W |

|

ADRF5545A |

2 |

0.6 W |

|

AD9545 |

1 |

0.7 W |

|

AD9528 |

1 |

1.4 W |

|

Pa驅動放大器 |

4 |

1.2 W |

|

其他 |

1 |

2 W |

|

總計 |

14 |

26 W至29 W |

表3. 變送功耗

|

器件 |

需要數量 |

TDD 70:30典型功耗(4T4R) |

|

PA(+24 dBm/天線) |

4 |

~2.5 W |

|

PA(+37 dBm/天線) |

4 |

~47 W |

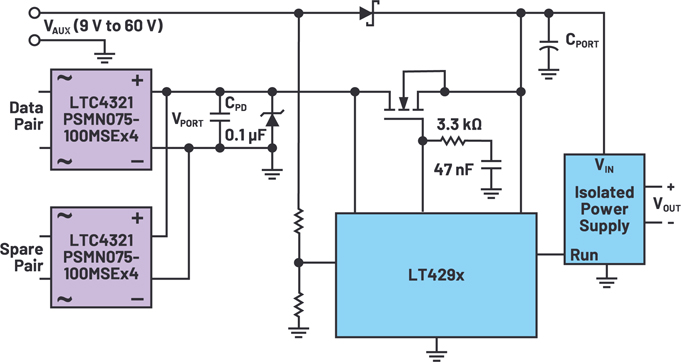

對于低功耗小型蜂窩,增加約2.5 W額外功率會讓總功耗增加至約30 W,對于由PoE解決方案供電的無源冷卻室內小型蜂窩非常合適。

一種潛在的PoE解決方案如圖11所示。該解決方案包括LT4321橋控制器,它使得MOS晶體管可以用作理想的二極管,而不是整流器,其優(yōu)點在于可以大幅提高效率。其后接LT4295,這是一個符合802.3bt標準的PD器件。還可以后接合適的本地穩(wěn)壓器,以滿足之前的表中所示的要求,按照需要提供高達90+ W的功率。

圖11. PoE隔離式小型蜂窩電源解決方案

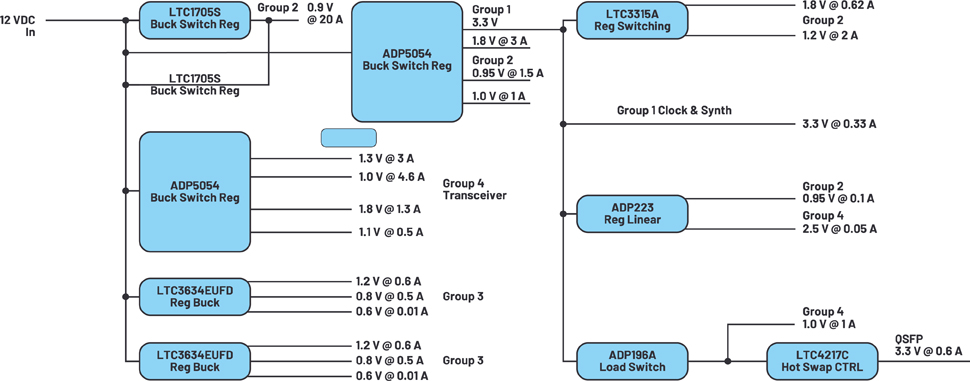

除了PoE轉換器件外,還可以使用許多其他器件來支持小型蜂窩參考設計。其中包括基礎器件,例如ADP5054系列,該系列專用于為ADI收發(fā)器、許多其他降壓轉換器和低噪聲LDO穩(wěn)壓器供電,如圖12所示。

選項

這個無線電架構的一大優(yōu)點是:它非常靈活,可以滿足多種市場需求。此架構針對多種應用進行優(yōu)化,包括FDD和TDD。它可以在低、中和高頻段內保持高性能,非常適合小型蜂窩到大規(guī)模MIMO平臺。可以在變送器和接收器電路中進行不同的權衡取舍,以優(yōu)化成本、尺寸、重量和功率。雖然本部分側重于更高的性能和集成,但可以通過選擇稍微不同的選項,做出可以改善成本的取舍。

例如,一些低功耗PA不需要使用驅動放大器,可以不要求配備。對于許多小型蜂窩應用來說,RF功率都較低,所以可以使用簡單的TR開關來替代環(huán)形器。最后,如果只需要局域性能,可以使用簡單的單級LNA來替換雙級LNA。結果是,成本更低的選項仍然能夠提供不錯的無線電性能。實例如圖13所示。還可以使用許多其他排列,在廣泛的頻率和功率選項內,滿足多種可能。

圖12. 適用于小型蜂窩應用的典型功率樹

圖13. 備用的收發(fā)器信號鏈

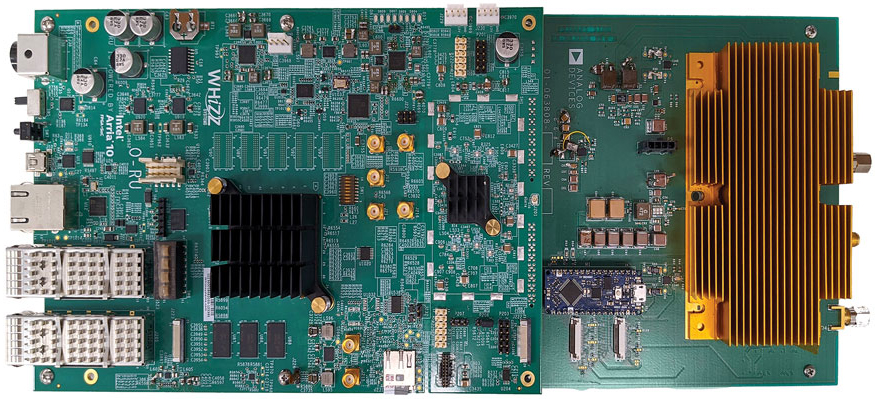

圖14. 5G原型平臺,包括可重新選擇頻段的RF前端

結論

本文所述的5G技術器件適用于通信應用,支持實現適合5G開發(fā)的低成本器件,尤其是實現O-RAN O-RU解決方案的器件。其中包括來自RadioVerse系列的器件、RF放大器、時鐘恢復/同步,以及以太網供電/負載點調節(jié)。這些高度集成的器件組合可用于實現5G小型蜂窩、宏蜂窩、微蜂窩和大規(guī)模MIMO應用。

與FPGA、eASIC或ASIC中提供的合適的PHY和軟件組合使用時,可以開發(fā)完整的O-RU解決方案,如圖14所示。此解決方案是與Intel®、Comcores和Whizz Systems等合作伙伴共同開發(fā)的。這些解決方案不僅滿足所需的RF特性,而且滿足部署低成本、高性能O-RAN平臺所需的成本和功率預算。

來源

1 ftp://ftp.3gpp.org/specs/latest/Rel-15/38_series/

2 O-RAN聯(lián)盟。

3 “O-RAN: 朝向開放和智能的RAN發(fā)展。”O-RAN聯(lián)盟,2018年10月。

4 Brad Brannon。 “零中頻的優(yōu)勢:PCB尺寸減小50%,成本降低三分之一。”《模擬對話》,第50卷第3期,2016年9月。

5 規(guī)格。 O-RAN聯(lián)盟。

作者簡介

Brad Brannon自北卡羅來納州立大學畢業(yè)至今,已在ADI公司工作37年。在ADI公司,他先后在設計、測試,應用和系統(tǒng)工程等領域擔任多個職位。目前,Brad負責開發(fā)O-RAN參考設計,為這些客戶提供支持。Brad撰寫過多篇論文和應用筆記,主題涉及數據轉換器計時、無線電設計、ADC測試等。

粵公網安備 44030902003195號

粵公網安備 44030902003195號