《射頻微波芯片設計》專欄適用于具備一定微波基礎知識的高校學生、在職射頻工程師、高校研究所研究人員,通過本系列文章掌握射頻到毫米波的芯片設計流程,設計方法,設計要點以及最新的射頻/毫米波前端芯片工程實現技術。

本文共計五部分

(全文閱讀大概需10分鐘,內容多有不嚴謹甚至是調侃的成分,大家看看圖個樂,加深下印象。如果你在閱讀本文某些地方,有那種言而不明的朦朧感的時候,那一定是博主自己也沒整明白,開始在劃水,所以更多專業的知識還是希望大家下來看看書復習下,當然最后還是希望本期內容對您開卷有益)

1.前 言——為啥要了解MOS管

2.MOS管的基礎概念

3.MOS管的I/V特性

4.MOS管的二級效應

5.MOS管的抽象電路模型

前言

都說酒是穿腸藥,色是刮骨刀,那么在現代電子系統中,咱門的MOS管大哥,便是傳統真空管電子以及分離式固態射頻電路的意大利炮,正逐步用他那無與倫比的性能、超低的功耗、極小的尺寸把傳統工藝電路轟進了歷史博物館,當然也在不斷地提高著大家對集成電路的認知。

在前面幾期我們聊到了常見的射頻基礎概念,也基于幾個實際例子給大家演示了射頻電路的設計方法,學習了如何設計濾波器、耦合器、天線、低噪聲放大器等等,如下所示(大家有時間的話,可以鏈接過去復習下,或許學習的過程是痛苦的,但希望這幾篇博文可以是苦寒中的梅花清香,讓大家有所獲):

3.《耦合器芯片》

4.《詳解圓極化天線…》

……

為了后續設計稍微復雜的射頻有源電路,本期主要介紹下MOS管的基礎。我們知道在射頻微波電路中Cascode和吉爾伯特單元是最為常見的電路結構(LNA、PA、Mixer、VGA、PS等電路中常常有使用到),那么在開聊這些稍微復雜的電路結構之前,咋門先看看下面的一個簡化的電路,大家可先停下來,思考下:

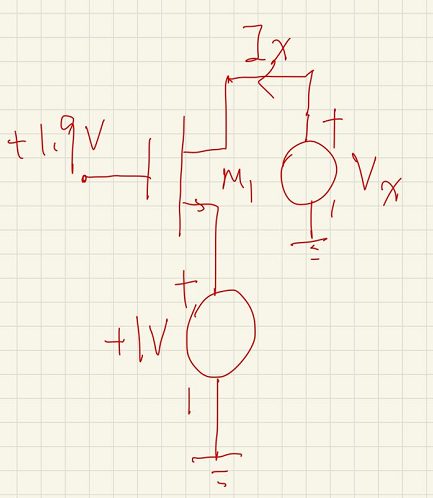

問題導入:如下圖所示,假定Vth0=0.7V,忽略溝道調制效應和體效應(即lambda=0,gama=0),分析下圖中電路,當Vx從0V變化到3V時,Ix是怎么樣的一個響應曲線,同時M1管子是怎么樣工作的???

(小提示:大家伙可以分三種情況((0,1);(1,1.2);(1.2,3))去討論結果,如果有疑問可以加微波射頻網的小編好友然后入群討論,文末有小編的微信二維碼)

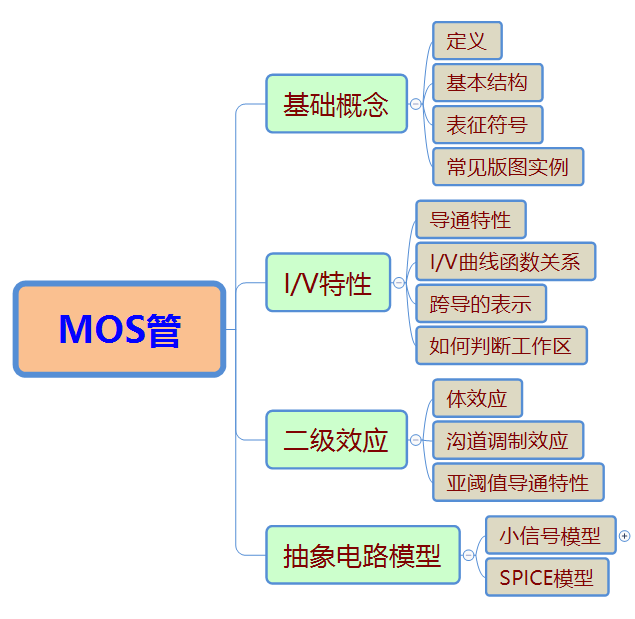

好了,言歸正傳,本篇博文的主要目的是:希望通過總結概括MOS管的基礎知識,1:給在校學生一個學習提綱;2:給正在求職面試的同學一個方便查閱的途徑;3:也希望本期內容可以給從業人員一個溫故而知新的小文庫。因此,下面將按照如下內容進行展開:

基本概念

1)定義

MOS管,是MOSFET的簡寫(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET),MOSFET即為金屬-氧化物半導體場效應晶體管,當然我們平時還是叫MOS管比較自然一點,當然我們在實際工程中為了把NMOS和PMOS做在一起,用的比較多的還是CMOS(互補型金屬氧化物半導體)。

看完上面的一段話,大家伙兒是不是還是一臉蒙圈,拋磚老哥你在說什么???你寫的漢字我都認識,但為何我的大腦,任然不知道你在講啥啊!!!

小老弟/小姐妹兒,咱不急,我們接著往下看——

2)結構

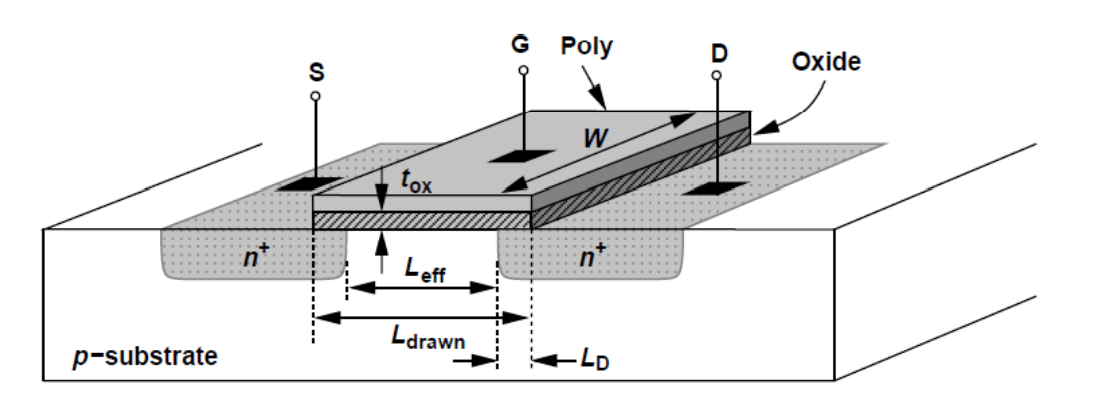

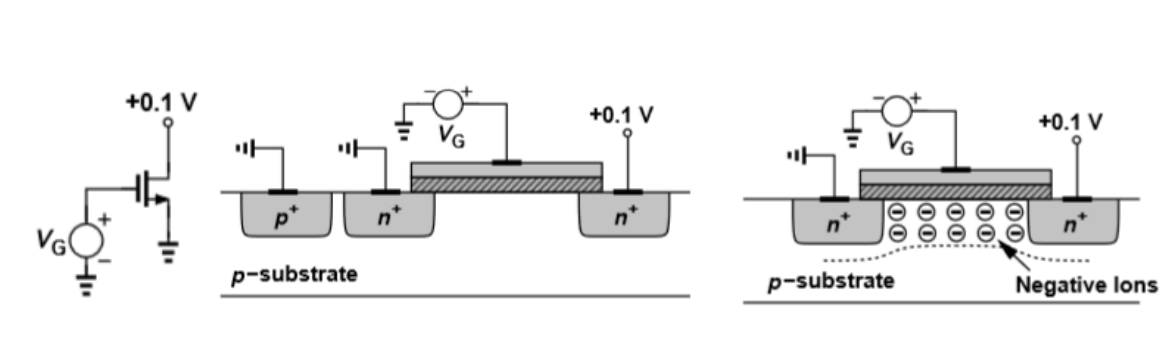

MOS管分為NMOS和PMOS,我們先拋開各種復雜的工藝流程不說,先看看NMOS它的廬山真面目,如下所示:

首先搞明白我們為什么要做MOS,其實簡單地說就是我們需要有一個器件可以以小博大,四兩撥千斤,通過較小的電壓去實現對大的電壓擺幅的輸出(也就是放大作用,當然也可以是控制有無輸出,即也可以做開關)。

好了,既然MOS管是用來做控制(以小博大)器件的,那么必然有這樣一個三角關系:A和B作為發起方和受用方,而C呢就作為調控方,就好像上面的一根小小的管子,把兩杯水給安得明明白白。

在實際的工藝中,咱們就見到了如上圖提到的NMOS結構,其中D和S就是發起方和受用方,我們通常把D叫做漏極,把S叫做源極(當然只是這么叫,在某些特定的電壓下,他哥倆的身份是可以互換的),然后G我們把它叫做柵極(就是中間人,你也可以把它叫做以小博大的皮條客),皮條客G柵極為了避免有一天東窗事發,干活的時候會用一層薄薄的絕緣氧化物薄膜把自己和D、S隔離開來,也就是上面的氧化物有一層tox的厚度。那么D和S的距離,也就是等效柵長,我們叫做MOS管的等效溝道長度Leff,(話說,臺積電準備在2025年把控制D和S的距離在量產到2nm,而韓國三星更為恐怖,他準備在2027年把D和S的距離量產到1.4nm了,什么,國內呢?這個嘛,不清楚,大家伙可以留言討論)

對了,MOS管的中文全稱叫啥來著?哦,金屬-氧化物半導體場效應晶體管,那么這里我們就把金屬D、S、G以及氧化物薄膜為基礎的場效應管結構介紹完了,然后所謂半導體嘛,自然就是說咱們的這些個柵極G、漏極D、源極S以及氧化物薄膜的辦公室,當然他們的辦公室不是隨隨便便選個場地就玩完,他們是選中了以低摻雜濃度的P襯底為場地,為了不壞事,場地和所謂的G、D、S盡量不要發生辦公室戀情,至少不要影響到G、D、S干活,因此在NMOS中的P襯底所謂的低摻雜就是說正常情況下基本不導電,只是提供場地的作用(當然,都說日久生情,我們的襯底有時候也會對MOS管產生一些情愫和影響,我們在后面的MOS管的二級效應中,會繼續來聊聊這段孽緣)。

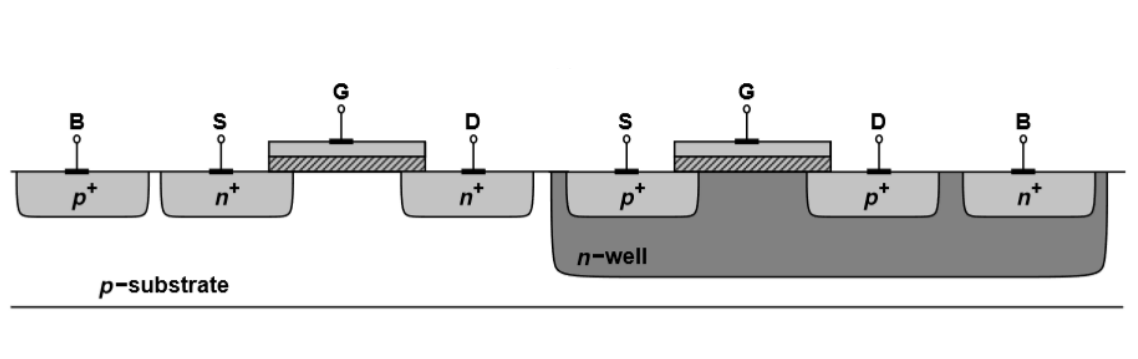

好了,上面我們大概了解了MOS管的作用的基本構成,在實際使用中,一般我們會用互補型的金氧半場效晶體管工藝,也就是大名鼎鼎的CMOS工藝,其結構如下圖所示:

大家肯定會說,城市套路深,我要回農村,咱家又不是沒地,干嘛委屈自己擠在一起干活?

我想說的是,小伙子光家里有地還不行啊,畢竟現在是公元2022年,現代社會講求的是高效與合作共贏嘛!那么當我們把NMOS和PMOS放在一起的時候,往往可以達到事半功倍的效果,不過話又說回來,他倆經營的事業還是有點不一樣的,NMOS和PMOS形成溝道的先決條件都是需要勢壘電壓的變化,因此天然而言,其存底摻雜的類型就有點區別,就好像雖然在商場里面大家都是做生意的,但是還是需要做一些隔間來區分各自的功能性,那么在CMOS工藝中,就是在P襯底上面做一個N-Well,然后PMOS就可以做到這個N-WELL里面了,這樣PMOS和NMOS就可以愉快地在一起玩耍了。

3)表示符號

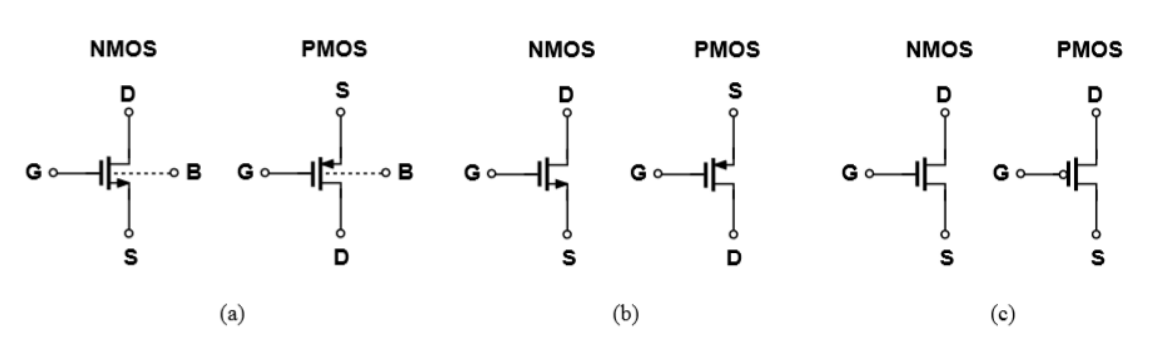

為了在交流過程中更加順暢,我們的物理學家和工程師們就對NMOS和PMOS的表示符號進行了一些定義,這個就好像我們中國的傳統象形文字一樣,見下圖所示:

在(a)、(b)、(c)中均是NMOS和PMOS的象形符號,大家可以按照自己的喜好去用,一般來說我們會把襯底的端電壓(B,Bulk)接到地或者VDD上面,因此用(b)、(c)的時候要多一些,其中(c)的符號表達式在數字電路中用的比較多(表示開關)。

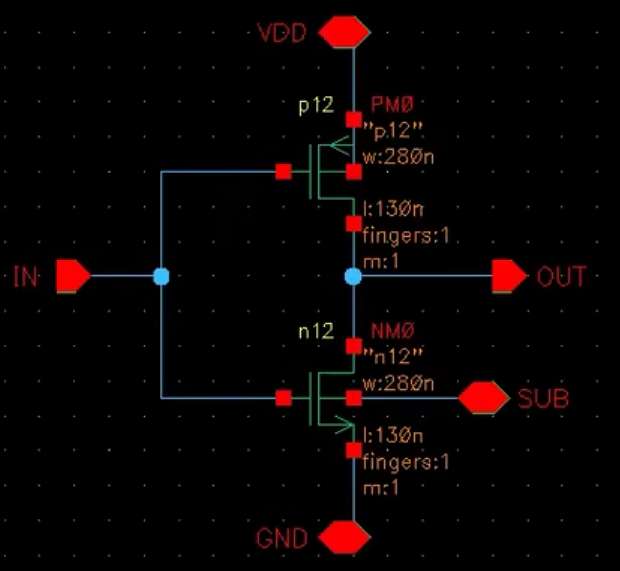

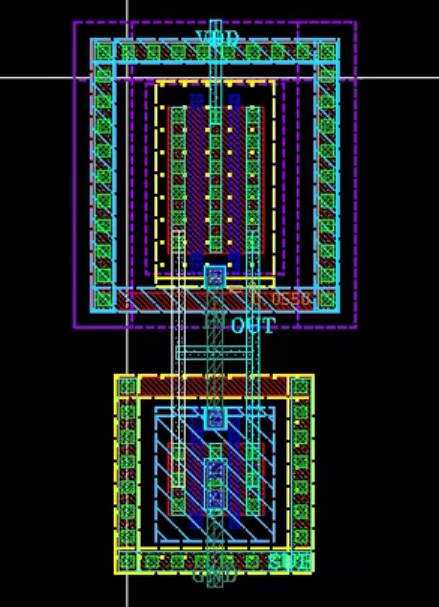

4)常見版圖實例

相信大家在面試的時候,很多面試官為了考查大家對NMOS和PMOS管子的結構是否理解的清楚,經常會叫大家繪制出最為典型的反相器的截面圖,因此大家對上面給出的NMOS與PMOS的截面圖還是要多多理解下。這里給出一個經典的反相器的原理圖和版圖(并非截面圖),供大家參考。

好了,聊完基本的MOS管概念,下面我們進入一點數學的環節(不要被嚇著,其實這些數學公式也就是物理現象的一種表示方式,就和我們上面提到的象形文符號一樣的,他使我們的表達更加精煉,因此在這篇博文中我們不做數學推導,只做大自然的搬運工),那么下面就來討論下,到底這個MOS管咋個工作的!!!

MOS管的I/V特性

如前面所說,我們研究I/V特性不是為了推導而推導,只是為了讓我們更加清楚地了解MOS管的工作狀態,在后續的表達中可以更加簡潔精煉,因此我們本部分重點討論MOS管的工作狀態(主要討論NMOS管,PMOS其實很多時候就是多一個負號,大家可以自行分析下),以及如何判斷工作狀態,附帶地根據數學公式繪制出各個狀態下的I/V特性。

1)導通特性

如上圖所示,當我們不斷升高VG,會有什么事情發生呢???我們可以看到柵極和襯底之間會等效成一個電容板,那么VG電壓升高,堆積在柵極金屬板的電荷就開始變多了,當電荷多到形成了一個溝道,這個時候D和S就會被導通,此時我們的VG就是所謂的“閾值電壓”,VTH電壓。我們接著繼續提高VG,此時溝道里面的電荷密度繼續增加,導致漏源電流進一步增加。好了,那么我們剛剛提到的VTH是一個定性分析出來的量,下面我直接給出半導體物理里面VTH的計算公式:

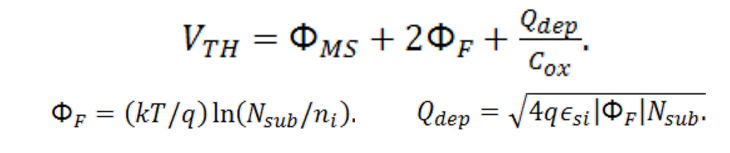

其中 是多晶硅柵和襯底的功函數之差的電壓值,

是多晶硅柵和襯底的功函數之差的電壓值, 里面的Nsub是襯底的摻雜濃度,q是電子電荷,ni是硅的本征載流子濃度,Qdep是耗盡區的電荷,Cox是單位面積的柵氧化層電容。

里面的Nsub是襯底的摻雜濃度,q是電子電荷,ni是硅的本征載流子濃度,Qdep是耗盡區的電荷,Cox是單位面積的柵氧化層電容。

當然我們實際計算不可能用上面的數學公式,因為這些個參數,我等凡人怕是不好測試到哦,當然就算是燒爐子的老師傅怕也是不好得到上面的參數進而求解到VTH,那么我們怎么來得到VTH 呢?下面且聽我把IV特性函數細細道來,當然現在的工藝大廠們一般SPICE參數里面會有一個VTH0,我們可以直接用。

2)I/V曲線函數關系

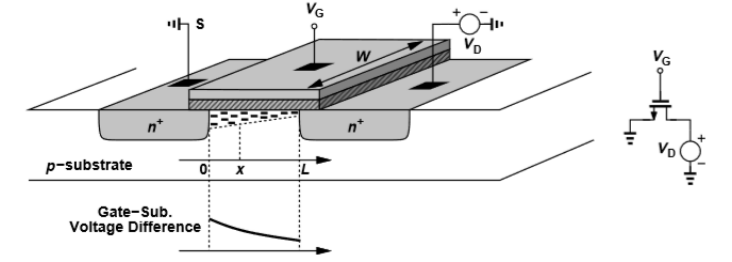

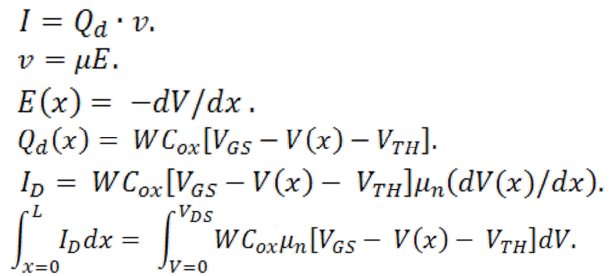

首先我們還是假設在NMOS管的柵極加上VG,源極S接地,漏極加一個VD電壓,然后根據下面的公式(看不太明白沒關系,可以到群里或者加作者好友留言討論):

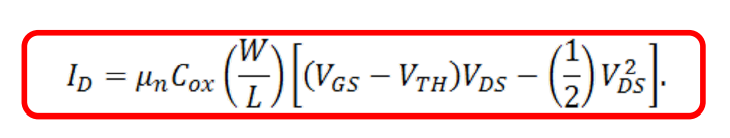

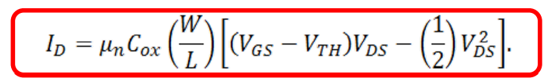

好了,不管推導過程的話,我們直接可以得到NMOS的漏極電流ID的數學函數表達:

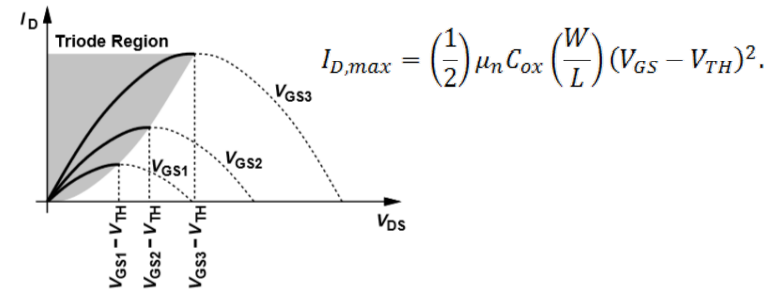

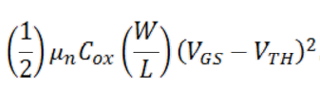

也就是說,此時我們的電流與載流子遷移率、單位長度電容、VGS、VTH以及VDS的值相關(拋物線方程),我們對ID求一個關于VD的偏導并令其為0,此時就可以看到想要ID獲得最大值,ID為:

Bingo,相信學過模擬電路的大家,此時對ID,max的值有一點點印象了吧,哈哈,他就是咋門NMOS管飽和時的電流啦,也就是說,當VD=VGS-VTH時,咱們的NMOS管的電流將會趨于穩定,也就是達到飽和狀態(這個我們待會后面再來討論)。

這里我們需要對上面公式中的兩個參數,單獨拉出來說一說:

1是我們的VGS-VTH,這就是大名鼎鼎的“過驅動電壓”,怎么說呢,為了形象地理解的話,我們VG剛剛達到VTH時就可以開啟,但是我們繼續加電壓(也就是VG-VTH還有余糧了),這個時候,是不是就驅動的飛起了,所以我們這么理解過驅動電壓沒毛病吧(哈哈,先這么理解吧,其實這個說法還是有點點值得考究的)。

2是我們的W/L,這就是我們在日常工作中提到的“寬長比”,在上面的公式中通過調節寬長比可以改變整個MOS管的最大輸出電流,在后續的博文中我們還會討論到寬長比對跨導,噪聲,線性度等等的影響。

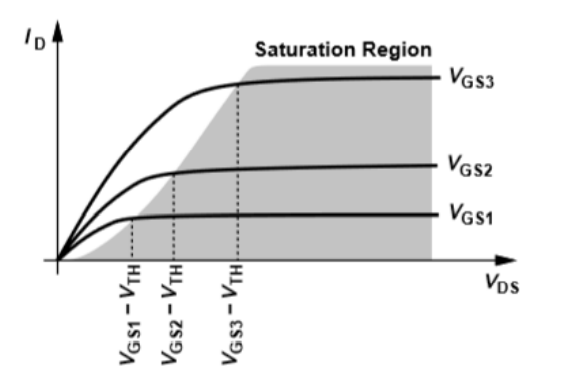

好了,到目前為止我們大概討論三種電流電壓狀態【哈哈,此時的你心里是不是在想:什么,什么?哪來的三種?拋磚老哥你沒騙我吧,我明明才看到1種啊,就是你說的VDS=VGS-VTH,我天,難道我眼花了?】好吧,我們把時間調回本節開始的地方:

1.當VG小于VTH時,此時我們的管子截止,也就是我么所謂的截止區,電流為0;

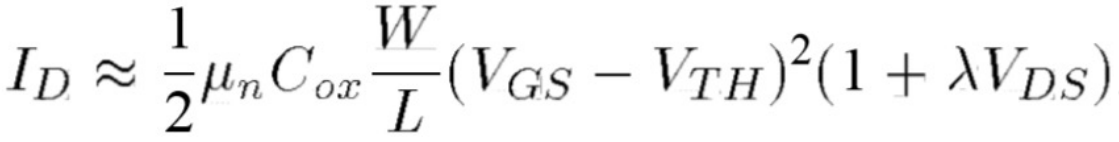

2.當VG大于VTH,且VDS≥VGS-VTH,此時管子處于飽和區,電流為:

3.當VG大于VTH,且VDS<VGS-VTH,此時為三極管區(也有叫線性區的),此時電流為

好了,就這些,大家伙自個體會吧(可能看到這里還是有點繞,沒關系后面我們還有一個比較容易判定工作在哪個區的方法)

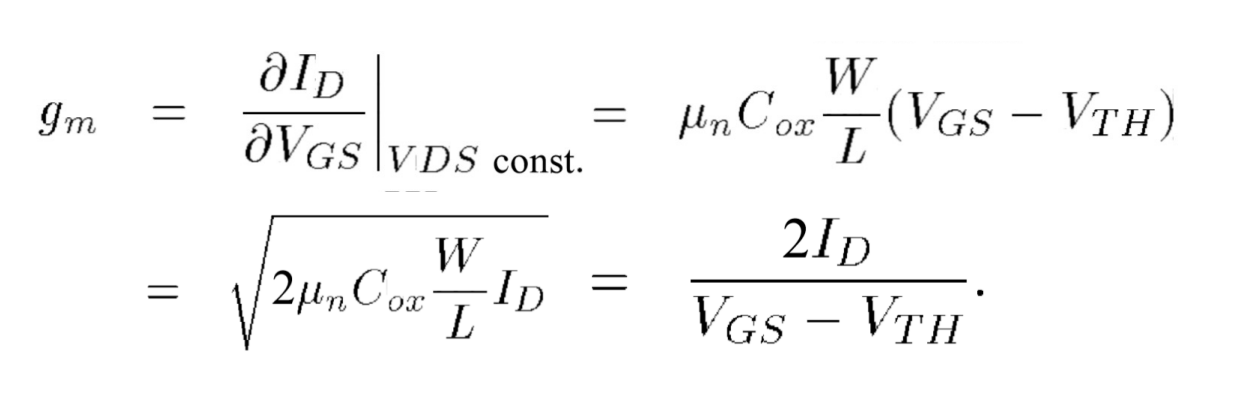

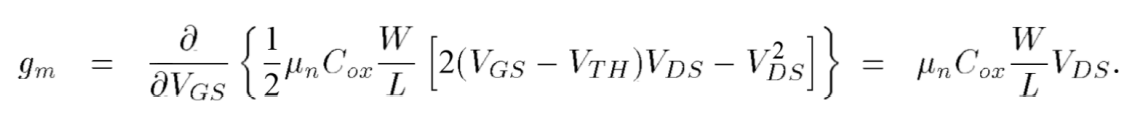

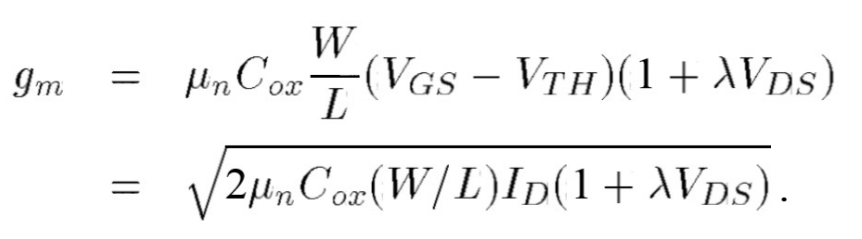

3)跨導的表達

這部分內容,就偷個懶,不在贅述其基本由來,直接根據上面的電流公式進行一個關于輸入電壓的求偏微分,即當管子處于飽和區時:

當管子處于三極管區(線性區)時:

通過跨導的大小我們就可以知道該管子四兩撥千斤的能力,也就是說,VGS稍微變動一下咱門的ID就可以有較大的變化,gm就是衡量這個四兩撥千斤能力的值。

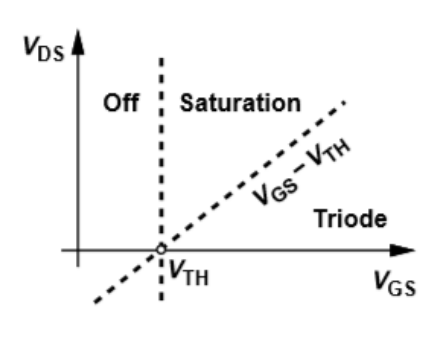

4)如何快速判斷NMOS管的工作狀態

這里承接上面判斷NMOS管的工作區部分,通過上圖我們可以知道:

1.我們看橫坐標,當VGS小于VTH時,即豎虛線左邊,管子截止,處于截止區;

2.看橫軸VGS大于VTH時,斜虛線為VD=VGS-VTH,斜虛線上方為VDS大于VGS-VTH,管子處于saturation,即飽和區;

3.繼續看橫軸VGS大于VTH時,斜虛線為VD=VGS-VTH,斜虛線下方為VDS小于VGS-VTH,管子處于Triode,即三極管區或者叫線性區;

好了,現在各個工作區的區分條件大家應該比較清楚了,那么在來補充一個概念,就是當我們的MOS用于開關的時候,開啟時是處于什么狀態呢?此時開啟電阻又是多少?好了這個問題大家就自行下來找答案或者到群里討論吧。

MOS管的二級效應

說到MOS管的二級效應,其實呢,主要就是我們在之前聊到的那段襯底與源極之間的孽緣、溝道長度效應和亞閾值導通特性。

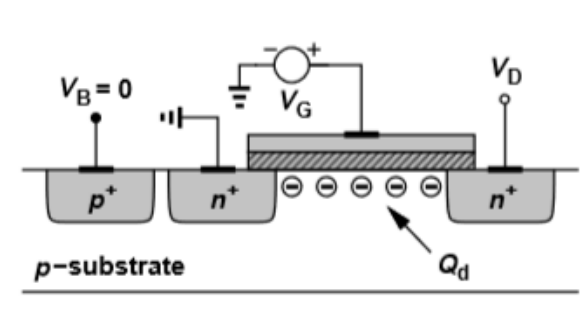

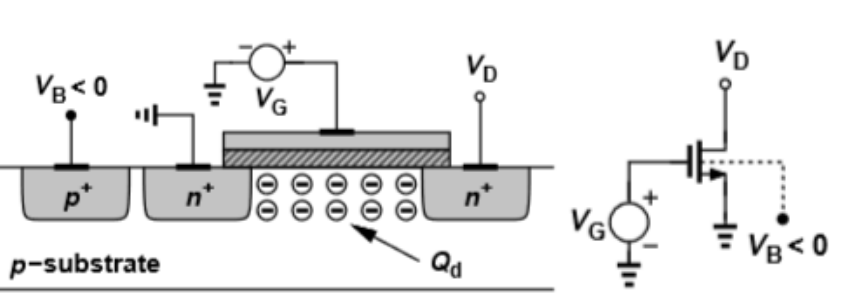

1)體效應

說到體效應,在之前我們都是默認襯底端接電到了GND,也就是說我們默認把VSB的值認為是一個固定值,那么VTH就可以根據之前的公式去求得,BUT,我們知道當VB變得更負(或者說VSB的相對值變得更負),那么將有更多的空穴被吸引到襯底電極,進而留下來了大量的電荷,使得耗盡層變得更寬

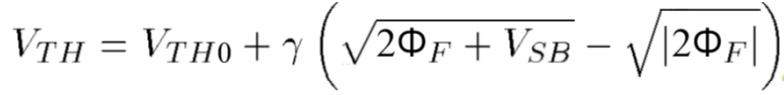

因此,此時受體效應影響的閾值電壓VTH的新的計算公式有如下表示:

VTH0就是之前的那個閾值電壓,一般我們工藝廠家會在SPICE文件中給出這個值,而VSB就是MOS管源極與襯底接觸的電壓差。

為體效應系數,同樣的,一般我們工藝廠家會在SPICE文件中給出這個值,在我們計算的時候直接帶進去就可以的。

為體效應系數,同樣的,一般我們工藝廠家會在SPICE文件中給出這個值,在我們計算的時候直接帶進去就可以的。

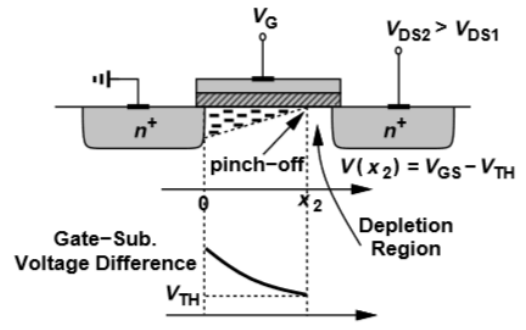

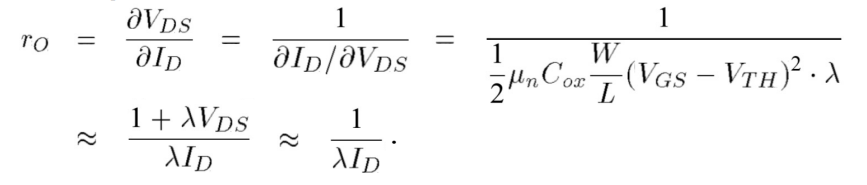

2)溝道調制效應

這個效應發生在飽和區,如下圖所示,反型層局部電荷密度正比與VGS-VTH-V(x),因此當V(x)接近于VGS-VTH時,電荷密度下降為0,即反型層這個時候終止,我們提高漏極電壓與源極電壓壓差,會讓反型層比2002年的第一場雪還要來的早一些,換句話說,隨著柵和漏之間的電壓差增大時,實際的反型溝道長度逐漸減小(哈哈,這里也就間接地說明了溝道調制效應他并不是在截止區和三極管區)

Lambda是溝通調制調制系數,當然在實際工程中,MOS管的SPICE參數里面會給出這個值。同樣的道理,我們可以根據新的ID求出在溝道調制效應下面的跨導:

3)亞閾值導通特性

這個特性呢,有點點反三觀,因為我們之前一直在聊,當VGS小于VTH(即柵源電壓小于閾值電壓)時,管子就關斷了,但是現實是咱們的MOS管大兄弟的求生欲十分強,當VGS約等于VTH或者略小于VTH時,還存在一個弱弱的反型層,并且有一些小小的漏源電流,那么可能大家伙又會問了,MOS管的這個小任性又會帶來什么幺蛾子呢?

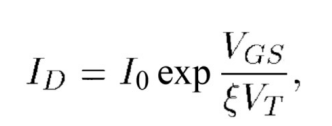

以前上初高中的時候,背寫英文小作文,最為經典莫過于“Every coin has two sides”,那么MOS管的亞閾值導通特性也是一樣的,一方面由于當VGS小于VTH管子關而不斷,會導致管子中存在的小小的電流,這個電流一旦積少成多就是一個相當恐怖的存在,比如上百萬甚至上億個管子工作的時候,這個小電流就會是一個可怕的功耗;那么另外一方面,當我們的MOS管處于亞閾值區時,電流與VGS呈指數關系,此時就可以獲得較大的增益:

我們平時工作狀態在三極管區或者飽和區的正常MOS管,如何過渡到亞閾值區呢?答案就是,當保持ID不變,增大柵寬W,使得VGS逐漸靠近甚至略小于VTH,或者我們減小電流ID,那么帶來的一個結果就是亞閾值電路的速度是很受限制的。

MOS管的抽象電路模型

1)MOS管的小信號模型

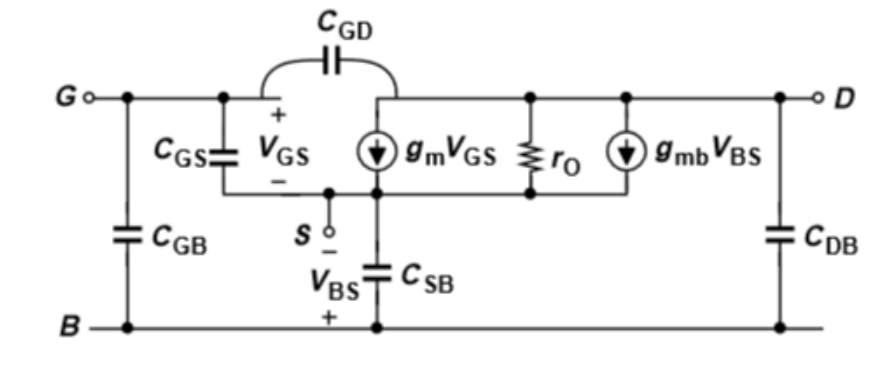

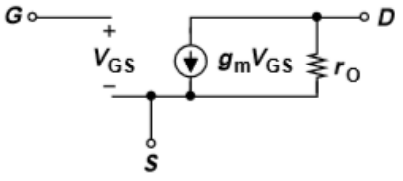

在分析MOS管小信號模型之前,我們先要搞明白為啥要花這么多時間去做這件事。首先呢,前面也提到了,我們用MOS管主要是用來做開關或者四兩撥千斤的控制放大效果,然后有了這個前提,那么我們是不是就得順著這個目標,去分析電壓電流之間的關系?好了,既然要做這么一件事,我們想辦法搞出來一個模型,再用我們簡單的KVL/KCL規則去一頓分析,最后我們得到了用怎么樣子的“四兩”去撥動怎么的“千斤”,換句話說,我們建立小信號模型是為了推導出MOS管輸出與輸入關系的數學表達。下面先給出常見的NMOS的小信號模型,后續我們逐步拆解其構成:

如何得出上面的MOS管的小信號模型的呢?

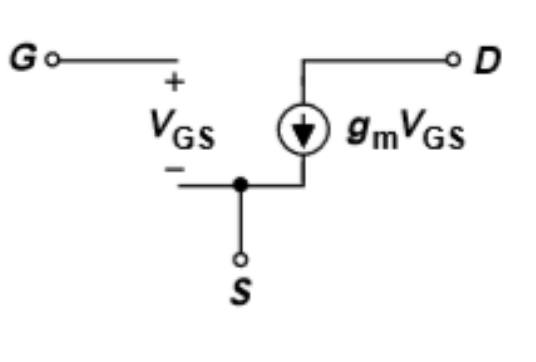

首先,對于MOS管而言,我們在柵源端加一個電壓變量,然后就可以在漏端去檢測到相應的電流變化,也就是說MOS管可以用連接在源漏之間的壓控電流源來模擬改變化,即得到如下基礎模型:

然后,我們將二級效應中的溝道調制效應考慮進來,也就是說此時我們的ID會多一個上文分析到的因子,我們對其除以電壓,就可以等效為一個電阻ro:

所以,此時的小信號模型可以變為這樣的:

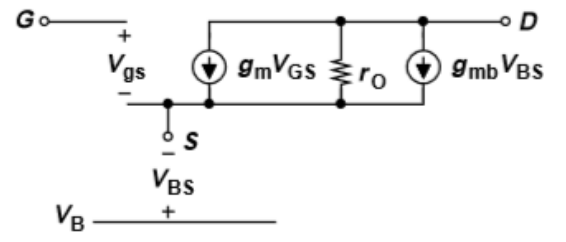

再然后,我們把二級效應中的體效應考慮進來,同樣的,根據上文的分析,我們的ID會多一個關于VTH的變化,也就是說,在柵源之間會存在一個VSB的相對電壓源存在,進而會在漏端求電流時的受控源會多一個gmb*VSB的存在,所以,此時的小信號模型繼續變為:

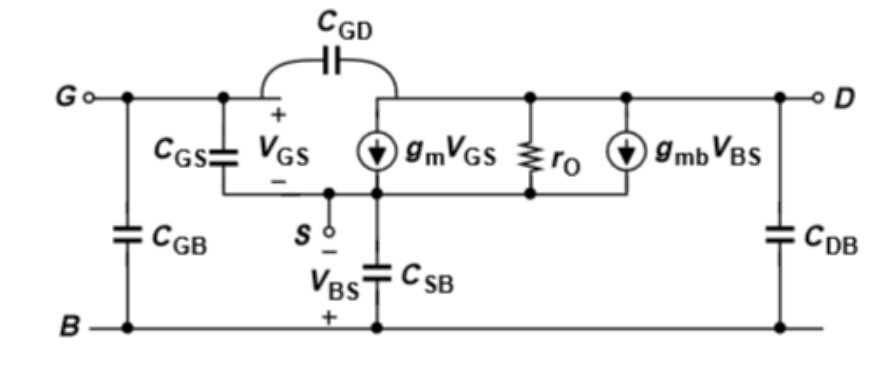

最后,我們再把MOS管的電容效應考慮進來,也就是說我們在分析導通特性那會聊到了,在MOS管內部會存在一些溝道,可以等效為電容,那么可以簡單地得到下圖:

所以,我們將其帶入到上面考慮了MOS管二級效應的小信號模型之中,最終我們得到了MOS管的小信號模型如下所示:

那么,如何利用該小信號模型來分析IV曲線或者跨導特性呢?大家可以自行下來拆解,或者如果這期反饋還不錯,大家都在積極點贊轉發啥的,那么我們可以后面找個時間再出一期,來分析信號如何在該模型之中傳播的。

2)MOS管的SPICE模型

其實SPICE模型,和上面的小信號模型一樣,是描述電路特性蕓蕓眾生中的一員大將。

在我們的科學家(主要是UCB大學的教授們)和工程師們多年的努力下,找到了一套描述管子工作狀態的程序化描述語言——SPICE模型。SPICE是Simulation Program with Integrated Circuit Emphasis的縮寫,是一種功能強大的通用模擬電路仿真器,描述器件內部的實際電氣連接,該程序是美國加利福尼亞大學伯克利分校電工和計算科學系開發的,主要用于集成電路的電路分析程序中,Spice的網表格式變成了通常模擬電路和晶體管級電路描述的標準,其第一版本于1972年完成,是用Fortran語言寫成的,1975年推出正式實用化版本,1988年被定為美國國家工業標準,主要用于IC,模擬電路,數模混合電路,電源電路等電子系統的設計和仿真。

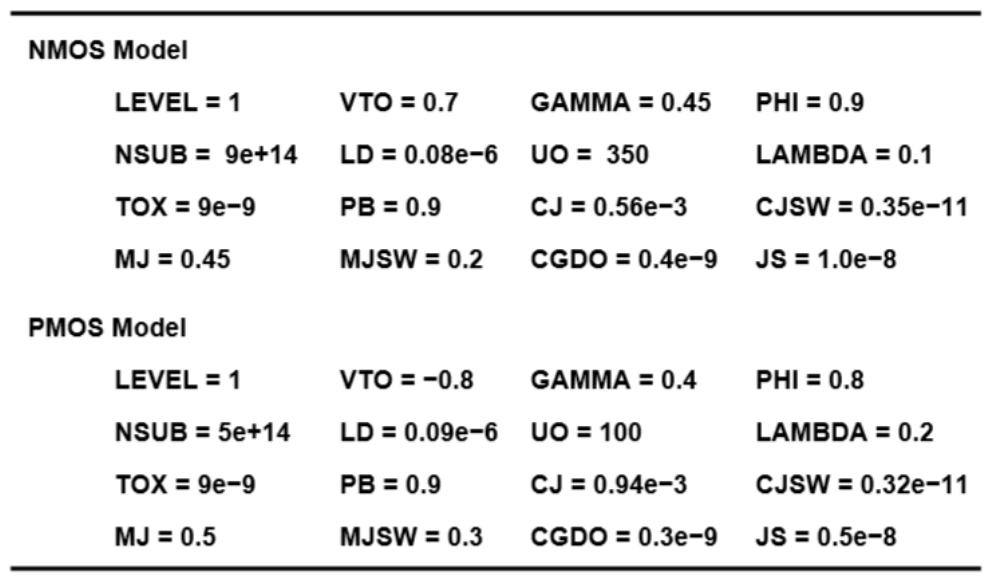

好了,到底什么是SPICE模型?能不能具體化一點,哈哈,咱就不賣關子了,本文就搬運一個0.5um CMOS工藝的“LEVEL1” SPICE模型:

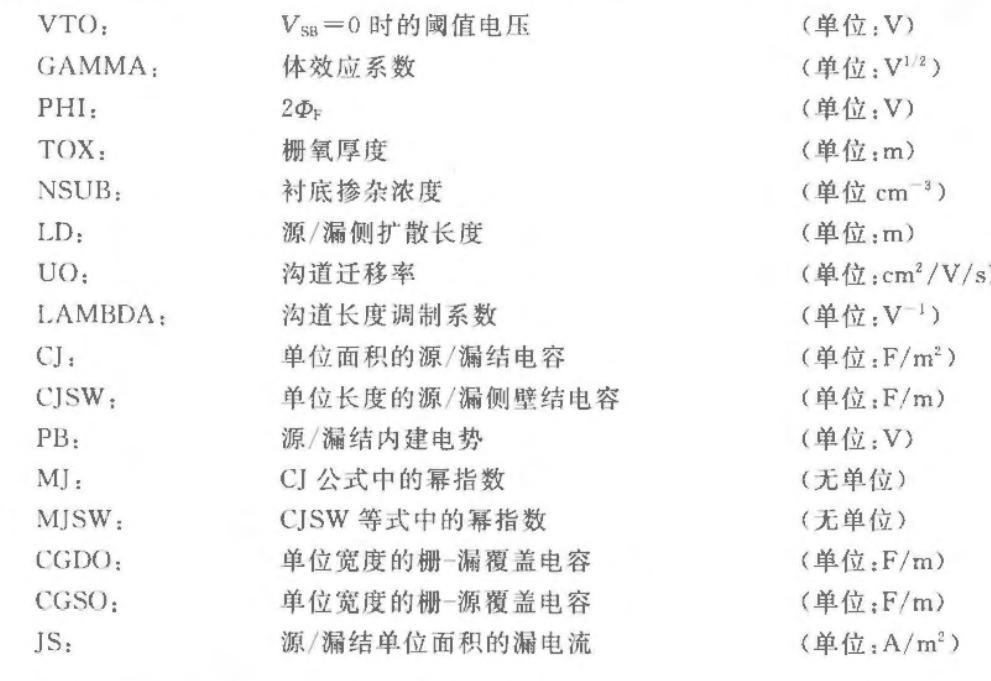

有沒有驚訝到您,這這這,為啥就只個表格呢?哈哈,對頭,其實它就是一個表格,通過程序語言來建立各個網格之間的關系的。那么這個咋個看呢?如下:

當然,還有一些描述MOS管的模型,比如IBIS模型,Verilog-AMS模型和VHDL-AMS模型等等,咱們就不一一去訴說了,當然,最主要的還是我不太會、不了解。。。

好了,本期內容就到此,希望大家有所收獲~

——END——

作者:RFIC_拋磚

同時歡迎加入《射頻微波芯片設計》學習交流群

長按識別上方二維碼加小編為好友

說明“《射頻微波芯片設計》學習”,拉您入群

粵公網安備 44030902003195號

粵公網安備 44030902003195號