眾所周知,對于碳化硅MOSFET(SiC MOSFET)來說,高質量的襯底可以從外部購買得到,高質量的外延片也可以從外部購買到,可是這只是具備了獲得一個碳化硅器件的良好基礎,高性能的碳化硅器件對于器件的設計和制造工藝有著極高的要求,接下來我們來看看安森美(onsemi)在SiC MOSFET器件設計和制造上都獲得了哪些進展和成果。

Die Layout

下圖是一張制造測試完成了的SiC MOSFET的晶圓(wafer)。

圖一

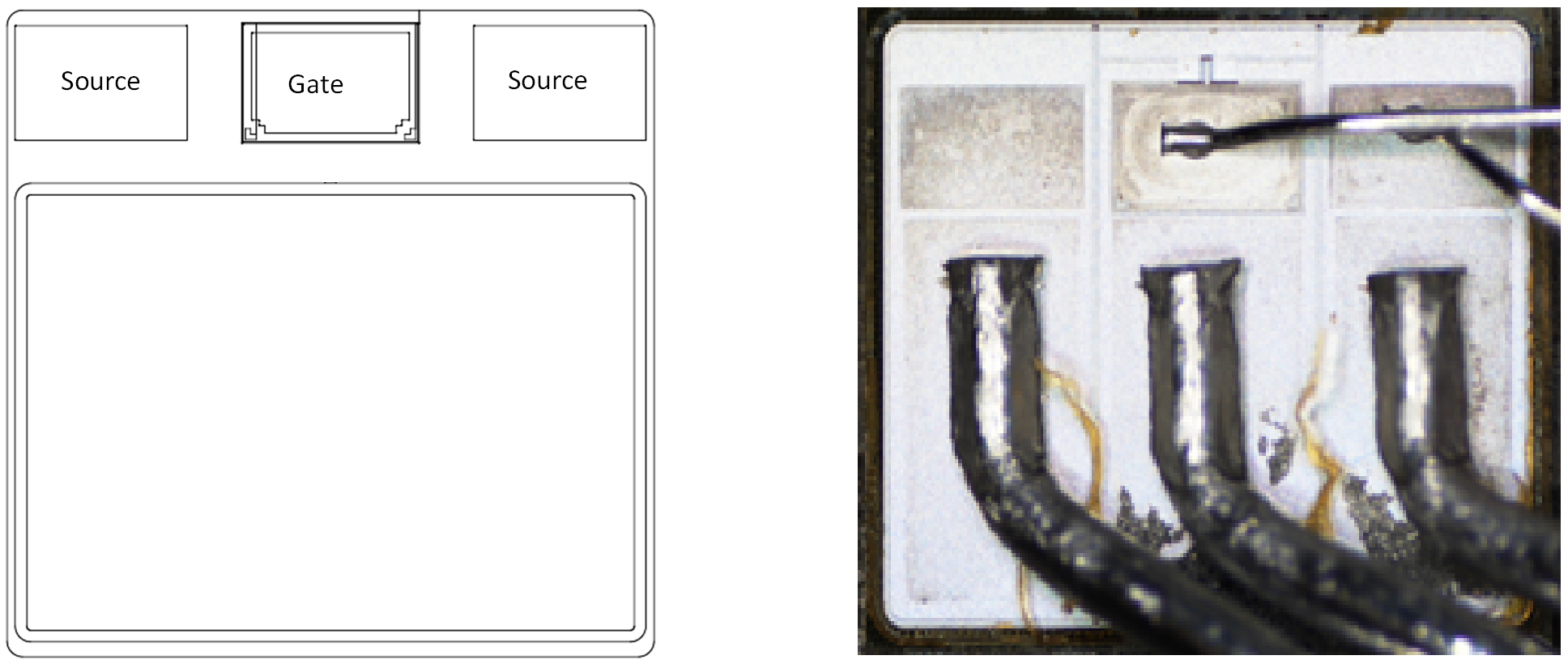

芯片的表面一般是如圖二所示,由源極焊盤(Source pad),柵極焊盤(Gate Pad), 開爾文源極焊盤(Kelvin Source Pad)構成。有一些只有Gate pad,如上圖的芯片就沒有Kelvin source pad。

圖二

在這里我們仔細觀察芯片的周圍有一個很窄的環形,這個有人叫耐壓環,這是很形象的說法。它的作用主要是提升芯片的耐壓,我們叫耐壓環(Edge termination Ring),通常是JTE結構,其實一個芯片主要就是由三部分構成,Terminal Ring,Gate Pad , Kelvin Source Pad和開關單元(Active Cell),一個芯片外圍一圈是耐壓環,Gate pad把柵極信號傳遞到每一個Cell上面,然后里面是上百萬個Active Cell。通常大家關注比較多的是Active Cell,因為芯片的開關和導通性能主要是和Active Cell有比較大的關系。在這里我們把芯片的layout還有各個部分的作用特點總結一下,這樣方便大家對芯片有一個更好的認識。

耐壓環(Edge termination Ring)

• 環繞著芯片的開關單元,目前大多數采用JTE結構。

• 有效控制了漏電流,提高了SiC器件的可靠性和穩定性;

• 減小了電場集中效應,提高了SiC器件的擊穿電壓,SiC MOSFET的擊穿電壓和具體的每一個開關單元有關,同時和耐壓環也有很大的關系。

• 防止離子遷移,JTE技術可以用于抑制移動離子的漂移,從而提高SiC MOSFET的可靠性和穩定性。具體來說,JTE技術可以在SiC MOSFET的邊緣區域形成一些深度摻雜的控制區域,這些區域可以有效地抑制移動離子的漂移。此外,JTE技術還可以在控制區域中引入一些特殊的物質,例如氮、硼等,這些物質可以與移動離子發生化學反應,從而減少其在MOSFET中的積累和漂移。

柵極焊盤和(Gate Pad),開爾文源極(Kelvin Source Pad)

• 柵極pad主要作用就一個,把柵極的信號傳輸到各個開關單元,同時提一下,安森美的芯片是集成了柵極電阻的,這樣在模塊封裝上可以節省空間和一些成本。

• 開爾文源極主要是增加了開關速度,減小開關損耗。不過在做并聯使用的時候,就需要特別的設計來使用它。

開關單元(Active Cell)

• 電流導通和關閉的路徑

• 所有的開關單元是并聯

• 固定的單元特性下,單元的數量決定了整個芯片的導通電阻大小和短路電流能力。

• 目前主要分為平面和溝槽兩種結構

我們已經對SiC MOSFET的表面layout有了認識,在SiC的芯片里Edge terminal和Active Cell是非常重要的兩部分,安森美在JTE的設計上具有豐富的經驗,在SiC MOSET上已經從M1發展到了M3,通過幾代的技術迭代發展,JTE設計仿真和制造非常的成熟。我們來總結一下JTE的一些特點和一些設計考慮因素。

SiC JTE(結延伸區)是用于改善硅碳化物(SiC)功率器件電壓阻斷能力的結構。SiC JTE的設計對于實現所需的擊穿電壓并避免因器件邊緣處高電場而導致的過早擊穿至關重要。

以下是SiC JTE設計的一些關鍵考慮因素:

1. JTE區域的寬度和摻雜:JTE區域的寬度和摻雜濃度確定器件邊緣處的電場分布。較寬和重摻JTE區域可以減少電場并提高擊穿電壓。

2. JTE的錐角和深度:JTE的錐角和深度影響電場分布和擊穿電壓。較小的錐角和較深的JTE可以減少電場并提高擊穿電壓。

3. 表面鈍化:表面鈍化層對于減少表面泄漏并提高擊穿電壓非常重要。需要特別為SiC JTE器件精心設計和優化鈍化層。

4. 熱設計:SiC JTE器件可以在比其Si對應物更高的溫度下工作。但是,高溫也可能降低器件性能和可靠性。因此,在SiC JTE設計過程中應考慮熱設計,如散熱和熱應力。 總體而言,SiC JTE設計是一個復雜的過程,涉及各種設計參數之間的權衡。需要進行仔細的優化和仿真,以實現所需的器件性能和可靠性。

Active Cell 開關單元 – SiC MOSFET的核心

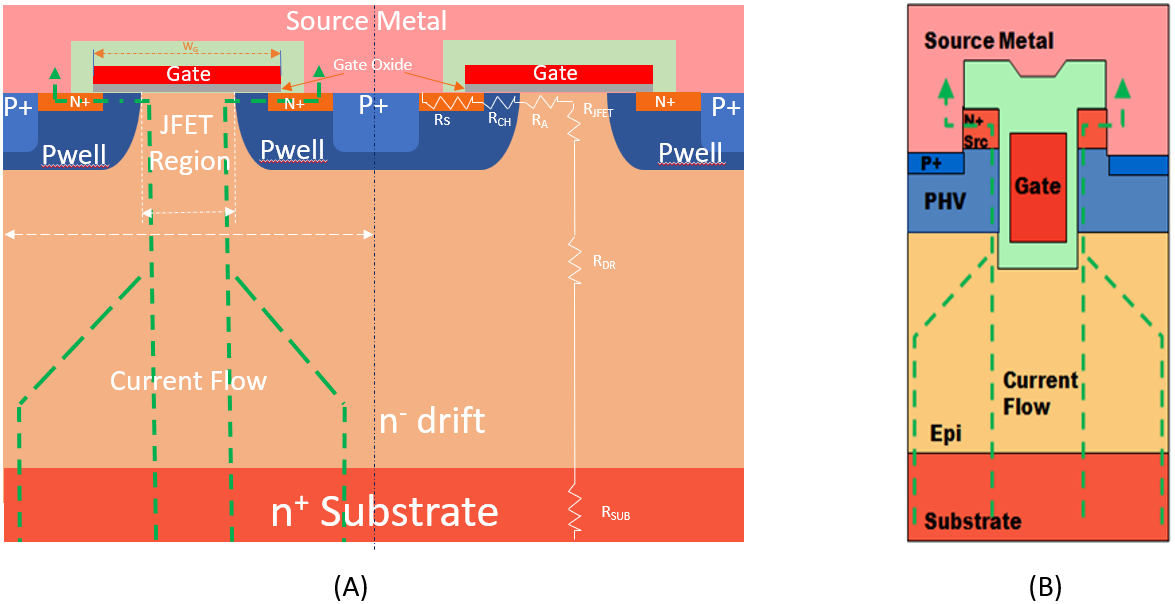

開關單元是SiC MOSFET中一個非常重要的部分。我們可以把MOSFET(硅和碳化硅)根據它們的柵極結構分成兩類:平面結構和溝槽結構。它們的示意圖如圖三所示。如果從結構上來說硅和碳化硅MOSFET是一樣的,但是從制造工藝和設計上來說,由于碳化硅材料和硅材料的特性導致它們要考慮的點大部分都不太一樣。比如SiC大量使用了干蝕刻(Dry etch),還有高溫離子注入工藝,注入的元素也不一樣。

圖三

當前國際上的SiC MOSFET絕大部分都采用了圖三A的平面結構,有少部分的廠家采用了圖三B的溝槽結構。從發展的角度來看,最終都會衍生到溝槽結構。但是目前的平面結構的潛力還是可以繼續深挖的,而溝槽結構也沒有表現出它們應當有的水平,在這里我們引入一個統一的尺度來衡量它們的性能 - Rsp(Rdson * area),標識的是單位面積里的導通電阻大小。平面結構的SiC MOSFET具有可靠性高,設計加工簡單的優點。安森美用在汽車主驅逆變器里的SiC MOSFET的Rsp 從第一代M1的4.2 m?*cm2降低到M2的2.6 m?*cm2,目前的最新的M3e常溫下的Rsp性能和友商的溝槽結構的SiC MOSFET的水平一致,而高溫下的Rsp則低于友商溝槽結構SiC MOSFET的Rsp,達到了行業領先的水平。M3e的cell pitch值和目前的溝槽結構的SiC MOSFET pitch值相當,這表明安森美在平面結構的SiC MOSFET發展優化到了一個相當高的水平。當然一個MOSFET的性能不僅僅看Rsp,還要考慮開關損耗。通過前幾代的SiC MOSFET發展,以及根據大量的客戶應用反饋,安森美SiC MOSFET器件優化了導通損耗,開通損耗,反向恢復損耗以及短路時間,使得它們在客戶的應用中達到最優的一個效率。

SiC MOSFET的平面結構的Active Cell的設計制造方向主要是減小開關單元間距也就是pitch值,提升開關單元的密度,減小Rdson,提升柵極氧化層的可靠性。

如圖三A中的結構為了盡可能的減小導通電阻,需要調整開關單元的間距,pitch值和Wg也就是柵極的寬度有一定的關系,pitch值變小,Wg也相應變小,這個對于柵極的可靠性是有一定好處的,在SiC MOSFET里,柵極氧化層(Gate Oxide)非常的薄,小于100納米,因此在SiC的生產工藝中使用了干式蝕刻的方法來控制加工的精度。

根據圖三A中的導通電阻示意圖,我們可以得出Rdson=Rs+Rch+Ra+Rjfet+Rdrif+Rsub, 在這里面Rch和Ra占比最大,超過60%以上,所以它們變成了設計和工藝優化的一個重點方向之一。不過也不是一味的減小開關單元柵極的寬度就可以減小Rsp,柵極的Wg寬度減小到一定范圍,反而會導致Rsp變大,在設計的時候需要綜合考慮以上的參數相互之間的影響,這樣才能獲得一個比較理想的優化結果,安森美經過幾代的工藝迭代發展,其平面結構的SiC MOSFET上已經在性能,良率,可靠性等方面發展得相對成熟。

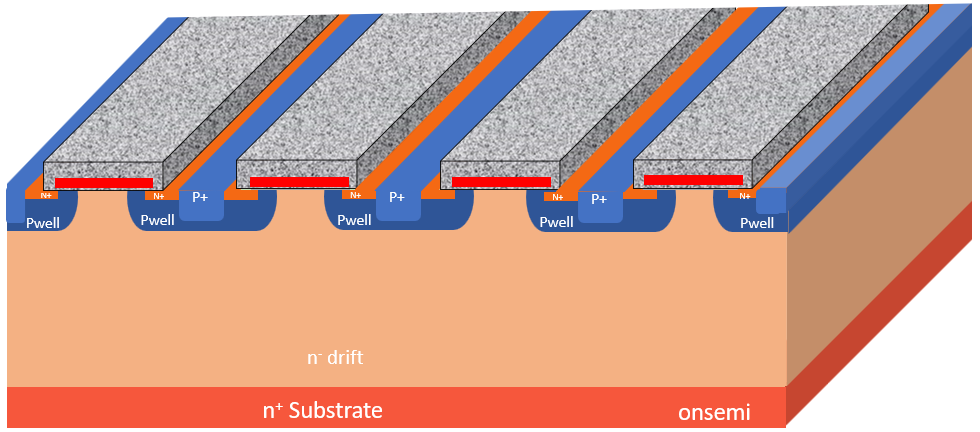

在芯片里,每個active cell是并聯在一起的,圖四是一個芯片的截面圖的示意圖,在這里采用的是帶狀結構的布局。從這里大家會對于芯片可以有更形象的了解。

圖四 芯片的截面圖

以下是SiC MOSFET Rdson設計的一些關鍵考慮因素:

1. 通道寬度和摻雜:SiC MOSFET的通道寬度和摻雜濃度會影響Rdson和電流密度。較寬和重摻的通道可以降低Rdson并提高電流承載能力。

2. 柵極氧化層厚度:柵極氧化層的厚度影響柵極電容,進而影響開關速度和Rdson。較薄的柵極氧化物可以提高開關速度,但也可能增加柵極漏電流,并增加氧化層擊穿失效的風險。

3. 柵極設計:柵極設計影響柵極電阻,進而影響開關速度和Rdson。較低的柵極電阻可以提高開關速度,但也可能增加柵極電容。總體而言,SiC MOSFET Rdson設計是一個復雜的過程,涉及綜合考慮各個參數之間的相互影響。需要進行仔細的優化和仿真并且進行試驗和測試,以實現所需的器件性能和可靠性。

集成片上柵極電阻

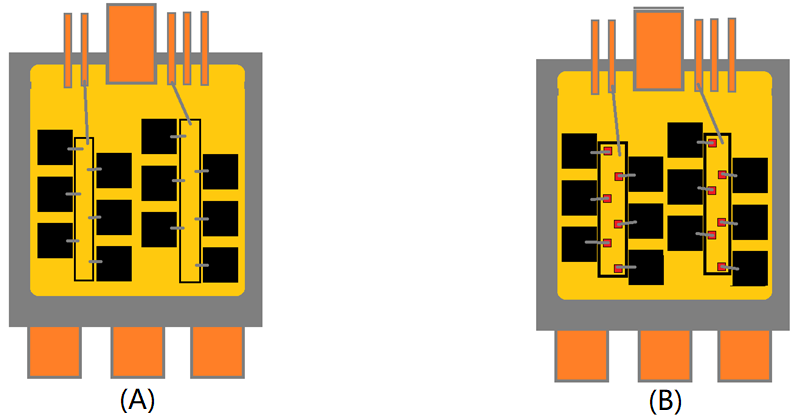

安森美所有針對主驅逆變器開發的SiC MOSFET都集成了柵極的電阻,我們可以從圖五看到有無電阻的區別。圖五A是不需要柵極電阻(芯片上集成了),圖五B是需要額外加一個柵極電阻。

圖五

集成柵極電阻會給模塊設計和制造帶來一些好處:

• 簡化了模塊綁定線的工藝,降低了失效率。

• 減少了焊接電阻到DBC的工藝

• 降低了BOM和制造成本

• 便于封裝的相對小型化設計和制造

由于篇幅關系,加上SiC MOSFET的設計制造工藝非常的復雜,不是三言兩語能夠闡述的清楚的,希望本文能讓大家對SiC MOSFET的設計和制造有一個概念。安森美在SiC 功率器件的設計和制造領域擁有十多年的經驗,我們的SiC MOSFET產品經過幾代的迭代發展,無論是性能還是品質和可靠性都已經穩定和具有競爭力,非常 歡迎選擇和使用我們的SiC MOSFET產品。

粵公網安備 44030902003195號

粵公網安備 44030902003195號