ADALM2000實(shí)驗(yàn):CMOS邏輯電路、D型鎖存器

作者:Doug Mercer,顧問研究員和Antoniu Miclaus,系統(tǒng)應(yīng)用工程師,ADI公司

目標(biāo)

本實(shí)驗(yàn)活動(dòng)的目標(biāo)是進(jìn)一步強(qiáng)化上一個(gè)實(shí)驗(yàn)活動(dòng)“ADALM2000實(shí)驗(yàn):使用CD4007陣列構(gòu)建CMOS邏輯功能”中探討的CMOS邏輯基本原理,并獲取更多使用復(fù)雜CMOS門級(jí)電路的經(jīng)驗(yàn)。具體而言,您將了解如何使用CMOS傳輸門和CMOS反相器來(lái)構(gòu)建D型觸發(fā)器或鎖存器。

背景知識(shí)

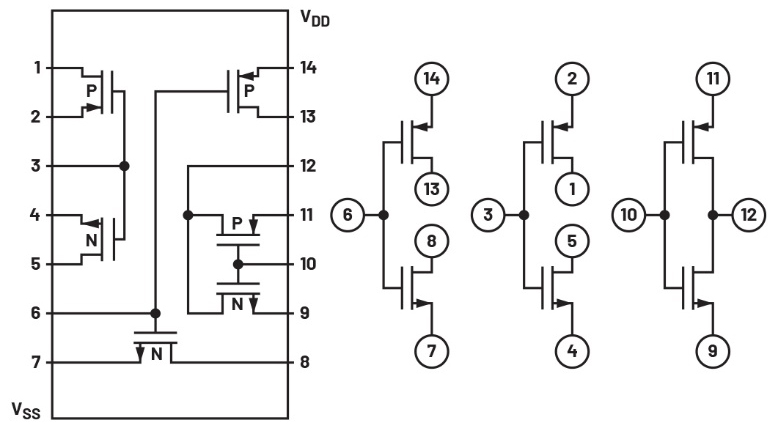

為了在本實(shí)驗(yàn)活動(dòng)中構(gòu)建邏輯功能,需要使用ADALP2000模擬部件套件中的CD4007 CMOS陣列和分立式NMOS和PMOS晶體管(ZVN2110A NMOS和ZVP2110A PMOS)。CD4007由3對(duì)互補(bǔ)MOSFET組成,如圖1所示。每對(duì)共用一個(gè)共柵(引腳6、3和10)。所有PMOSFET(正電源引腳14)以及NMOSFET(地引腳7)的襯底都共用。左邊的互補(bǔ)MOSFET對(duì),NMOS源極引腳連接到NMOS襯底(引腳7),PMOS源極引腳連接到PMOS襯底(引腳14)。另外兩對(duì)均為通用型。右邊的互補(bǔ)MOSFET對(duì),NMOS的漏極引腳連接到PMOS的漏極引腳,即引腳12。

圖1.CD4007功能框圖。

CD4007是一款多功能IC,我們?cè)谏弦粋€(gè)實(shí)驗(yàn)活動(dòng)中已有所了解。例如,單個(gè)CD4007可用于構(gòu)建一個(gè)反相器鏈(包括三個(gè)反相器)、一個(gè)反相器加上兩個(gè)傳輸門或其他復(fù)雜的邏輯功能,如NAND和NOR門。反相器和傳輸門尤其適合構(gòu)建D型鎖存器或主/節(jié)點(diǎn)觸發(fā)器。

靜電放電

CD4007與許多CMOS集成電路一樣,很容易被靜電放電損壞。CD4007包括二極管,可防止其受靜電放電的影響,但如果操作不當(dāng)仍可能會(huì)損壞。使用對(duì)靜電敏感的電子產(chǎn)品時(shí),通常會(huì)使用防靜電墊和腕帶。然而,在家里(正規(guī)的實(shí)驗(yàn)環(huán)境之外)工作時(shí),可能沒有這些物品。避免靜電放電的一種低成本方法是在接觸IC之前先使自己接地。在操作CD4007之前,使積聚的靜電放電將有助于確保在實(shí)驗(yàn)過程中不會(huì)損壞芯片。

材料

? ADALM2000主動(dòng)學(xué)習(xí)模塊

? 無(wú)焊試驗(yàn)板

? 1個(gè)CD4007(CMOS陣列)

? 2個(gè)ZVN2110A NMOS晶體管

? 2個(gè)ZVP2110A PMOS晶體管

說(shuō)明

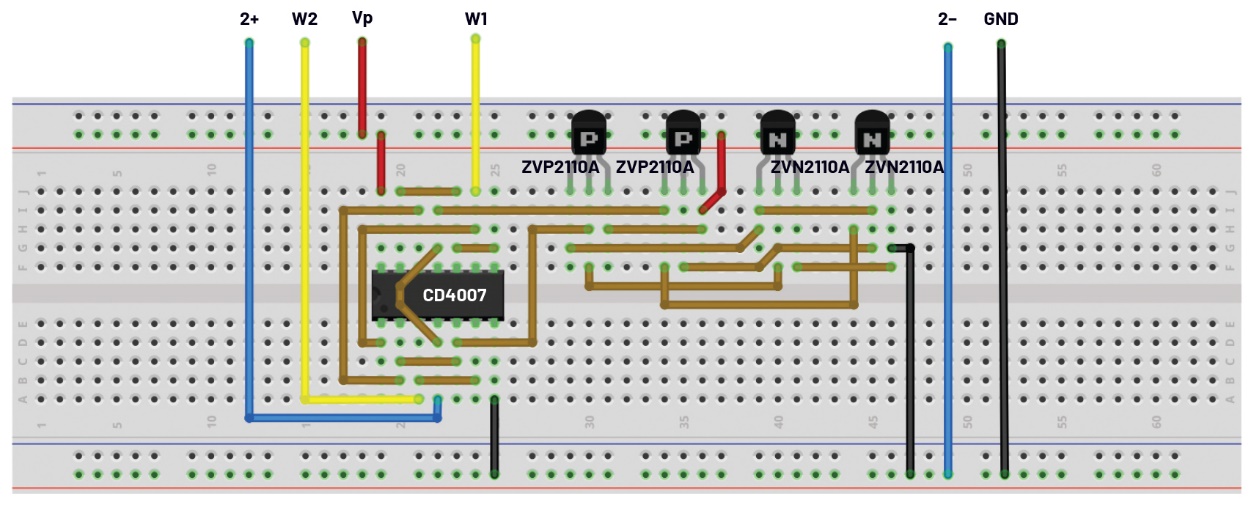

現(xiàn)在我們將結(jié)合使用之前練習(xí)中的反相器鏈構(gòu)建的雙傳輸門來(lái)構(gòu)建D型鎖存器,如圖2所示。兩個(gè)傳輸門協(xié)同工作以實(shí)現(xiàn)D型鎖存器。在鎖存器的透明模式下,當(dāng)CLK=0時(shí),第一個(gè)傳輸門(左)打開,同時(shí)第二個(gè)傳輸門(右)關(guān)閉。D通過第一個(gè)傳輸門和兩個(gè)串聯(lián)的反相器傳輸至輸出端(Q)。在鎖存器的保持模式下,當(dāng)CLK=1時(shí),第一個(gè)傳輸門關(guān)閉,但第二個(gè)傳輸門打開。因此,輸入端D中的任何變化都不會(huì)反映在輸出端Q上。不過,現(xiàn)已開啟的第二個(gè)傳輸門可確保通過在兩個(gè)串聯(lián)的反相器周圍形成的閉合正反饋回路來(lái)保留Q上先前的邏輯電平。在無(wú)焊試驗(yàn)板上構(gòu)建圖2所示的D型鎖存器電路。器件M1至M6采用CD4007 CMOS陣列,兩個(gè)反相器級(jí)中的每一級(jí)(反相器級(jí)M7和M8,以及M9和M10)使用一個(gè)ZVN2110A NMOS和一個(gè)ZVP2110A PMOS。電路使用ADALM2000的固定5 V電源供電。

圖2.D型鎖存器。

硬件設(shè)置

在實(shí)驗(yàn)最初,將兩個(gè)AWG輸出配置直流源。根據(jù)需要,示波器通道將用于監(jiān)控電路的輸入和輸出。固定5 V電源用于為電路供電。在此實(shí)驗(yàn)中,應(yīng)禁用固定–5 V電源。

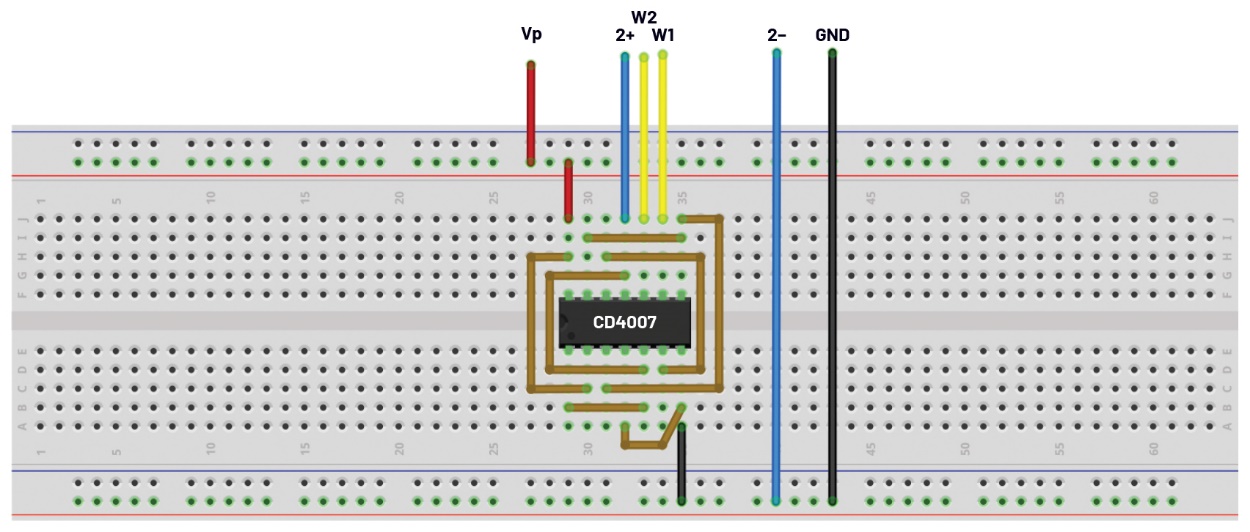

圖3.D型鎖存器試驗(yàn)板連接。

程序步驟

連接引腳1和9,鎖存器的D輸入端連接到AWG1的輸出端。連接引腳4和11,鎖存器的Q輸出端連接到示波器通道2。連接引腳6,作為連接到AWG2的CLK。確保打開固定5 V電源。

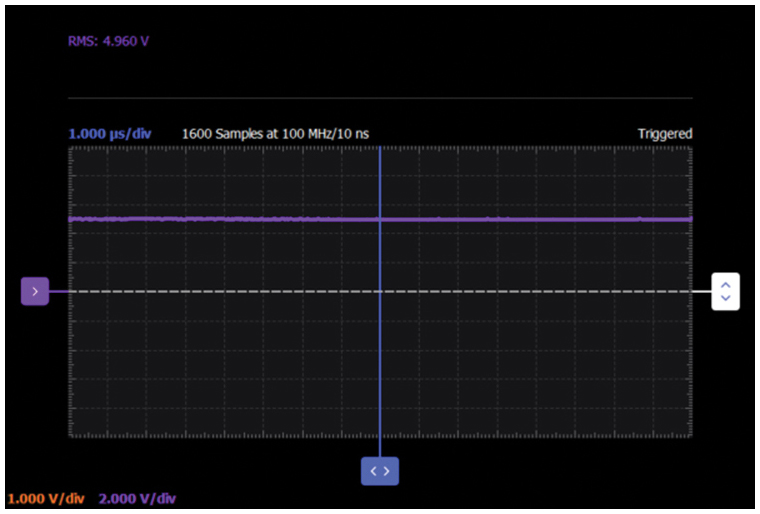

首先,打開AWG控制界面并將AWG2設(shè)置為0 V直流電壓,對(duì)CLK施加邏輯低電平。將AWG1設(shè)置為5 V直流電壓,對(duì)D輸入端施加邏輯高電平。

觀察示波器通道2上鎖存器的輸出端Q。示波器界面上應(yīng)顯示穩(wěn)定的5 V電壓。捕獲屏幕截圖。

圖4.Scopy屏幕截圖。

將AWG1設(shè)置為0 V直流電壓,對(duì)D輸入端施加邏輯低電平。觀察示波器上的輸出。這是鎖存器的透明模式。此時(shí)應(yīng)能看到示波器通道2也是0 V直流電壓。現(xiàn)在將AWG2設(shè)置為5 V直流電壓,對(duì)CLK施加邏輯高電平。同時(shí)將AWG1設(shè)置為5 V直流電壓,對(duì)D輸入端施加邏輯高電平。

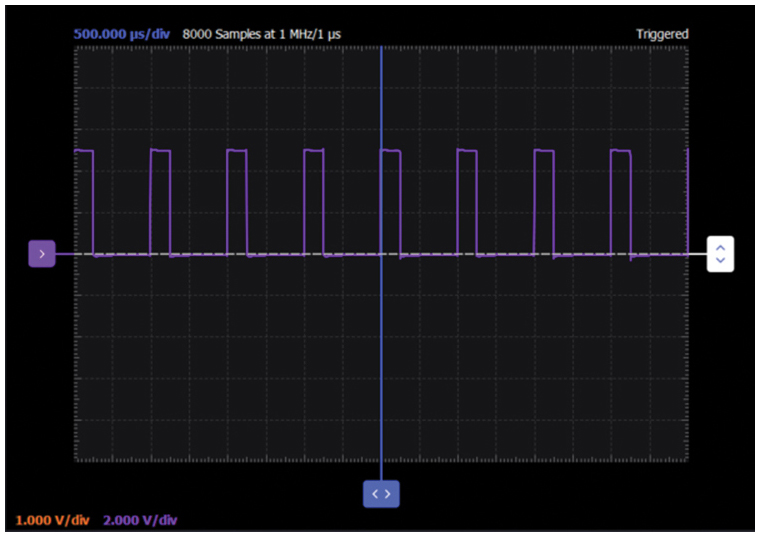

觀察示波器界面上的Q輸出。由于D輸入端之前為低電平,因此盡管將D更改為邏輯高電平,仍會(huì)顯示穩(wěn)定的低電平。捕獲屏幕截圖。這是電路的保持模式。

圖5.Scopy屏幕截圖。

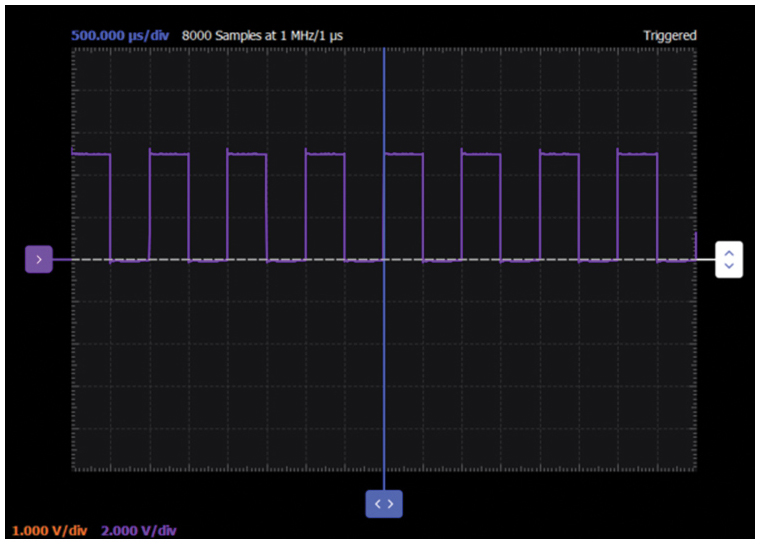

現(xiàn)在將兩個(gè)AWG通道均配置為峰峰值為5V的方波。將AWG1設(shè)置為1 kHz頻率,將AWG2設(shè)置為2 kHz頻率或AWG1頻率的兩倍。將AWG2的相位設(shè)置為0度。確保將AWG設(shè)置為同步運(yùn)行。

觀察示波器界面上在上述CLK和D輸入下相應(yīng)的Q輸出。捕獲各種波形并保存截圖,用于包含在實(shí)驗(yàn)報(bào)告中。

圖6.Scopy屏幕截圖。

現(xiàn)在將AWG2的相位設(shè)置為90度。再次觀察示波器界面上在此時(shí)CLK和D輸入下相應(yīng)的Q輸出。與AWG2相位為0度時(shí)相比有何變化?說(shuō)明原因。捕獲各種波形并保存截圖,用于包含在實(shí)驗(yàn)報(bào)告中。

圖7.Scopy屏幕截圖。

問題

單個(gè)D型鎖存器將使輸入信號(hào)延遲1/2時(shí)鐘周期。說(shuō)明時(shí)鐘相位相反的兩個(gè)串聯(lián)D型鎖存器如何構(gòu)成主節(jié)點(diǎn)D型觸發(fā)器,可以使輸入信號(hào)延遲一個(gè)完整的時(shí)鐘周期。

如果還有CD4007陣列可用,可構(gòu)建主節(jié)點(diǎn)D型觸發(fā)器作為額外的練習(xí)。

替代形式

圖2所示的D型鎖存器使用具有NMOS和PMOS晶體管的互補(bǔ)傳輸門。單個(gè)NMOS或PMOS無(wú)法傳遞具有相同強(qiáng)度(即導(dǎo)通電阻)的高低邏輯電平。單個(gè)NMOS器件可以傳遞強(qiáng)邏輯電平0,但會(huì)傳遞弱邏輯電平1。相反,單個(gè)PMOS器件可以傳遞強(qiáng)邏輯電平1,但會(huì)傳遞弱邏輯電平0。

在許多集成電路設(shè)計(jì)案例中,內(nèi)部信號(hào)僅在內(nèi)部電路模塊之間傳遞,此時(shí)單個(gè)NMOS或PMOS晶體管傳遞的非對(duì)稱驅(qū)動(dòng)不是主要問題。在這種情況下,鎖存器中固有的正反饋可能會(huì)有所幫助。可以采用簡(jiǎn)化的D型鎖存器,即只使用6個(gè)器件而不是圖2中使用的10個(gè)器件,如圖8(鎖存器在上升沿)和9(鎖存器在下降沿)所示。

圖8.6晶體管上升沿D型鎖存器。

圖9.6晶體管下降沿D型鎖存器。

硬件設(shè)置

圖10.6晶體管上升沿D型鎖存器試驗(yàn)板連接。

圖11.6晶體管下降沿D型鎖存器試驗(yàn)板連接。

說(shuō)明

對(duì)試驗(yàn)板進(jìn)行任何更改之前,確保關(guān)閉固定5 V電源。在無(wú)焊試驗(yàn)板上,將圖2中的電路重新配置為圖3中的電路。確保打開固定5 V電源。重復(fù)相同的步驟,將AWG1連接到D輸入端,將AWG2連接到CLK輸入端。驗(yàn)證鎖存器的工作情況,它將在輸入時(shí)鐘的適當(dāng)邊沿鎖存邏輯0和邏輯1輸入。

最后,將無(wú)焊試驗(yàn)板上的電路重新配置為圖4中的電路。確保打開固定5 V電源。重復(fù)相同的步驟,將AWG1連接到D輸入端,將AWG2連接到CLK輸入端。驗(yàn)證鎖存器的工作情況,它將在輸入時(shí)鐘的適當(dāng)邊沿鎖存邏輯0和邏輯1輸入。

替代元件選擇

使用四個(gè)獨(dú)立NMOS和PMOS晶體管(ZVN2110A和ZVP2110A)構(gòu)建的反相器對(duì)也可以由第二個(gè)CD4007 IC構(gòu)成,也可以使用例如 74HC04 或 CD4049 等六反相器 IC 的 CMOS 反相器。

問題:

1.您能說(shuō)出D型鎖存器的主要用途(應(yīng)用)嗎?

您可以在學(xué)子專區(qū)論壇上找到問題答案。

關(guān)于ADI公司

Analog Devices, Inc. (NASDAQ: ADI)是全球領(lǐng)先的半導(dǎo)體公司,致力于在現(xiàn)實(shí)世界與數(shù)字世界之間架起橋梁,以實(shí)現(xiàn)智能邊緣領(lǐng)域的突破性創(chuàng)新。ADI提供結(jié)合模擬、數(shù)字和軟件技術(shù)的解決方案,推動(dòng)數(shù)字化工廠、汽車和數(shù)字醫(yī)療等領(lǐng)域的持續(xù)發(fā)展,應(yīng)對(duì)氣候變化挑戰(zhàn),并建立人與世界萬(wàn)物的可靠互聯(lián)。ADI公司2022財(cái)年收入超過120億美元,全球員工2.4萬(wàn)余人。攜手全球12.5萬(wàn)家客戶,ADI助力創(chuàng)新者不斷超越一切可能。更多信息,請(qǐng)?jiān)L問www.analog.com/cn。

關(guān)于作者

Doug Mercer于1977年畢業(yè)于倫斯勒理工學(xué)院(RPI),獲電子工程學(xué)士學(xué)位。自1977年加入ADI公司以來(lái),他直接或間接貢獻(xiàn)了30多款數(shù)據(jù)轉(zhuǎn)換器產(chǎn)品,并擁有13項(xiàng)專利。他于1995年被任命為ADI研究員。2009年,他從全職工作轉(zhuǎn)型,并繼續(xù)以名譽(yù)研究員身份擔(dān)任ADI顧問,為“主動(dòng)學(xué)習(xí)計(jì)劃”撰稿。2016年,他被任命為RPI ECSE系的駐校工程師。

Antoniu Miclaus現(xiàn)為ADI公司的系統(tǒng)應(yīng)用工程師,從事ADI教學(xué)項(xiàng)目工作,同時(shí)為Circuits from the Lab®、QA自動(dòng)化和流程管理開發(fā)嵌入式軟件。他于2017年2月在羅馬尼亞克盧日-納波卡加盟ADI公司。他目前是貝碧思鮑耶大學(xué)軟件工程碩士項(xiàng)目的理學(xué)碩士生,擁有克盧日-納波卡科技大學(xué)電子與電信工程學(xué)士學(xué)位。

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)