作為3G移動通信標準中的兩個主要標準,W-CDMA和CDMA2000都采用碼分多址接入方式,且具有信道帶寬寬、數據速率多樣且支持高速率,不同業務采用信道編碼不同等共性;同時,這兩種標準之間在碼片速率、信道帶寬和信道選擇碼等方面也存在差異。這些方面以及為了提高系統容量在3G中將采用的智能天線技術(Smart Antenna)、多用戶檢測技術(MUD)等,使得軟件無線電技術在3G系統中有著廣泛的應用空間,同時也面臨巨大的技術挑戰。

以實現CDMA2000(含IS-95)和W-CDMA雙模軟件無線電系統為例,針對3G移動通信系統的具體情況,我們將分析3G中軟件無線電技術的可行性及實現所面臨的技術難題。討論是在傳統的流水線結構上進行的,首先討論傳統單用戶接收機的軟件無線電實現問題,然后討論卷積碼、Turbo碼譯碼的軟件實現,最后討論智能天線技術和多用戶檢測技術在軟件無線電實現中所面臨的問題。

多種3G移動通信標準的加入使得本來已經十分龐大的移動通信標準族變得更加繁雜。從近期發展上看,軟件無線電技術可以解決不同標準的兼容性,為實現全球漫游提供方便;從長遠發展上看,軟件無線電發展的目標是實現具有可以根據無線電環境變化而自適應地配置收/發信機的數據速率,調制、解調方式,信道編、譯碼方式,甚至調整信道頻率、帶寬以及無線接入方式的智能化無線通信系統,從而更加充分地利用頻譜資源,在滿足用戶QoS要求的基礎上使系統容量最大。當然,實現這一美好目標有待于理論與應用研究的進一步深入。

傳統單用戶接收方式的實現

這里的討論僅限于下行鏈路接收過程中的A/D變換器和數字處理子系統。討論是從實現各種無線電功能的計算復雜度這個角度進行的,而且僅討論資源需求中的主要問題,包括成形濾波和RAKE接收等。

首先,標準為實現W-CDMA和CDMA2000雙模無線電系統提供了基礎。為了在移動電臺中支持多種通信標準,從降低復雜度和造價等方面考慮,人們希望能用同一個主系統時鐘為每種工作模式產生工作時鐘,這個主時鐘可以是每種模式的時鐘頻率的最小公倍數。CDMA2000 1X(1.2288M)和W-CDMA(3.84M)碼片速率的最小公倍數是30.72MHz,CDMA20003X和W-CDMA碼片速率的最小公倍數是92.16MHz。由于這個公倍數較小,可用其二倍頻率184.32 MHz作為主系統時鐘,CDMA2000(1X和3X)或W-CDMA各自的時鐘均可由此主時鐘導出。所以說W-CDMA和CDMA2000標準為W-CDMA/CDMA2000多模移動臺的實現提供了方便。

其次,VLSI器件也為實現提供了有利條件。實現W-CDMA和CDMA2000雙模系統對A/D變換器和可編程DSP處理器提出了要求。

(1)A/D變換器

A/D變換器的采樣率選擇為61.44MHz。選擇的依據有兩方面:首先是為了滿足采樣定理。無線頻譜資源是十分有限的,這里假設分配給每個標準的頻譜都是25MHz,采樣定理要求采樣率至少是信號帶寬的2倍,實際中常取為信號帶寬的2.5倍,61.44MHz的采樣率基本滿足要求。

其次61.44MHz采樣率可由184.32 MHz的系統時鐘3倍降采樣直接得到。從最先進的A/D器件水平看,ADI公司的AD6644和AD9244在65MHz采樣率時能提供14bit的精度。其中AD6644在Nyquist頻帶上可提供100dB的FSDR(無寄生動態范圍指標),可滿足要求。

(2)DDC器件

DDC器件可選擇Intersil公司的HSP50214B-65。HSP50214B-65最高輸入樣本速率為65MHz,精度為16bit,并可以進行非整數倍的降采樣。這樣可以分別確定W-CDMA和CDMA2000的降采樣倍數。為了使后續處理部分能更精確地實現碼片同步,降低采樣后的數據速率取為碼片速率的4倍。于是得到W-CDMA的降采樣速率為4,CDMA2000 3X降采樣率為4.1667,CDMA2000 1X降采樣率為12.5。降采樣后的數據率分別為15.36MSPS(W-CDMA)、4.9152MSPS(CDMA2000 1X)和14.7456MSPS(CDMA2000 3X)。

(3)可編程DSP處理器

● 脈沖成型濾波處理計算量估計。脈沖成型濾波器也是按4采樣速率進行的。3GPP2明確給出了成型濾波器長度(在四采樣時,1X時的濾波器長度為48,3X時的濾波器長度為108)。3GPP協議中給出的成型濾波器是滾降因子為0.22的根平方升余弦濾波器,長度為25(單采樣率)的根平方升余弦濾波器可以滿足3GPP的要求。脈沖成型濾波器收發都要用到,而且是I、Q兩路,所以總的計算量仍然很大,對DSP處理能力要求很高,但是用FPGA實現比較方便。

● RAKE接收中的運算量估計。當完成精確的碼片同步后,脈沖成型濾波器輸出數據速率可以降為碼片速率,此后的計算都是在碼片速率基礎上進行的。RAKE完成解擴、解擾和多徑合并等處理。而解擾、解擴后的數據率與擴譜因子有關,對W-CDMA,擴譜因子取值范圍是4~512,所對應的數據率為960~7.5 kSPS,因此,最大比合并的計算量為K×0.03~K×3.84MIPS。CDMA2000可以得到相似結果。

發射過程的計算復雜度一般要小于接收過程的計算復雜度,所以,總的復雜度一般不會超出接收處理復雜度的兩倍。但是,應該說明的是上面的討論主要考慮的是數字處理部分中對總計算量起決定作用的功能模塊,而沒有考慮信源編碼及協議實現等所需要的處理量。目前最先進的DSP器件TMS320C6416的處理能力已經達到5.76GIPS。實現上述處理的要求可用兩片TMS320C6416芯片或者用FPGA來實現成型濾波器,用一片TMS320C6416來實現其余處理。

信道譯碼器的實現

CDMA2000和W-CDMA的信道編碼方案中都包括卷積碼和Turbo碼兩種方式。卷積碼采用Viterbi算法實現譯碼;Turbo碼譯碼器可以采用MAP算法和SOVA算法通過迭代實現,由于MAP算法十分復雜,實際中采用的是降低復雜度的LOG-MAP算法、MAX-LOG-MAP算法或SOVA算法。

Turbo碼譯碼器的計算復雜度與采用的算法、編碼器的約束長度和實現的迭代次數有關。各種算法中MAP算法復雜度最高,LOG-MAP算法次之,而SOVA算法復雜度最低。與這些算法復雜度依次降低相對應的是算法的精度相應地也降低了。在CDMA2000和WCDMA標準中,Turbo碼主要用于高速數據業務和高QoS要求的業務。估計中假設DSP芯片中乘、比較和查表等是在單指令下實現的。這種假設對于內部提供Viterbi算法支持的DSP芯片是成立的,如TMS320C54X信片等。當迭代次數N為6時,完全滿足CDMA2000標準中各種速率要求的Turbo碼譯碼器需要的運算量為2.7GIPS。

所以,在可編程DSP上用軟件實現Turbo碼的譯碼算法對DSP提出了很高的要求。一種可行的方案是用DSP+靈活的硬件譯碼器方法實現,DSP對硬件譯碼器進行配置,然后具體的譯碼算法在硬件中實現,解決了靈活性與處理要求高的矛盾。慶幸的是,在部分高級DSP芯片,如TMS320C6416中,針對3G移動通信標準中的信道編碼要求嵌入了高性能的Viterbi譯碼器和Turbo碼譯碼器。這些協處理器能完全滿足CDMA2000和W-CDMA標準中不同信道的譯碼要求,它們與DSP核心處理器并行工作,通過高性能DMA完成與DSP的數據交換。

智能天線的實現

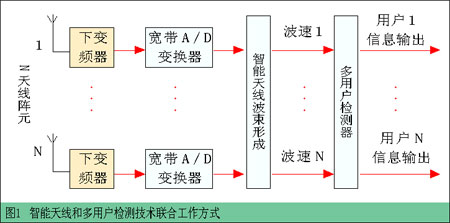

CDMA系統是干擾受限系統,多址干擾(包括同小區內用戶和其他小區用戶的干擾兩部分)和多徑干擾大大降低了CDMA系統的容量和覆蓋范圍。智能天線和多用戶檢測技術是降低多址干擾的兩種關鍵技術。圖1中給出了智能天線和多用戶檢測技術聯合的一種方式。

智能天線利用信號傳輸的空間特性,

自適應地調整天線方向,在跟蹤有用信號的同時減少或抵消干擾,增加信號干擾噪聲比,增加系統容量,提高通信頻譜利用率,降低信號發射功率,提高通信系統覆蓋范圍。智能天線波束形成算法可分為基于訓練序列的算法和盲算法兩大類,這些算法性能通常與通信系統的多址方式有關,如對于3G標準來說,MDIR算法是優選方案。因此,在用軟件無線電實現的可以支持不同頻段、不同多址方式的通信系統中,智能天線處理的體系結構與算法應當實時地與系統具體采用的標準保持一致。

智能天線處理包括調整天線陣元權系數和利用給定的權系數對輸入信號實時處理兩方面的計算。不同的智能天線算法復雜度不同,同一算法在系統中天線陣元數不同時復雜度也不同。對于基于訓練序列的智能天線算法,很多技術文獻中給出了采用LSM、RLS、FTF和LSL等自適應算法調整天線陣元權矢量的計算復雜度。相關文獻給出了適用于3G標準的MDIR算法的復雜度。結果表明,當基站的智能天線由4個陣元組成時,每個用戶的波束形成需要用一片浮點C67X DSP處理器。可見,對于同時要處理多個用戶信息的基站來說,實現MDIR智能天線算法難度較大。

相關文獻給出了一種次最優的、低運算復雜度的盲智能天線算法,適用于采用CDMA多址方式的移動通信系統。特點是采用時-空處理結構在解擴之后的基帶進行天線波束形成運算,調整天線權系數和實現陣列處理輸出都以信息符號的速率進行。而基站中采用此低復雜度智能天線算法的可行性很大。

多用戶檢測的實現

多用戶檢測技術通過信號處理手段來降低多址干擾、多徑干擾和遠近效應的影響,從而增加系統容量和覆蓋范圍。多用戶檢測器可分為最優的多用戶檢測器(MLSD檢測器)和次優型多用戶檢測器,而次優型多用戶檢測器又可分為線性多用戶檢測器和非線性多用戶檢測器。MLSD檢測器的復雜度為高。有關文獻中給出了部分降低復雜度的次優型多用戶檢測器的復雜度。復雜度過高是制約所有多用戶檢測方法使用的決定因素。例如,實現最優多用戶檢測器需要幾十至幾百TFLOPS,采用多級硬判決反饋算法的多用戶檢測方法需要至少7GFLOPS(或30GOPS)的處理量才能滿足WCDMA的要求。用當前最先進的定點DSP芯片TMS320C6416來實現3G系統的多用戶檢測器,需要至少7~8片并行處理才能實現。對于不受體積、功耗等因素制約的基站來說,采用當前最先進的微處理器技術已經可以實現軟件無線電多用戶檢測器。

當前的軟件無線電多用戶檢測器研究尚處于功能實現階段,通常采用全DSP結構或DSP加FPGA的混合結構來實現。在采用DSP和FPGA混合結構實現的軟件無線電多用戶檢測器中,用FPGA實現算法中計算量大、實時性要求高的部分,而DSP實現算法中結構復雜的部分,如矩陣求逆等。已有相關文獻報道,采用改進的匹配濾波器方式實現了匹配濾波MF接收機、近似解相關檢測器AD、嚴格解相關檢測器DC、最小均平方誤差解相關器MMSE、連續干擾對消檢測器SIC、并行干擾對消檢測器PIC等多用戶檢測算法。可根據業務QoS的不同要求,采用不同的多用戶檢測方法。全DSP結構的軟件無線電多用戶檢測器靈活性更高。而采用4片RISC處理器PowerPC G4實現的基于判決反饋算法多級干擾對消的多用戶檢測器,可同時支持128個實時的、同時通話的話音用戶。

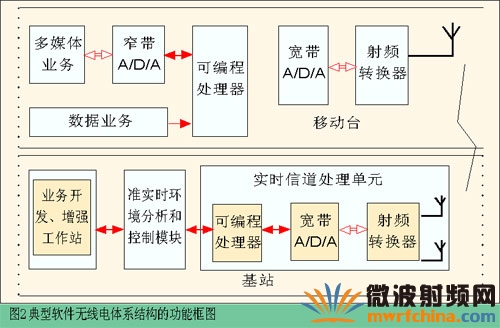

典型軟件無線電體系結構

典型的軟件無線電系統包括實時信道處理部分、準實時的環境管理部分以及用于開發增強業務的在線和脫機軟件等,圖2給出了典型軟件無線電體系結構的功能框圖。軟件無線電實現方式多樣,既可以利用ADC、FPGA、DSP和通用CPU形成具有SIMO和MIMO混合結構的流水線方式來實現,也可以在通用的PC機和工作站上實現,甚至可以通過高速網絡利用網絡資源實現。

摘自“計算機世界報”2005年1月

粵公網安備 44030902003195號

粵公網安備 44030902003195號