引 言

軟件無線電的出現,是無線電通信從模擬到數字、從固定到移動后,由硬件到軟件的第三次變革。簡單地說,軟件無線電就是一種基于通用硬件平臺,并通過軟件可提供多種服務的、適應多種標準的、多頻帶多模式的、可重構可編程的無線電系統。軟件無線電的關鍵思想是,將AD(DA)盡可能靠近天線和用軟件來完成盡可能多的無線電功能[1~2]。

蜂窩移動通信系統已經發展到第三代,3G系統進入商業運行一方面需要解決不同標準的系統間的兼容性;另一方面要求系統具有高度的靈活性和擴展升級能力,軟件無線電技術無疑是最好的解決方案。用ASIC(Application SpecificIntergrated CIRcuits)和DSP(Digital Singnal Processor)芯片搭建軟件無線電平臺是目前系統設計的主要方法[3~5],這種方法有兩個突出缺點:一是系統速度跟不上高速動態實時數字信號處理,二是系統體積大功耗高。這兩個突出缺點制約了軟件無線電在高速實時通信領域的應用前景。本文運用目前基于FPGA(Field Programmable GateArray)的SoPC (System onProgrammable Chip)技術構建軟件無線電平臺。大大提高了數字信號處理的能力和速度,并且降低了系統功耗,縮小了系統體積,為更高層次的3G無線通信要求提供了解決方案。

1 無線通信系統設計

1.1 系統設計

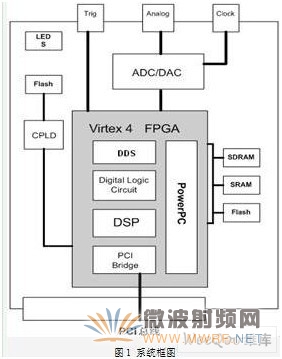

軟件無線電使得無線電具有更多的個性化特點,它以軟件方式定義多個頻段及多種調制波形接口。軟件無線電系統包括信號發射和接收兩部分,本文重點以接收流程進行論述。軟件無線電的RF(Radio Frequency)部分是一個多波束天線陣,可同時接收多個頻段、多個方向的射頻信號,并將射頻轉換為中頻信號[6~9]。如圖1所示,系統中包括Virtex-4 FX系列FPGA,模擬信號輸入端口,同步觸發端口,外接時鐘源,Flash(加載FPGA配置程序),CPLD,SDRAM,PCI接口,LED信號燈等部分。

提取用戶窄帶信號進行抽取由專用ADC芯片完成,數字下變頻部分由FPGA中的IP(Intellectual Property)模塊完成。用專用芯片進行模數轉換可以提高系統的穩定性和可靠性;用IP模塊完成數字下變頻功能可以降低功耗,提高速率。

數字下變頻后進行解調,經過解調后的信號為一個比特流序列,比特流處理部分需要完成信息的加密解密、編碼譯碼等。如圖1所示,這部分功能可以用Verilog-HDL語言編寫DSP處理模塊完成,也可以用Matlab的FDATool進行設計后自動生成Verilog-HDL源代碼和PowerPC指令程序;本文采用Verilog-HDL直接編寫DSP模塊的辦法,這樣可以對硬件處理流程進行更好的掌控,并且獲得更高的信號處理性能。由于將DSP模塊嵌入FPGA中,通過增加或減少DSP邏輯電路可以使得設計更加靈活,例如可以將2FSK調制解調,FIR濾波和FFT分別封裝成為單元模塊,編寫地址驅動后PowerPC程序執行時可直接進行調用,相比DSP專用處理器僅調用乘法器和移位寄存器的方法可以節省上百個指令周期,大大提高了實時信號處理的能力,具有在高端領域廣闊的應用前景。

比特流序列處理完成后,可將數據傳入主機磁盤陣列經行儲存,PowerPC通過PCI橋控制本系統和主機的數據傳輸,以滿足未來數據回放和可視化界面要求。

1.2 ADC模數轉換

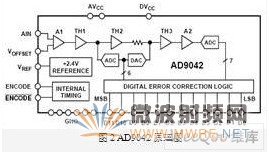

軟件無線電要求ADC,DAC盡可能的靠近天線,這需要很高的ADC的采樣率,采樣精度,動態范圍等特征[11~13]。AD9042是一款高性能高速ADC芯片,采用的是兩級子區式轉換結構,這種設計既保證了所需的轉換精度和轉換速度,又降低了功耗,同時也減小了芯片尺寸,AD9042系統原理如圖2所示[10]。AD9042可以保證的最小采樣率可達41MHZ, 12bit精度,80dB無寄生動態范圍。

1.3 DDS直接頻率合成

由于數字信號處理的處理速度有限,往往難以對A/D采樣得到的高速率數字信號直接進行各種類別的實時處理。為了解決這一矛盾,需要采用數字下變頻技術,將采樣得到的高速率信號變成低速率基帶信號,以便進行下一步的信號處理。數字下變頻技術在軟件無線電和各類數字化接收機中得到了廣泛應用。寬帶數字下變頻器基于外差接收機的原理,包括數字混頻、低通濾波、抽取三個環節[12]。抽取后得到和信號帶寬匹配的基帶抽樣信號,實現從寬頻帶中提取窄帶信號的目的。Xilinx提供的專用DDS(Direct DIGItal Synthesizer) IP模塊用以實現數字下變頻功能。

1.4 CPU控制單元

Virtex-4 FX系列FPGA集成了運行速度高達450 MHz的雙32位嵌入式PowerPC,每個處理器可提供超過700 DhrySTone MIPS的性能,是普通FPGA中處理器性能的三倍。兩個完全集成的UNH認證的10/100/1000 Ethernet MAC進一步提升了Virtex-4 FX處理平臺的性能,從而提高了FPGA資源的可用性。本系統以PowerPC作為該系統的指令處理和控制單元,可以避免純硬件設計復雜,通用性差和不容易協調控制的缺點。PowerPC是本系統SoPC架構的核心組成部分,擔負算法實現和中央控制兩部分任務。Virtex-4 FX內部有大量乘法器可供調用,能夠充分滿足各種數字信號處理要求;PowerPC與前文提到用Verilog-HDL 設計的DSP模塊連接,使整個系統具有實時動態信號的處理能力。PowerPC作為控制器的狀態流程如圖3所示。

2 FSK設計實例及仿真結果

在現代通信中,調制器的載波信號幾乎都是正弦信號,數字基帶信號通過調制器改變正弦載波頻率,產生移頻鍵控(FSK)信號。FSK時域表達式為

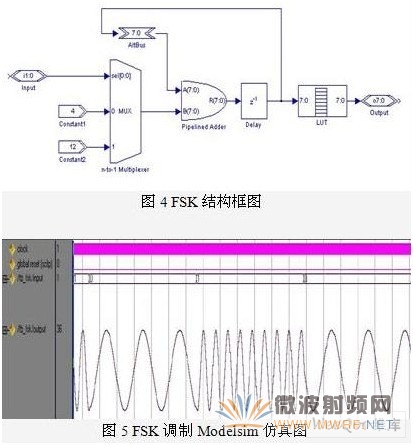

用本系統實現FSK調制結構框圖如圖4所示,用Verilog-HDL語言編寫實現的FSK調制模塊,相對于傳統軟件無線電的實現方式,省去了讀取指令周期的時間,總運算時間縮短了一半。FSK調制的ModelSim波形仿真結果如圖5所示。

3 結 論

改進的基于FPGA的嵌入式軟件無線電系統,可更好地滿足通信、雷達、數字電視等高科技領域對信號處理實時性的要求。運用軟件無線電和SoPC技術,極大的提高了系統動態實時信號的處理能力。在節約資源方面,以節省芯片數量計算,該系統相對于目前常規系統,節省功耗和體積可達30%以上。40MHZ時鐘頻率, 12bit精度,80dB無寄生動態范圍,該系統可以應用于Cellular / PCS基站,多通道多模式接收機,GPS抗干擾接收機,相控陣接收機,頻譜分析,3G無線通信等領域。

粵公網安備 44030902003195號

粵公網安備 44030902003195號