由于不斷追求更高的性能,有效數據窗的單位間隔(UI)繼續縮短。速率為1Gb/s時,UI為1000 ps,5Gb/s縮短為200 ps,10Gb/s則為100 ps。對于100 ps的有效數據窗,當系統沒有連貫而可靠地發送和接收數據之前,可容忍很小的Tj(總抖動)。以上述速度傳輸時,Tj結果需大大小于100ps,而Rj(隨機性抖動)只在1ps的子區間內。有什么技術和工具能用來檢定這些飛秒(fs)系統呢?

基本上來說,隨著速度的提高,高速I/O設計比以往面臨更大挑戰。最新的標準多數要求在物理層的比特誤碼率為10–12。然而,UI的逐漸縮小使保持這樣的誤碼率變得越來越難。到頭來,這就意味著設備級抖動要繼續縮短。例如,5Gb/s的SuperSpeed USB規定Rj為2.42ps RMS;10 Gb/s的SFP規定Tj為28 ps,Rj為1 ps左右。

定時分析

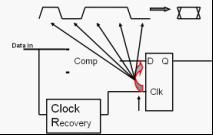

所有采用電壓變換來體現定時情況的電氣系統都伴有討厭的定時抖動。當信號發送速率不斷提高,電壓擺動縮小以降低功耗時,系統的抖動在信號發送間隔中占到相當大的比重。這種情況下,抖動成為基本性能限度。是否具有抖動檢定能力,對成功運用符合性能要求的高速第三代(Gen 3)系統至關重要。如圖1所示,每個時鐘的數據級、上升沿和下降沿都在D處表示出來。數據鎖存是數據通信的關鍵環節。工具(示波器、仿真系統)上,以可見圖形的形式顯示。在每個時鐘上,邊沿的定時位置(如有)有助于時鐘—數據延時統計分布。這種位移即抖動或時間間隔誤差(Time Interval Error or TIE)。

圖1 串行數據 中的抖動

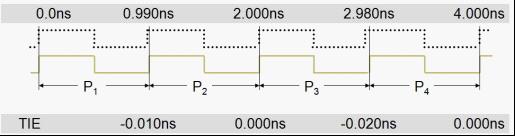

TIE抖動是相對已知或已恢復的時鐘測量出的信號定時誤差。在串行數據的應用中,TIE通常稱為抖動。TIE很重要,因為其甚至能顯示一段時間內少量抖動的累積效應。以圖2為例,每毫微秒時鐘邊沿的TIE標準偏差是9.6 ps。

圖2 TIE抖動測量有其他方法測量單波形抖動,包括周期性抖動和cycle-to-cycle抖動。

周期性抖動是對信號的測量,通常針對從一個邊沿到另一相似邊沿的復示信號。常見的周期測量工具測量某一信號的上升沿到下一上升沿之間的數值。采用數據傳輸方式(如DDR 內存),同時利用上升沿和下降沿來記時數據比特,這時測量周期僅為半個周期。在采集周期測量值的有效樣值后,可分辨標準偏差和峰值。該統計數據即信號中的周期性抖動。

對于cycle-to-cycle抖動,通過應用簡單算術計算剛剛獲取的周期測量值。如果已知兩個相鄰周期的定時數據,其差值便是cycle-to-cycle變化:周期1減去周期2。此外,取周期中的有效示范周期,并測量周期之間的差值后,即可得出標準偏差和峰值。統計出的數據即cycle-to-cycle“抖動”。

抖動分量

將抖動分成各個分量,可提高精度、看清BER性能的根源。最常用的抖動模型基于圖3所示的分級結構。雖然也有分析抖動的其他方法,但這種方法為T11 MJSQ所認可,目前最為常用,因為它直接顯示與BER性能相關的分量。

圖3 按抖動類型進行的抖動分析

在這種分級結構中,首先將總抖動(Tj)分為兩類,即隨機性抖動(Rj)和確定性抖動(Dj),然后再將確定性抖動分為若干類:周期性抖動(Pj,有時也稱正弦波抖動Sj)、占空比抖動(DCD)以及數據相關抖動(DDj,也稱符號間干擾ISI)。有時也采用另外的類別(有界不相關抖動BUj)。

如果要測量在高信號發送速率時構成Tj的各分量,應采用本底噪聲低、頻率響應平穩、抖動測量底限低和觸發抖動小的儀器。例如, ON Semiconductor發現在檢定其高速ECL設備時,需采用系統抖動<200 fs RMS而且帶寬較寬的儀器。芯片設計者發現幾個ps期間的信號移位,甚至是在fs范圍內的移位,也會干擾發送(TX)和接收(RX)性能。

值得注意的是,盡管大多數串行通信標準都對抖動容差或抖動限值做出規定,但標準所采用的技術參數較為模糊,或者在分析抖動時采用了不同的基本原理。標準文件傾向于概述可量化的抖動限值,但并沒有提出多少指導意見來幫助確定在特定應用時哪一種限值更為重要。各種形式的抖動都有可能干擾系統BER,不同的工具在檢測抖動時有不同的優勢。

我們在之前的博文“解答頭號難題:抖動分析設備的選擇,以及足球偏好問題”中分析了各種抖動分析儀,歡迎您與我們分享您的抖動測試經驗,我們將在下回繼續討論。

作者:泰克公司 越測越開心博客團隊

粵公網安備 44030902003195號

粵公網安備 44030902003195號