發送頻率與觸發器以獲得高速同步化之設備,遭遇到些許的問題。針對同步化而言,必須協調多部測量設備的潛在因素與時間不確定性;對于高速測量系統而言更是如此。工程師往往在最初的系統設計時間中忽視這些問題,而限制同步化系統的速度與準確性。在發送頻率與觸發器時的2 個主要問題,即為偏斜(skew) 與抖動(jitter)。

七、取樣頻率同步化

以本質來說,混合信號測試需要在各儀器上采用不同的取樣率,因為模擬波形 I/O 與數字波形 I/O 必須采用不同的取樣率;但是均必須進行同步化。更重要的一點,必須在各儀器上,以正確的取樣頻率邊緣進行數據取樣。

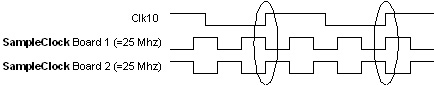

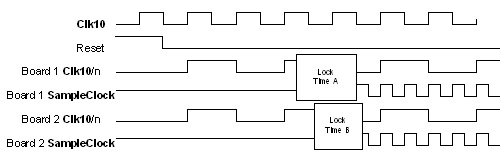

當不同儀器上的取樣頻率均為 10 MHz 參考頻率的整倍數時,所有的儀器都將擁有與其他儀器同步的取樣頻率──所有取樣頻率的提高間距都與 10 MHz 頻率邊緣 (edge) 相符。如圖 6 所示,盡管已鎖定相位為 10 MHz 參考頻率,但當取樣頻率不為整倍數時(如 25 MHz),就不能保證取樣頻率同相 (in phase)。目前使用標準技術來解決這個問題,即同時重新設定所有的 PLL,使得同頻率的取樣頻率變成同相,如圖 7 所示。即使此時所有的取樣頻率皆為同相,但是此解決方法仍然不完全。完全同步化為:從設備到設備的數據時間,位于一個取樣頻率周期中。完全同步化的關鍵在于觸發,將于下文中討論。

圖 6. 未校準之 25 MHz 取樣頻率

圖 7:使用重設使 PLL 同步化

頻率偏斜(skew) 與抖動(jitter)

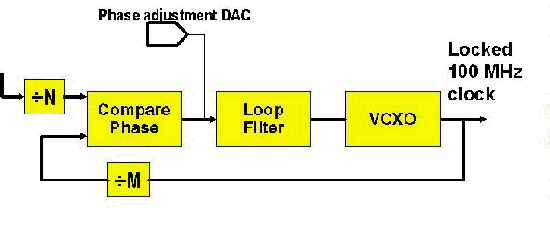

工程師必須仔細規劃取樣頻率與/或參考頻率的發送。舉例來說,一個經同步化的測量系統若要以 200 MS/s 取樣率,于 20 個通道同時進行取樣。則表示要將頻率發送到 10 個雙通道的示波器。如果取樣頻率偏斜 1%,則偏斜不能大于 25 ps。這樣一個系統看起來極具挑戰性。還好,偏斜限制可針對每部測量裝備的偏斜進行校正來解決;可以在取樣數據中,就偏斜部份加以補償。真正的問題是頻率頻率。無論是發送一個 200 MHz 直接取樣頻率或 10 MHz 參考頻率,都會在系統中造成抖動。發送系統的物理性質,在發送頻率的準確性上扮演重要角色;如果頻率的路徑容易受到高頻電子噪音的影響,那么頻率抖動就會成為明顯的問題。針對用于發送高頻取樣頻率的平臺,制造、測試,與校正都變得極為昂貴。因此在許多高頻系統中,普遍會使用較低頻的參考頻率來進行校正。圖 8 是安裝在NI SMC 模塊儀器中的典型 VCXO PLL。回路帶寬維持在最低,以防止來自參考頻率的抖動,同時設備 VCXO 的抖動則低于 1 psrms。這樣的系統可以有效地成為一個低抖動的同步系統。

NI 的 PLL 設計中,有一項非常有用的特性,就是使用一顆相位 DAC。使用相位 DAC 時,可將“VCXO 輸出”和“輸入的參考頻率”進行相位對正。表面上,VCXO 輸出與參考頻率同相;但可能必須將 VCXO 輸出略為偏斜,使輸出的相位稍微偏斜。當送進各設備中的參考頻率因為傳送延遲而有些許偏斜時,則該項功能對于校準多部設備的取樣頻率就非常重要。舉例來說,在 NI PXI-1042 的機架中發送 10 MHz 參考頻率時,插槽至插槽的偏斜最高有 250 ps,最多有 1 psrms 的抖動。雖然 250 ps 的插槽至插槽偏斜對大部份應用而言沒有問題,但可能不適合極高速應用;因為其相位準確度很重要。為了解決這個偏斜問題,相位 DAC 的輸出可加以調整,以校正偏斜。在 NI PXI-5422,200 MS/s取樣率的任意波形發生器,與 NI PXI-5124,200 MS/s 取樣率的示波器中,取樣頻率的相位/延遲調整為 5 ps,因此使用者在同步化多部設備時,可擁有極大的彈性。

圖 8. 具備相位調整 DAC 的 PLL──相位 DAC 使取樣頻率對應于參考頻率的延遲更加有彈性。

觸發器偏斜與扭曲

在解決取樣頻率同步化的問題之后,另外一個主要問題就是發送觸發器以啟動同步作業。觸發器可能來自1 個數字事件,或來自符合觸發條件的模擬信號。一般來說,在多信道系統中,其中1 部設備被設定為主要設備,其余的則指定為從屬設備。在這個情況下,主要設備將發送觸發信號給系統的所有從屬設備(包含其本身)。這里出現的2 個問題為觸發延遲 (delay) 和偏斜 (skew)。從主要設備發送到所有從屬設備時會發生觸發延遲,而每部從屬設備之間會發生扭曲;此現象雖無法避免,但是此種延遲與偏斜均可加以測量,并進行校正。

然而在測量延遲與偏斜時,所面對的挑戰分成兩個階段:

1. 自動測量主要設備和每一部從屬設備之間的觸發延遲,并進行補償。

2. 確保從屬設備之間的偏斜極小,以確保所有設備皆在同樣的頻率范圍內收到觸發器。

將觸發信號發送到多部設備,需要將觸發信號傳送到取樣頻率的頻率范圍中,使觸發器能在正確的時間點上傳送到每一部設備。

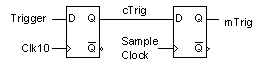

在取樣頻率低于或等于 100 MS/s 時,偏斜會成為觸發器正確發送的主要障礙。舉例來說,若系統內含10 部 200 MS/s 取樣率的設備,每部設備必須在 5ns 的時間范圍內收到觸發。則此限制對于想要提供 100 MHz 以上頻率與同步的平臺造成明顯負擔。觸發信號必須以低于取樣頻率的頻率范圍發送,否則必須建立1 個未經總線的方式來發送觸發器信號(如點對點聯機)。這種平臺的價格過高,并非使用主流。因此必須采用另外一個發送通道:讓觸發器信號使用低頻率范圍,以穩定地發送,并且傳送到高速取樣頻率范圍。理想的選擇之一,即為同步化觸發器信號的發送與 10 MHz 的參考頻率。但是,當取樣頻率并非10 MHz 參考頻率的整倍數時,就無法確保2 組適配卡能于同一個取樣頻率周期中收到觸發器信號。為了說明這一點,假設2 部設備擁有圖 9 所示之簡單回路4,供觸發器從 10 MHz 參考頻率范圍傳送到取樣頻率范圍。

圖 9. 10 MHz 觸發器自參考頻率范圍傳送至取樣頻率范圍

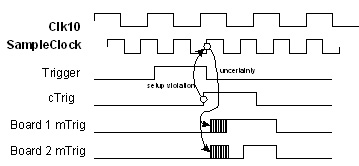

即使設備的取樣頻率相同,以下的頻率圖表顯示在2 部裝置中,無法于相同取樣頻率周期中看到觸發的原因。

圖 10. 亞穩定 (Metastability) 在觸發器上的效果

第一次觸發器的輸出(cTrig) 可能發生在過于接近取樣頻率升高邊緣的地方,導致mTrig 變成亞穩定(metastable) 狀態。當穩定狀態安定下來時,在不同的設備上可能有不同的處理方式,導致將同一個觸發器信號視為發生在不同時間的2 個事件。

八、SMC 模塊儀器與 TClk

2003 年時,NI 以同步化與內存核心(Synchronization and Memory Core,SMC) 為基礎,推出第一代PXI 示波器、任意波形發生器,與數字信號發生器/分析儀。SMC 中使用的關鍵技術之一,就是供頻率與同步應用的T-Clock (TClk) 技術。

TClk

NI 開發1 種同步化的方法,當布署另外的信號頻率范圍時,可啟用取樣頻率校準,與觸發的發送和接收。Tclk 技術的目標包含2 方面:

• TClk 可針對已相位鎖定10 MHz 參考頻率,但卻未校準的取樣頻率進行校準。

• TClk 可正確觸發同步化后的設備。

TClk 同步化即具彈性,而且范圍廣闊;可應用于下列環境中:

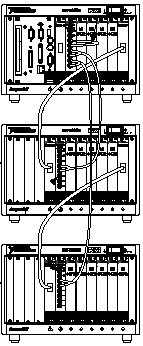

• 使用NI PXI-6653 Slot 2 系統頻率與控制模塊,從單一PXI 機架延伸至多部PXI 機架的同步化,以配合大型通道之用。

• 同質予異質同步化──使用外部或內部取樣頻率,以相同或不同取樣率運作的設備。

• TClk 同步化可以運用在模式一與模式二中,如上文所描述。

圖 11. 使用 NI PXI-6653 系統頻率與控制模塊進行多機架同步化;由主控機架發送 10 MHz 參考頻率至所有的從屬機架。NI MXI-4 可控制所有的從屬機架。

TClk 同步化的目的,是讓設備能夠同時對觸發器響應。“同時”指在同取樣時段中,而且盡可能校準其取樣頻率。達成 TClk 同步化的方式,是讓每一部設備根據取樣頻率產生一個觸發頻率 (TClk)。觸發器與 Tclk 脈沖進行同步化。從外部來源接收的觸發器,或是在內部自行產生的設備,將于 TClk 的負緣 (falling edge) 上傳送信號至所有設備(包含本身)。TClk 頻率低于取樣頻率與 PXI 的 10 MHz 參考頻率,以配合 NI PXI-1045 的18 槽機架(從插槽 1 至插槽 18 之間的傳播延遲,可能會延長至數個毫微秒)。如果應用程序呼叫多部機架時,傳播延遲高于一般正常機架間的延遲,則可設定 TClk 頻率。

此時即出現“實時”數據采集的問題;如果符合觸發器條件,而且必須觸發 10 部示波器,那么由于觸發器對 TClk 的同步化操作,潛在的問題就會浮現。處理這個問題的方法,是使用設備樣本內存緩沖區中的觸發前樣本與觸發后樣本。所有的 TClk 設備,均能接受因觸發器對 TClk 進行同步化而造成的時間延遲。舉例來說,將10 部示波器設定為同時采集 10,000 個樣本。取樣率為 200 MS/s (取樣時間5 ns),而引用之 TClk 頻率則設定為 5 MHz (取樣時間200 ns)。這表示因 TClk 對觸發器同步化所導致的采集延遲,可能高達 40 個樣本。TClk 設備的設計會自動填補內存緩沖區,以補償觸發事件和開始采集之間的延遲,而 NI-TClk 驅動程序軟件會自動調整所有示波器上的時間標記,以反應開始采集與觸發事件之間的時間關系。

粵公網安備 44030902003195號

粵公網安備 44030902003195號