在整合設計與測試實例的第二個趨勢,就是利用EDA所產生的行為模型,加速開發產品檢驗/認證,并製作測試軟件。在此之前,讓產品設計程序效率低落的塬因之一,就是特定產品的測試程序代碼開發緩慢,甚至要等到首次測試實體塬型之后。不論是特性描述或生產測試程序代碼,若要能加快開發程序,最好通過軟件製作既定設計的塬型并直接做為DUT。通過此方式,工程師將可以于產品設計期間同時,開發特性描述與生產測試軟件,進而加速上市時間。

以美敦力(Medtronic)為例,該公司最近就針對心率調節器開發而選用此設計方式。美敦力通過特殊設計的新軟件套件銜接EDA環境與測量軟件,連接軟件環境之后,工程師可于製作實際硬件之前就開發出測試工作臺,而通過此設計方式而達到的平行機制,讓工程師能因此加速產品上市時間。

在提升工程設計完整度的過程中,整合“設計實例”與“測試實例”的重要度將越來越被突顯。由于EDA與測量軟件間越來越緊密,工程師將能于未來數年之內更有效利用EDA軟件,以取得更完整的模擬作業,并讓EDA模擬功能強化檢驗與生產測試的程序。

FPGA啟動下世代測量儀器革命

過去20多年來,“微處理器架構、可由使用者設計程式的測量演算法”已成主流概念,讓測試系統可迅速接受不斷變動的客製化測試需求。此方法亦即所謂的虛擬儀控,且供應商亦繼續設法設計其他儀器優勢--更高效能、提高客製化程度、更廣泛采用現成技術、降低測試系統成本等。

如果說微處理器帶動虛擬儀控的革命,那么現場可編程閘陣列(FPGA)就又啟動了下個階段。FPGA用于儀器之中已有數年,舉例來說,目前高頻寬示波器雖可蒐集大量資料,但使用者并無法迅速分析所有資料。這些裝置上的硬件定義演算法一般均建置于FPGA,以執行資料分析與縮減(平均、觸發、波形數學)、運算統計(平均值、標準差、最大值、最小值)、處理資料以利顯示,最后為使用者呈現有意義的結果。這些功能雖然確有其價值,但卻無法突顯FPGA潛在功能,在大部分條件下,使用者并無法將客製化測量演算法部署至FPGA。

測量硬件上的開放式FPGA,可為僅有處理器的系統提供多項優勢。基于FPGA的強大運算功能,將可達到更高的測試傳輸率與更廣的測試範圍,進而縮短測試時間并降低投資成本。微處理器所無法達到的測試作業,亦可通過FPGA的低延遲特性而建置。FPGA既有的平行機制,可達到真正的多執行序測試,甚至超越多核心處理器。在即時測試的硬件排序與待測物控制程序中,FPGA更扮演關鍵角色。

由產業研究公司Frost & Sullivan所發表的2011年模組化儀控市場研究指出,由Altera與賽靈思(Xilinx)等公司對FPGA功能的提升,將對測試與測量應用影響深遠,對需要高精確度與快速處理功能的客戶而言尤為如此,目前市場上有越來越多的開放式FPGA產品。

雖然市面上已有許多硬件可供選擇,但大多數的測量演算法都是針對虛擬儀控的微處理器部分所開發。基于資料形態、程式設計模型、特定硬件屬性(如時序限制) 等的不同,并無法簡單移至FPGA繼續使用。廠商要開發專業且穩定的FPGA測量硅智財(IP)須具備專業知識并耗上大量時間,因此,目前儀控硬件中的大多數FPGA僅使用供應商定義的固定演算法,無法由使用者自行設計程式。

2011年業界就已經開始討論異質運算(Heterogeneous Computing),意即將演算法分配至多種運算架構(中央處理器(CPU)、圖形處理器(GPU)、FPGA、云端系統)中,找出最佳的演算法建構資源。除硬件架構本身的強大功能考量之外,異質運算代表各種系統的程式設計難題,且測量演算法難以在系統之間“攜帶”,復雜度確實有所影響。

業界最近針對測試工程領導廠商的全球調查指出,約有54%受訪者認為未來技術發展將可提升測試傳輸率并降低系統成本,進而縮短開發時間。為克服此難題,產業界正積極開發相關工具,以期能跨硬件系統使用演算法,并且讓FPGA可普及于測試系統。

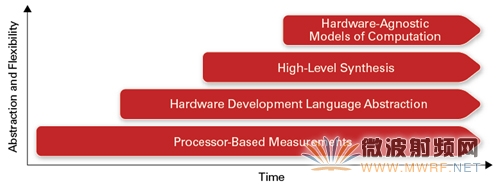

此種跨硬件的系統將可提供硬件描述語言(HDL)抽象化。HDL是以文字方式描述邏輯閘層(Gate)與訊號層(Signal-level)的行為,而HDL抽象化(Abstraction)工具則通過圖形或簡圖的呈現方式,擷取更高層級的設計(圖3)。與HDL相較,雖然這些工具確實降低FPGA技術的門檻,但仍無法完全省略某些FPGA設計的特定硬件屬性,如資源分配、數位訊號處理器(DSP)分割架構、管線流通(Pipelining)、內建記憶體(On-chip Memory)等。在這些情況下,仍須重新設計/檢驗演算法才能銜接FPGA,也促成開發工具的未來發展。

圖3 開發軟件必須能跨執行系統,而達到更高的硬件抽象化與靈活度,以達更高效能、更高成本效益,且更能迅速上市。

挾多重優勢 開放式FPGA普及于測量系統

高階合成(High-level Synthesis,HLS)工具可于較高階層擷取演算法,并為既有建置獨立分配其效能屬性,如延遲、時脈率、傳輸率、資源利用等。由于特殊建置并不屬于演算法定義,如此也降低演算法的可攜性。此外,開發工程師在設計硬件特性(管線流通、資源仲裁等)時,并不須顧慮特定硬件。HLS的概念已存在超過20年,但市面上的工具是最近才漸趨成熟。這些工具確實提供相關優勢,但僅針對FPGA或特定應用積體電路(ASIC),并未納入如GPU與微處理器的其他運算平臺。為突破這些HLS工具的限制,業界提供測試版軟件,整合既有的LabVIEW資料流程式圖與HLS優點,以因應FPGA設計作業。如此一來,建置FPGA亦可納入大量LabVIEW測量與控制演算法,而不受制于微處理器的執行情況,亦不須針對FPGA部署作業而重新設計大量演算法。此軟件目前仍在測試中而無法普及,但最后的目標結果可期。

創新開發工具的最后一步,就是讓跨硬件系統整合運算/設計的多種模型。這些運算模型包含LabVIEW資料流程式圖、DSP簡圖可用于RF與通訊應用中的多重速率訊號處理、文字式數學可擷取類教科書的方程式、狀態機器用于數位邏輯與協定等。

舉例來說,如賽靈思Zynq可延伸處理平臺所建構的系統單芯片(SoC)系統,未來將整合雙核心安謀國際(ARM)微處理器與FPGA。此芯片具備極高的異質運算潛力,但由于微處理器與FPGA分別需要不同的運算語言/模型,所以程式設計作業的難度極高。在理想狀態下,工程師應擁有多樣的運算模型以支援所有系統,并以更有效的方式擷取演算法,最后部署至最佳執行系統。根據業務需求的不同,這裡的“最佳”可能代表最高效能、最高成本效益,或最短上市時間。若要讓工具搭配非特定硬件的運算模型,仍有一段開發的路要走,而且必須能滿足目前測試系統的開發需求。

開發軟件必須能跨執行系統,而達到更高的硬件抽象化與靈活度,以達更高效能、更高成本效益,且更能迅速上市。

雖然非特定硬件的測量演算法與高階合成工具尚未晉升主流,但開放式FPGA正逐漸普及于自動化測試系統中。FPGA在測試作業中的優勢,已值得許多廠商投入更多開發資本,而且只要提升軟件工具,將連帶縮短開發時間并降低復雜度,促成更多相關應用。如同微處理器與相關 的軟件開發環境/測量演算法,帶動了虛擬儀控的革命,使用者可設計的FPGA亦將帶動圖形化系統設計(GSD)的下一波革新,催生未來的測試系統。

來源:NI公司

粵公網安備 44030902003195號

粵公網安備 44030902003195號