導語

在低頻時,一段普通導線就可以有效地將兩個電路短接在一起,但是在高頻時候就不同了。在高頻電路中,一個小小的過孔、連接器就會對信號產生很大的影響。為了分析高速信號,引入了一個新的模型——傳輸線。理想傳輸線的兩個主要特征就是時延和阻抗。如果電路中傳輸線的阻抗突變會導致信號的反射,使得信號質量產生較大的影響,這篇文章主要介紹這方面的信息。

1、集總參數和分布參數

在信號速率比較低的時候,我們通常會把電路等效成電阻、電容以及電感進行分析,這就是我們常說的集總參數電路,和集總參數電路對應的叫做分布參數電路。

集總參數電路和我們中學物理里面的“質點”的概念類似,我們在分析它們的時候可以不考慮自身的大小,而分布參數電路則需要考慮它們自身尺寸對信號的影響。

集總參數和分布參數的區分并沒有完全明確的定義,一般我們認為:

滿足信號的波長λ>> 器件的尺寸d的時候,我們可以把電路當作是集總參數電路。

不滿足信號的波長λ>> 器件的尺寸d的時候,我們可以把電路當作是分布參數電路。

在Howard.Johnson的《高速數字設計》中給出了這樣的定義——“如果連線長度小于上升沿有效長度的1/6,則該電路主要表現為一個集總系統的特征”。不過這里的1/6也是個經驗參數,也有的作者采用的的是1/4或者 。

。

舉一個例子吧,對于我們常用到的51單片機,它們的IO口進行一次數據切換的時間大概在1µs,對應的基波波長約為300m(我們可以近似認為信號在PCB上的傳播速度為光速的一半),我們的電路板以及cable的長度一般不會超過3m,和信號的波長比起來尺寸可以忽略不計,所以對于單片機這個級別的系統,我們可以認為它是集總系統。

對于一個速率為480Mbps的USB2.0信號,上升時間大約在0.6ns左右,在上升時間內在PCB上能夠傳輸的距離約為9cm,當器件或者走線的尺寸超過1.5cm的時候,我們就必須考慮它們本身大小對信號帶來的影響。

我們使用的USB線就屬于分布參數電路,我們一般稱之為“傳輸線”。

2、理想傳輸線

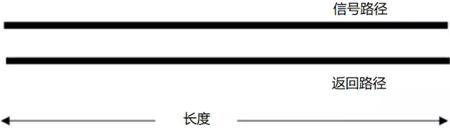

傳輸線就指的是有長度的兩根導線,如下圖所示;所謂的有長度,就是指我們無法忽略導線長度對信號帶來的影響。

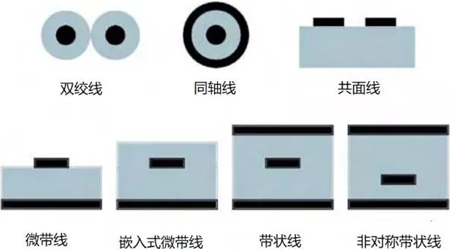

常見的傳輸線有以下幾種:

雙絞線,我們平時用的RJ45口的網線就屬于雙絞線

同軸線,常見的射頻電纜一般都屬于同軸線,如BNC線

微帶線,一般的PCB表層高速走線都是屬于微帶線

帶狀線,一般的PCB內層高速走線都是屬于帶狀線。

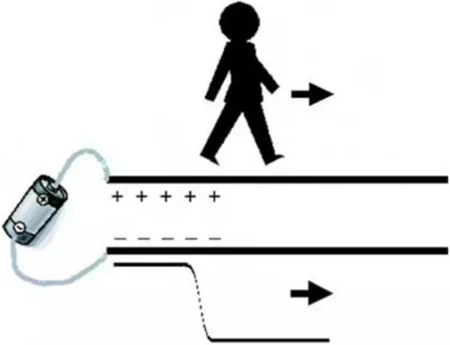

假設有一段足夠長的導線,我們把自己當作一個快速上升沿信號,在以15cm/ns的速度穿過這段導線,因為傳輸線本身可以看作是一個大的電容,信號在經過這段傳輸線的時候會感受到瞬時電抗的存在。通常把這個感受到的電抗叫做傳輸線在某個位置的瞬時阻抗,如果在某個位置的電容偏大的話,這個位置的瞬時阻抗也就越小。

如果這條傳輸線是一條均勻的傳輸線,它在每一個位置的瞬時阻抗都是相同的,我們把這個固定的阻抗值叫做傳輸線的特征阻抗,關于傳輸線的更多內容,可以參考Eric.Bogatin的著作《信號完整性分析》第7章。

我們經常提到的100Ω差分線,其實指的就是這對差分傳輸線的特征阻抗是100Ω。對于理想傳輸線而言,它有兩個重要的參數:一個是時延,另一個就是它的特征阻抗。

3、傳輸線的反射

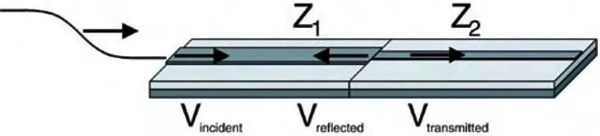

信號在傳輸的過程中如果遇到阻抗突變,就會產生反射,反射電壓的大小和入射電壓以及傳輸線的阻抗有關,如下圖所示,假設傳輸線第一個區域的瞬時阻抗為Z1,第二個區域的瞬時阻抗為Z2。

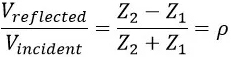

那么反射電壓Vreflected和入射電壓Vincident滿足以下關系:

其中,ρ是我們所關心的反射系數,即反射電壓與入射電壓的比值,當信號從高阻抗區域進入低阻抗區域時,反射系數的值是負的,當信號從低阻抗區域進入高阻抗區域時,反射系數是正的。反射系數的取值范圍是[-1,1]。

相應的,傳導系數t滿足以下關系:

因為傳輸線本身有長度,也有瞬時阻抗,如果傳輸線上有多個點的阻抗不連續,可能會導致多次反射。

4、傳輸線的多次反射

傳輸線的反射是很多信號完整性問題的根源,我們見到的很多現象,例如振鈴、回溝以及“花生眼”等現象都是由于信號在鏈路中多次反射造成的。

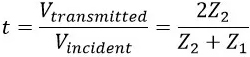

下圖是一個振鈴現象產生的示例,信號源的內阻為10Ω,往外發送一個上升時間為1ns、幅值為1V的階躍信號,經過一段15cm的50Ω傳輸線,在傳輸線末端開路測量。很容易得到,在傳輸線兩側的反射系數分別為-0.667和1,傳輸線末端的信號幅值如下所示。

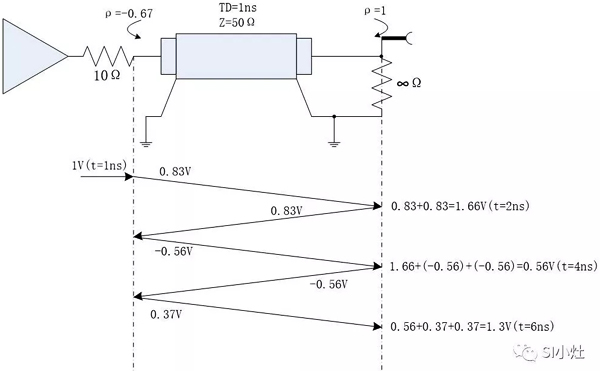

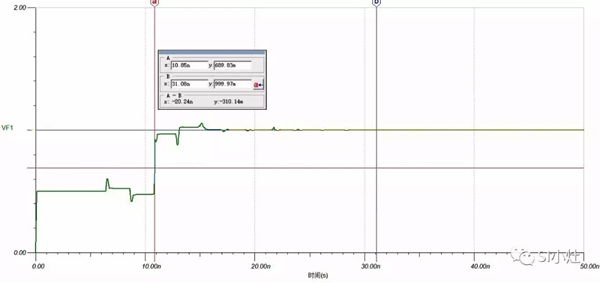

下圖是使用TI-TINA仿真得到的結果,和我們上面推算的結果一致,這個就是我們在測試的時候經常能夠見到的振鈴現象。

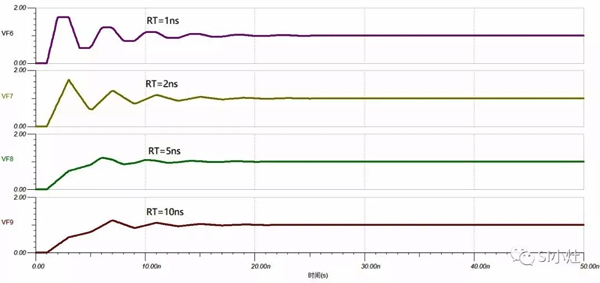

當我們改變輸入信號的上升時間,從1ns到10ns,傳輸線末端的信號如下圖所示。從圖中我們可以得知,信號上升時間越緩,受到反射的影響越小。當阻抗不連續點的時延小于信號上升時間的1/5的時候,對信號的影響較小。

大家看到這個1/5,是不是想到了些什么?我們在文章的一開始說過,當器件的尺寸小于信號上升時間的1/6(也有的說是1/4)的時候,我們可以忽略器件的自身大小。既然傳輸線本身的時延可以忽略,那么也就不會存在多次反射了。關于傳輸線反射的更多內容,可以參考Eric.Bogation的著作《信號完整性分析》第8章內容。

在高速信號的layout中,我們有時候會碰到一些不可避免的阻抗不連續點,例如過孔、連接器以及芯片的封裝。如果這些不連續點的自身尺寸較小,而信號的速率又不是特別高的情況下,阻抗不連續造成的影響會比較小。

5、阻抗測量

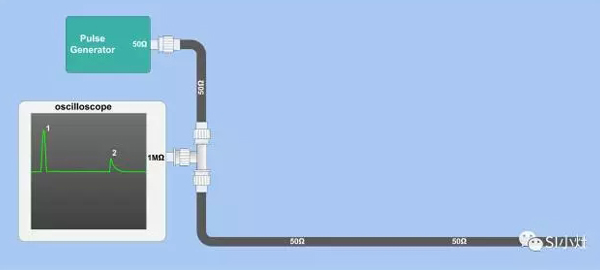

測量傳輸線的阻抗需要用到TDR,TDR(Time Domain Reflectometer),TDR的示意圖如下圖所示,它是由一個高速階躍信號發生器和采樣示波器組成,其中信號發生器的內阻是精確的50Ω。信號發生器可以產生上升時間在100ps以內的快速階躍信號。

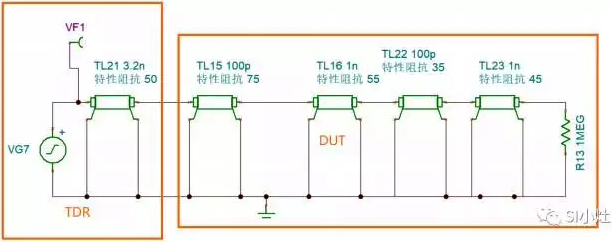

下圖是使用TINA搭建的模型,其中左側是TDR和一段約50cm長的線纜,右側是一段阻抗不連續的一段傳輸線,信號源的上升時間為100ps,幅值為1V。

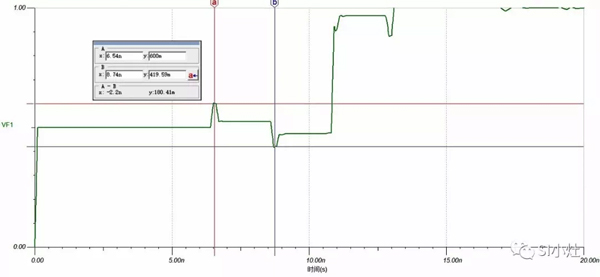

在VF1處測量到的電壓信號如下圖所示,由于DUT存在阻抗不連續,所以能夠測量到變化的反射電壓,DUT的末端是開路的,在末端的反射系數為1,所以被測件末端的電壓會迅速提升到原來的兩倍。

下圖的a點對應的是DUT第一個阻抗為75Ω的位置,瞬時阻抗增大,反射系數ρ取正值,所以測量到的電壓會增大,a點對應的時間約為6.4ns,是前面那段導線電延時的兩倍;同理,b點對應的是上圖中瞬時阻抗為35Ω的位置,在這個位置反射系數ρ為負值,所以對應位置電壓減小,a點和b點之間的時間差為2.2ns,正好是這兩點間電延時的兩倍。

將時基擴大到10ns/div,能夠看到信號在DUT末端的多次反射,但是由于末端是開路的,所以在達到穩態時的電壓VF1(∞)=VG7(∞)=1V。

在實際測量中,TDR顯示的縱軸不再是電壓值,可以直接轉換成阻抗,所以我們可以直接在TDR上查看阻抗的大小,下圖是LeCroy公司SPARQ工具測量到的阻抗。

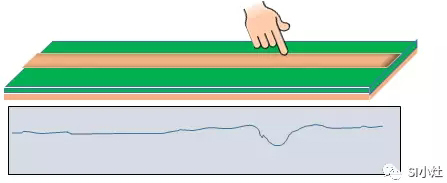

在使用TDR對微帶傳輸線進行測量的時候,大家可以嘗試一下用手輕觸PCB走線,可以看到如下圖所示的阻抗變化,TDR測量的阻抗曲線在某個位置阻抗突然減小,這是因為人的身體是導體,當手指接觸到表層的PCB走線的時候,接觸位置的等效并聯了一個電容,使得容性增加,阻抗降低。

我們也可以利用這個方法去尋找微帶傳輸線上阻抗不連續點在PCB的位置,用我們的人體去輔助定位。

TDR可以很好的測量無緣鏈路的互聯設計,但是有時候TDR的測試結果也未必是“真實”的,告訴示波器測量到的結果有時候會更可靠,下面給大家舉一個實例,這個也是我工作的時候遇到的第一個信號完整新方面的問題。

6、實例分析

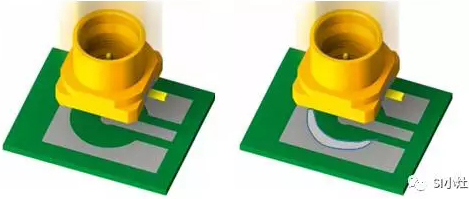

參加工作后測試的第一個項目是某3Gbps SerDes項目,EVB上采用的是SMP接口。可能是Layout的同事用錯SMP接口的PCB封裝了,SMP接口中多出了一圈額外的覆銅,參考下圖右側。多余的覆銅導致SMP接口處的電容變大,瞬時阻抗降低。

經過實測,SMP接口處的單端阻抗下降到了約30Ω,和50Ω的設計值相比,達到了40%偏差。我們當時還在想著信號質量一定會受到比較嚴重的影響,甚至有可能導致眼圖閉合、產生大量誤碼。結果實際上,眼圖和抖動并沒有產生明顯的惡化。

這是為什么呢?

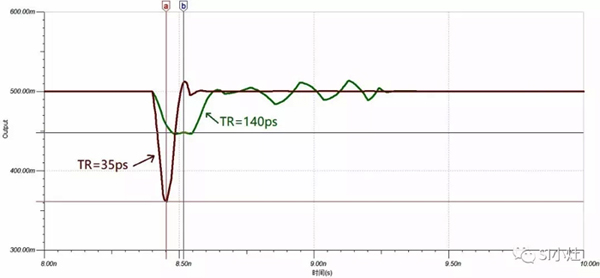

我們當時用來測試的TDR設備,上升時間是固定的35ps,而且不可調節。而35ps是一個非常快速地上升沿,10Gbps以上的信號在近端才會有這么快的上升沿,我們測試的信號速率是3.125Gbps,而且到SMP接口時已經經過了一段走線,所以實際信號的上升時間遠大于35ps,我們使用TDR測量到的阻抗對于我們的被測信號來說是一個過于嚴苛的結果。

下圖是使用TINA仿真出來的結果,當我們設置階躍信號的上升時間為35ps的時候,反射更加嚴重,對應測量的瞬時阻抗也就越低,當階躍信號上升沿為140ps的時候,明顯有所改善。

從這個例子,我們可以看出來,如果測試條件不正確的話,有些測試得到的“真實數據”反而是不可靠的。在對高速信號進行分析的時候,一方面,我們需要從信號的角度去觀察問題;另一方面,我們需要從多個角度進行測量和分析,這樣才能夠得到更可靠的結果。

對于高速系統,阻抗測量結果配合高速示波器測量到的結果往往會更加真實可靠。

7、Reference

Eric. Bogatin 《信號完整性分析》

Howard. Johnson 《高速數字設計》

本文使用的仿真工具是TINA,TINA是德州儀器(TI)公司提供的一款模擬電路仿真軟件,可以在TI官網上免費下載。

粵公網安備 44030902003195號

粵公網安備 44030902003195號